Микрокоманды

Для управления трактом данных, изображенным на рис. 4.1, нам нужно 29 сигналов Их можно разделить на пять функциональных групп

-

9 сигналов для записи данных из шины С в регистры.

-

9 сигналов для разрешения передачи регистров на шину В и в АЛУ.

-

8 сигналов для управления АЛУ и схемой сдвига.

-

2 сигнала, которые указывают, что нужно осуществить чтение или запись через регистры MAR/MDR (на рисунке они не показаны)

-

1 сигнал, который указывает, что нужно осуществить вызов из памяти через регистры PC/MBR (на рисунке также не показан).

Значения этих 29 сигналов управления определяют операции для одного цикла тракта данных. Цикл состоит из передачи значений регистров на шину В, прохождения этих сигналов через АЛУ и схему сдвига, передачи полученных результатов на шину С и записи их в нужный регистр (регистры). Кроме того, если установлен сигнал считывания данных, то в конце цикла после загрузки регистра MAR начинается работа памяти. Данные из памяти помещаются в MBR или MDR в конце следующего цикла, а использоваться эти данные могут в цикле, который идет после него. Другими словами, если считывание из памяти через любой из портов начинается в конце цикла к, то полученные данные еще не могут использоваться в цикле к+1 (ТОЛЬКО В цикле к+2 и позже).

Этот процесс объясняется на рис. 4.2. Сигналы управления памятью выдаются только после загрузки регистров MAR и PC, которая происходит на нарастающем фронте синхронизирующего сигнала незадолго до конца цикла 1. Мы предположим, что память помещает результаты на шину памяти в течение одного цикла, поэтому регистры MBR и (или) MDR могут загружаться на следующем нарастающем фронте вместе с другими регистрами.

Другими словами, мы загружаем регистр MAR в конце цикла тракта данных и запускаем память сразу после этого. Следовательно, мы не можем ожидать, что результаты считывания будут в регистре MDR в начале следующего цикла, особенно если длительность импульса небольшая. Этого времени будет недостаточно. Поэтому между началом считывания из памяти и использованием этого результата должен помещаться один цикл. Однако во время этого цикла может выполняться не только передача слова из памяти, но и другие операции. Предположение о том, что работа памяти занимает один цикл, эквивалентно предположению, что количество успешных обращений в кэш-память составляет 100%. Подобное предположение никогда не может быть истинным.

Так как регистры MBR и MDR загружаются на нарастающем фронте синхронизирующего сигнала вместе с другими регистрами, они могут считывать во время циклов, в течение которых осуществляется передача нового слова из памяти. Они возвращают старые значения, поскольку прошло еще недостаточно времени для того, чтобы поменять их на новые. Здесь нет никакой двусмысленности: до тех пор пока новые значения не загрузятся в регистры MBR и MDR на нарастающем фронте сигнала, предыдущие значения находятся там и могут использоваться.

Выходной сигнал шины С можно записывать сразу в несколько регистров, однако нежелательно передавать значения более одного регистра на шину В. Немного расширив схемотехнику, мы можем сократить количество битов, необходимых для выбора одного из возможных источников для запуска шины В. Существует только 9 входных регистров, которые могут запустить шину В (регистры MBR со знаком и без знака учитываются отдельно) Следовательно, мы можем закодировать информацию для шины В в 4 бита и использовать декодер для порождения 16 сигналов управления, 7 из которых не нужны.

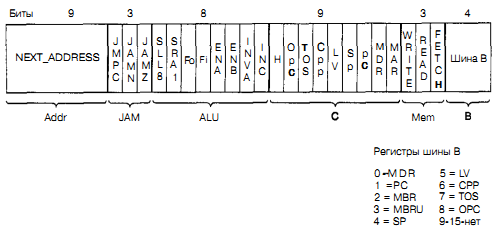

Рис. 4.4. Формат микрокоманды для Mic-1

Теперь мы можем управлять трактом данных с помощью 9+4+8+2+1=24 сигналов, следовательно, нам требуется 24 бита. Однако эти 24 бита управляют трактом данных только в течение одного цикла. Задача управления — определить, что нужно делать в следующем цикле. Чтобы включить это в разработку контроллера, мы создадим формат для описания операций, которые нужно выполнить, используя 24 бита управления и два дополнительных поля поле NEXT_ADDRESS (следующий адрес) и поле JAM (определяет, как выбирается следующая микрокоманда.).

Управление микрокомандами: Mic-1

До сих пор мы рассказывали о том, как происходит управление трактом данных, но мы еще не касались того, каким образом решается, какой именно сигнал управления и на каком цикле должен запускаться. Для этого существует контроллер последовательности, который отвечает за последовательность операций, необходимых для выполнения одной команды.

Контроллер последовательности в каждом цикле должен выдавать следующую информацию:

1. Состояние каждого сигнала управления в системе.

2. Адрес микрокоманды, которая будет выполняться следующей.

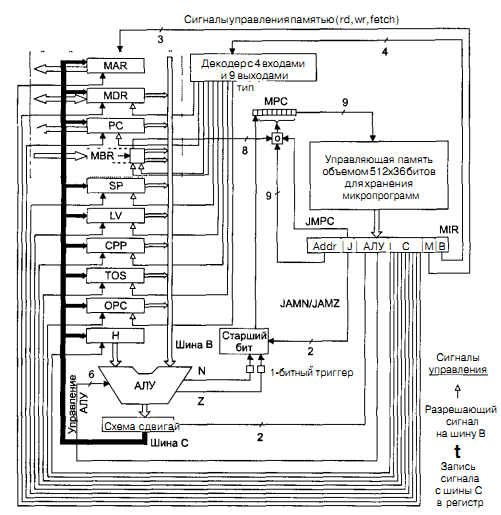

Рисунок 4.5 представляет собой подробную диаграмму полной микроархитектуры рассматриваемой машины, которую мы назовем Mic-1.

Диаграмма состоит из двух частей: тракта данных (слева), который мы уже подробно обсудили, и блока управления (справа), который мы рассмотрим сейчас. Самой большой и самой важной частью блока управления является управляющая память. Удобно рассматривать ее как память, в которой хранится полная микропрограмма, хотя иногда она реализуется в виде набора логических вентилей. Мы будем называть ее управляющей памятью, чтобы не путать с основной памятью, доступ к которой осуществляется через регистры MBR и MDR. Функционально управляющая память представляет собой память, которая содержит микрокоманды вместо обычных команд. В нашем примере она содержит 512 слов, каждое из которых состоит из одной 32-битной микрокоманды с форматом, изображенным на рис. 4.4. В действительности не все эти слова нужны, но по ряду причин намтребуются адреса для 512 отдельных слов.

Управляющая память отличается от основной памяти тем, что команды, хранящиеся в основной памяти, выполняются в порядке адресов (за исключением ветвлений), а микрокоманды — нет. Увеличение счетчика команд в листинге 2.1 означает, что команда, которая будет выполняться после текущей, — это команда, которая идет вслед за текущей в памяти. Микропрограммы должны обладать большей гибкостью (поскольку последовательности микрокоманд обычно короткие), поэтому они не обладают этим свойством. Вместо этого каждая микрокоманда сама указывает на следующую микрокоманду.

Поскольку управляющая память функционально представляет собой ПЗУ, ей нужен собственный адресный регистр и собственный регистр данных. Ей не требуются сигналы чтения и записи, поскольку здесь постоянно происходит процесс считывания. Мы назовем адресный регистр управляющей памяти МРС (Microprogram Counter — микропрограммный счетчик). Название не очень подходящее, поскольку микропрограммы не упорядочены явным образом и понятие счетчика тут неуместно, но мы не можем пойти против традиций. Регистр данных мы назовем MIR (Microinstruction Register — регистр микрокоманд). Он содержит текущую микрокоманду, биты которой запускают сигналы управления, влияющие на работу тракта данных.

Рис. 4.5. Полная диаграмма микроархитектуры Mic-1

Регистр MIR, изображенный на рис 4 5, содержит те же шесть групп сигналов, которые показаны на рис 4.4. Группы Addr и J (то же, что JAM) контролируют выбор следующей микрокоманды. Мы обсудим их чуть позже Группа ALU содержит 8 битов, которые выбирают функцию АЛУ и запускают схему сдвига. Биты С загружают отдельные регистры из шины С. Сигналы М управляют работой памяти. Наконец, последние 4 бита запускают декодер, который определяет, значение какого регистра будет передано на шину В. В данном случае мы выбрали декодер, который содержит 4 входа и 16 выходов, хотя имеется всего 9 разных регистров. В более проработанной модели мог бы использоваться декодер, имеющий 4 входа и 9 выходов.