- •Тема 7. Архітектурні особливості мікропроцесорів Intel 80x86.

- •1. Реальний і захищений режими роботи процесора.

- •Мал. 3.1 Схема визначення фізичної адреси для процесора 8086.

- •2. Нові системні регістри мікропроцесорів і80x86.

- •Мал. 7.2 Основні системні регістри мікропроцесорів і80x86.

- •3. Підтримка сегментного способу організації віртуальної пам'яті.

- •Мал. 7.3 Дескриптор сегменту.

- •Мал. 7.4. Селектор сегменту.

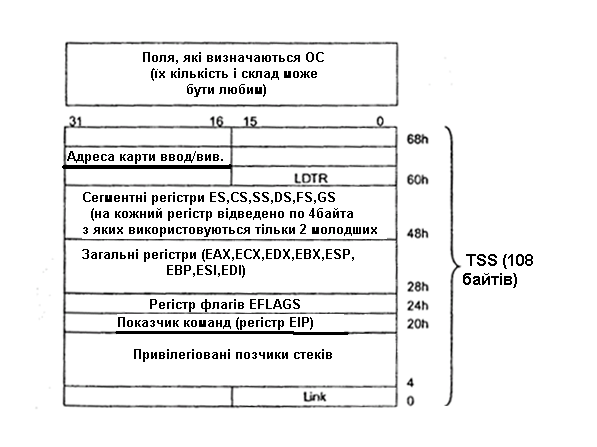

- •Мал. 7.5 Сегмент стану задачі (tss).

- •Мал. 7.6 Процес отримання лінійної адреси команди.

- •4. Підтримка сторінкового способу організації віртуальної пам'яті.

- •Мал. 7.7 Дескриптор сторінки.

- •Мал. 7.8 Трансляція лінійної адреси в мікропроцесорах і80x86.

- •5. Режим віртуальних машин для виконання додатків реального режиму.

- •6. Захист адресного простору задач.

- •Рівні привілеїв для захисту адресного простору задач.

- •Якщо цільовий сегмент є сегментом стека, то правило перевірки має вид

- •7. Механізм шлюзів для передачі керування на сегменти коду з іншими рівнями привілеїв.

- •Мал. 7.9 Механізм шлюзів для переходу на другий рівень привілеїв.

- •Мал. 7.10 Перехід на сегмент більш привілейованого коду.

- •Мал. 7.11 Формат дескриптора шлюзу.

Мал. 7.4. Селектор сегменту.

Для маніпулювання задачами ОС має інформаційну структуру, що ми уже визначили як дескриптор задачі. Мікропроцесор підтримує роботу з найбільш важливою частиною дескриптора задачі, що найменше залежить від операційної системи. Ця інваріантна частина дескриптора, з яким і працює мікропроцесор, названа сегментом стану задачі (task state segment, TSS). Перелік полів TSS зображений на мал. 3.5. Видно, що в основному цей сегмент містить контекст задачі. Процесор одержує доступ до цієї структури за допомогою регістра задачі (task register, TR).

Регістр TR містить індекс (селектор) елемента в GDT. Цей елемент являє собою дескриптор сегмента TSS. Дескриптор заноситься в тіньову частину регістра (див. мал. 3.2). До розгляду TSS ми ще повернемося, а зараз помітимо, що в одному з полів TSS міститься покажчик (селектор) на локальну таблицю дескрипторів даної задачі. При переході процесора з однієї задачі на іншу вміст поля LDTR заноситься мікропроцесором в однойменний регістр. Ініціалізувати регістр TR можна і явно.

Отже, регістр LDTR містить селектор, що вказує на один з дескрипторів глобальної таблиці GDT. Цей дескриптор заноситься мікропроцесором у тіньову частину регістра LDTR і описує таблицю LDT для поточної задачі. Тепер, коли в нас визначені як глобальна, так і локальна таблиця дескрипторів, можна розглянути процес визначення лінійної адреси. Для прикладу розглянемо процес одержання адреси команди. Адреси операндів визначаються за аналогією, але задіяні будуть інші регістри.

Мікропроцесор аналізує біт TI селектора коду й у залежності від його значення, витягає з таблиці GDT чи LDT дескриптор сегмента коду з номером (індексом), що рівний полю index (біти 3-15 селектора, див. мал. З.4). Цей дескриптор заноситься в тіньову (сховану) частину регістра CS. Далі мікропроцесор порівнює значення регістра EIP (extended instruction pointer — покажчик інструкції команди) з полем розміру сегмента, що міститься у взятому дескрипторі, і якщо зсув відносно початку сегмента не перевищує розміру межі, то значення EIP додається до значення поля початку сегмента і ми одержуємо шукану лінійну адресу команди. Лінійна адреса - це одна з форм віртуальної адреси. Вихідна двійкова віртуальна адреса, що обчислюється відповідно до використовуваної адресації, перетвориться в лінійну. В свою чергу, лінійна адреса буде дорівнювати або фізичному (якщо сторінкове перетворення відключене), або за допомогою сторінкової трансляції перетвориться у фізичну адресу. Якщо ж зсув з регістра EIP перевищує розмір сегмента коду, то ця аварійна ситуація викликає переривання і керування повинне передаватися супервізору ОС.

Мал. 7.5 Сегмент стану задачі (tss).

Розглянутий нами процес одержання лінійної адреси проілюстрований на мал. 3.6. Варто відзначити, що оскільки міжсегментні переходи відбуваються нечасто, то, як правило, визначення лінійної адреси полягає тільки в порівнянні значення EIP з полем межі сегмента та у додаванні зсуву до початку сегмента. Усі необхідні дані вже знаходяться в мікропроцесорі, і операція одержання лінійної адреси відбувається дуже швидко.

Отже, лінійна адреса може вважатися фізичною адресою, якщо не включений режим сторінкової трансляції адрес. Апаратні засоби мікропроцесора для підтримки розглянутого способу подвійної трансляції віртуальних адрес у фізичні явно недостатні, і при наявності великої кількості невеликих сегментів приводять до повільної роботи. Справді, тіньовий регістр при кожнім селекторі є в єдиному екземплярі, і при переході на інший сегмент буде потрібно знову знаходити і витягати відповідний дескриптор сегмента, а це вимагає часу. Сторінковий же спосіб трансляції віртуальних адрес, як ми знаємо, має чимало своїх переваг. Тому в захищеному режимі роботи, при якому завжди діє описаний вище механізм визначення лінійних адрес, може бути включений ще і сторінковий механізм.