Описание функционирования центрального процессора на микропрограммном уровне

Процесс считывания команды выглядит следующим образом:

-

RAP:=SK;

В регистр РАП оперативной памяти переписывается значение счётчика команд;

-

RCH:=ЧТZC(RAP);

Чтение команды из памяти в регистр РСП (регистр счёта памяти)10;

-

RK:=RCH;

Запись в регистр РК значения регистра РСП.

-

SK:=SK+1;

Увеличение значения счётчика команд на длину команды;

Процесс выборки операндов описывается следующими командами:

Выборка первого операнда:

1) RAP:=RK(A1);

В регистр РАП оперативной памяти переписывается значение адресного поля первого операнда;

2) RCH:=ЧТZC(RAP);

Чтение по адресу-значению регистра РАП из памяти в регистр РСП адреса ячейки, содержащей адрес первого операнда;

-

RAP:=RCH;

Перезапись значения из регистра РСП в регистр РАП;

4) CPC:=RCH;

Присвоение счётчику CPC значения регистра РСП;

5) RCH:=ЧТZC(RAP);

Чтение по адресу-значению регистра РАП из памяти в регистр РСП значения операнда;

6) R1:=RCH;

Запись операнда из регистра РСП во входной регистр АЛУ – R1.

Выборка второго операнда:

-

RARP:=RK(A2);

В регистр РАРП регистровой памяти переписывается значение адресного поля второго операнда;

2) RCHR:=ЧТRONS(RARP);

Чтение по адресу-значению регистра РАРП из регистровой памяти в регистр РСП значения операнда;

3) R2:=RCHR;

Запись операнда из регистра РСП во входной регистр АЛУ – R1.

Реализация алгоритма умножения описывается следующим образом

Теоретически алгоритм умножения двоичных чисел с фиксированной запятой, представленных в прямом коде описывается так:

-

Определение знака произведения путем сложения по модулю 2 знаковых разрядов множимого и множителя;

-

Обнуление знаковых разрядов отрицательных операндов;

-

Анализ очередной цифры множителя (начиная с младших разрядов).

Если очередная цифра множителя равна 1, то к сумме частичных произведений (первоначально равной 0) прибавляется множимое, в противном случае прибавляется ноль.

-

Сдвиг суммы частичных произведений вправо относительно неподвижного множимого, причём младший разряд суммы частичных произведений является очередным разрядом ответа – произведения двух чисел.

-

Повторение пунктов 3 и 4 n раз, где n =r+1, r – разрядность чисел, без учёта знака.

-

Присвоение произведению знака, определённого в п.1.

В результате последняя сумма частичных произведений будет содержать старшие разряды произведения, а сдвигаемые на предыдущих циклах младшие разряды текущих сумм частичных произведений – младшую.

Микропрограммное описание

Подготовка к процессу умножения

-

TZ:=R1[n-1] XOR R2[n-1];

Нахождение знака произведения и сохранение его значения в триггере знака TZ;

-

R1[n-1]:=0; R2[n-1]:=0;

Обнуление знаков операндов;

-

SCH:=n;

Присвоение счётчику циклов значения разрядности регистров операндов;

-

RB:=0;

Обнуление регистра RB;

Умножение

-

R2[0]=0?

Проверка младшего разряда множителя. Если он равен 0, то переход к пункту 2. Иначе переход к пункту 3.

-

RA:=0;

Обнуление регистра RA. Переход к пункту 4.

-

RA:= R1;

Присвоение регистру RA значения множимого, хранимого в регистре R1:

-

RC:=П(1)( RA+RB);

Сложение значений регистров RA и RB и запись полученной суммы, сдвинутой на один разряд вправо в регистр RC;

-

R3:=П(1)R2;

Запись в регистр R3 значения регистра R2, двинутого на 1 разряд вправо;

6) R3[n-1]:= ( RA+RB)[0];

Старшему разряду регистра R3 присваивается значение младшего разряда суммы значений регистров RA и RB.

-

RB:=RC;

Запись значения регистра RC, содержащего значение текущей суммы частичных произведений, сдвинутое вправо в регистр RB;

-

R2:=R3;

Запись в регистр множителя R2 значения регистра R3, содержащего оставшиеся непроанализированными разряды множителя в младшей части, а в старшей части – разряды результата.

-

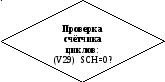

SCH:=SCH-1;

Уменьшение значения счётчика циклов на 1;

-

Проверка значения счётчика циклов. Если SCH не равен нулю, то переход к п. 1. Иначе – переход к п. 10;

-

RC[n-1]:=TZ;

Присвоение произведению значения триггера знака.

Запись результатов

-

RCH:=RC;

Запись в регистр РСП значения старших разрядов произведения;

-

CPC:=CPC+n;

Увеличение значения счётчика корректировки адреса на ширину выборки;

-

ZS(RAP):=RCH;

Запись в память значения старших разрядов произведения;

-

RCH:=R2;

Запись в РСП значение младших разрядов произведения;

-

RAP:=CPC;

Установка в РАП значения счётчика корректировки адреса;

-

ZS(RAP):=RCH.

Запись в память младших разрядов произведения.

Структурная схема микропрограммы с обозначением управляющих вентилей представлена на стр. 13.

Структурная схема микропрограммы

(без совмещения)

Выборка команды:

(V1) RAP:=SK;

(V5) RCH:=ЧТZC(RAP);

(V2) RK:=RCH;

(V3) SK:=SK+1;

Выборка операндов: (V8) RAP:=RK(A1);

(V5) RCH:=ЧТZC(RAP); (V7) RAP:=RCH; (V26) CPC:=RCH;

(V5) RCH:=ЧТZC(RAP); (V6) R1:=RCH; (V9) RARP:=RK(A2);

(V11) RCHR:=ЧТRONS(RARP);

(V12) R2:=RCHR;

Подготовка к процессу умножения: (V18) TZ:=R1[n-1]

XOR R2[n-1]; (V22) R1[n-1]:=0; (V22) R2[n-1]:=0; (V19) SCH:=n; (V20) RB:=0;

(V13) RA:= R1

(V21) RA:=0

(V14) RC:=П(1)(

RA+RB); (V14) R3[n-1]:=

( RA+RB)[0];

(V14) R3:=П(1)R2; (V15) RB:=RC; (V27) R2:=R3; (V23) SCH:=SCH-1;