- •Общие сведения. Основные определения

- •Классификация микропроцессоров

- •Мп классифицируются

- •8, 16, 32, 64 Разрядные, секционные.

- •Организация шин

- •Шинная структура связи

- •Принципы построения микропроцессорных систем

- •3. Принцип микропрограммного управления состоит в возможности осуществления элементарных операций микрокоманд (сдвигов, пересылок информации, логических операций).

- •Обобщенная структура микропроцессорной системы управления

- •Основные узлы бис микропроцессора

- •Режимы работы микропроцессорных систем

- •3) Прямой доступ к памяти

- •Архитектура микропроцессора

- •Упрощенная функциональная схема алу

- •Достоинства и недостатки архитектур мп

- •Обоснование выбора микропроцессора

- •Критерии выбора микропроцессора

- •Организация ввода/вывода

3) Прямой доступ к памяти

Обмен по системной шине идет без участия процессора. Внешнее устройство, требующее обслуживание, сигнализирует процессор о необходимости прямого доступа к памяти. Процессор заканчивает выполнение текущей программы и отключается от всех шин, сигнализируя о начале обмена ПДП.

Операция ПДП сводится к пересылке информации из устройства ввода/вывода в память, или наоборот. По окончании обмена процессор возвращается к прерванной программе, продолжая с места прерывания.

Как и в случае прерывания реакция на внешние события при прямом доступе к памяти медленнее, чем при программном режиме. В этом случае требуется введение в систему дополнительного устройства – контроллера ПДП, который будет осуществлять обмен по системной магистрали.

Контроллер ПДП – это специализированный процессор, отличается тем, что не участвует в обмене, может входить в состав устройств ввода/вывода, которым необходим режим ПДП.

Обмен с помощью ПДП может обеспечить более высокую скорость передачи информации, чем программный обмен, т. к. процессор передает данные медленнее, чем контроллер ПДП. Но скорость обмена в режиме ПДП обычно ограничена возможностями магистрали.

Архитектура микропроцессора

Она объединяет составные части микропроцессора, а также связи и взаимодействия между этими частями. Архитектура включает структурную схему микропроцессора, программную модель МП (описание функции регистров), информацию об организации памяти (способ адресации, емкость), описание процедур ввода/вывода.

Существует 2 основных типа архитектуры МП: Гарвардская и Фон-Неймовская (45).

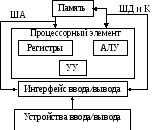

По Фон-Неймовской архитектуре программа и данные находятся в общей памяти, доступ к которой осуществляется по одной шине данных и команд.

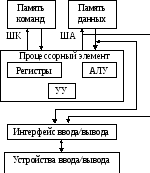

Особенностью Гарвардской архитектуры (двухшинная) является то, что память данных и память программ разделены и имеют отдельные шину данных и команд, что позволяет увеличить быстродействие системы.

Структурная схема обеих типов структур содержит процессорный элемент, память, интерфейсы ввода/вывода и устройства ввода/вывода.

Память и ИВВ могут быть для различных типов МП как внутренними (размещаются в одном кристалле), так и внешними. Процессорный элемент содержит АЛУ, УУ и выполняет функции обработки данных и управления процессами обмена информаций.

Память обеспечивает хранение данных и кодов команд программы. Интерфейсы ввода/вывода (ИВВ) предназначены для связи с устройствами ввода/вывода.

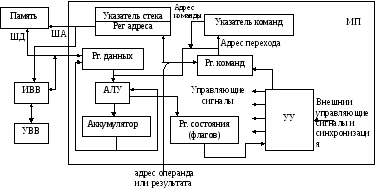

РАСШИРЕННАЯ СТРУКТУРНАЯ СХЕМА С ПРОЦЕССОРОМ ФОН-НЕЙМОВСКОЙ АРХИТЕКТУРЫ

Схема содержит УУ, АЛУ, регистры, аккумулятор, указатель команд и стека. УУ вырабатывает управляющие сигналы для всех блоков микропроцессорной системы в соответствии с кодами команд, внешними управляющими сигналами и сигналами синхронизации, а также управляет обменом информацией между МП, памятью и устройством ввода/вывода.

УПРОЩЕННАЯ СТРУКТУРНАЯ СХЕМА УУ

Рг. команд – запоминающий регистр, в котором хранятся код команды, код выполняемой операции и адреса операндов, участвующих в операции.

Дешифратор операций – логический блок, выбирающий в соответствии с поступающим из регистра команд кода операции – один из множества имеющих у него выходов.

ПЗУ микропрограмм – хранит в своих ячейках управляющие сигналы, необходимые для выполнения операций обработки информации.

Импульс, по выбранному дешифратором операции, в соответствии с кодом операции считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов.

Узел формирования адреса – устройство, вычисляющее полный адрес ячейки памяти (Рг.) по данным, поступающим из регистра команд и регистров микропроцессора.

УУ реализует функции: начальная установка МП, синхронизация, прерывание, согласование быстродействия модулей микропроцессорной системы.

1. Функция начальной установки МП: внешний сигнал начальной установки МП (Reset) формируется при включении источника питания МП. При появлении этого сигнала УУ обеспечивает загрузку нулевого значения в указатель команд, который инициирует выборку из памяти байта команды с нулевым адресом. В конце выборки содержимое указателя команд увеличивается на 1 и выбирается байт команды со следующим адресом.

2. Функция синхронизации: в соответствии с внешними управляющими сигналами и сигналами синхронизации УУ синхронизирует работу всех блоков МП.

3. Функция прерываний: с поступлением сигнала прерывания УУ инициирует выполнение подпрограммы обработки соответствующего прерывания. Потребность в реализации функции прерываний возникает тогда, когда во время выполнения основной программы необходимо перевести МП на решение другой задачи (например, для обработки аварийной ситуации или работы с устройствами ввода/вывода).

4. Функция согласования быстродействия модулей микропроцессорной системы: во время обслуживания памяти и устройств ввода/вывода, быстродействие которых значительно меньше, чем у МП, согласование быстродействия реализуется генерацией тактов ожидания МП. Во время обслуживания устройств с более высоким быстродействием, чем у МП, используется режим прямого доступа к памяти.

АЛУ – представляет собой комбинационную схему на основе сумматора, которая сигналами с выходов УУ настраивается на выполнение определенной арифметической и логической операции.

АЛУ выполняет арифметические и логические операции над операндами, которые пересылаются из памяти или регистров МП.