Расширенная структурная схема с процессором фон-неймановской архитектуры

Схема процессора содержит устройство управления, АЛУ и регистры данных , адреса команд, состояния, а также аккумулятор, указатель команд и указатель стека.

УУ вырабатывает управляющие сигналы для всех блоков МПС в соответствии с кодами команд, внешними управляющими сигналами и сигналами синхронизации, а также управляет обменом информации между памятью, МП и устройствами ввода-вывода.

Схема УУ

Регистр команд – запоминающий регистр, в котором хранится код команды: код выполняемой операции и адреса операндов, участвующих в операции. Расположен в интерфейсной части МП в блоке регистров команд.

Дешифратор операций – логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции один из имеющихся у него выходов.

ПЗУ микропрограмм хранит в своих ячейках управляющие сигналы необходимые для выполнения операций обработки информации.

Узел формирования адреса находится в интерфейсной части МП, вычисляет полный адрес ячейки памяти или регистра по данным, поступающим из регистра команд и регистра адреса.

Кодовые шины данных, адреса и команд – часть внутренней интерфейсной шины МП.

УУ реализует следующие функции:

1. функция начальной установки МП

Внешний сигнал начальной установки МП поступает при включении источника питания RESET. При появлении этого сигнала УУ загружает «0» в указатель команд, который инициирует выборку из памяти байта команды с нулевым адресом.

В конце выборки содержимое указателя команд увеличивается на 1, и выбирается байт команды со следующим адресом;

2. синхронизация

В соответствии с внешними управляющими сигналами и сигналами синхронизации УУ синхронизирует работу всех блоков МП.

3. прерывания

С поступлением сигнала прерывания УУ инициирует выполнение подпрограммы обработки соответствующего прерывания.

4. функция согласования быстродействия модулей МПС

Во время обслуживания памяти, устройств ввода-вывода, быстродействие которых меньше, чем у МП, согласование быстродествия реализуется генерацией тактов ожидания МП.

Во время обслуживания устройства с большим быстродействием, чем у МП, используется режим прямого доступа к памяти (ПДП).

АЛУ представляет собой комбинационную схему на основе сумматора, который сигналами с выходов УУ настраивается на выполнение арифметических или логических операций.

АЛУ выполняет арифметические операции над операндами, которые пересылаются из памяти или регистра МП.

Операнд – объект в виде значений данных содержимого регистра или содержимого ячейки памяти, с которой оперирует команда.

Полученный после выполнения операции результат пересылается в регистр или ячейку памяти.

Сумматор – вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов.

Регистры – быстродействующие ячейки памяти различной длины. Регистр 2 имеет разрядность одного слова, регистр 1 имеет разрядность двойного машинного слова.

При выполнении операции, в регистр 1 помещается число 1, по завершению операции – результат. В регистре 2 находится число 2, по завершению операции результат в нем не изменяется.

Схемы управления принимают по шинам управления управляющие сигналы от УУ и преобразуют их в сигналы для управления регистрами или сумматором.

Аккумулятор – это регистр, в котором хранится один из операндов. После выполнения команды в аккумуляторе вместо операнда, там размещается результат.

В восьмиразрядных процессорах А принимает участие во всех операциях АЛУ. В 16-разрядных процессорах большинство команд выполняется без участия А, кроме ввод-вывод, умножение, деление.

Регистры предназначены для хранения n-разрядного двоичного числа. Они представляют собой n-триггеры со схемой управления.

Регистры создают внутреннюю память МП и используются для хранения промежуточных результатов вычисления.

Указатель команд или программный счетчик предназначен для хранения адреса ячейки памяти, которая содержит код команды. Для перехода к следующей команде содержимое счетчика увеличивается на единицу в момент выборки команды из памяти. В конце выполнения команды в счетчике команды хранится адрес следующей команды.

Указатель стека – это регистр, который хранит адрес последней занятой ячейки стека.

Регистр команд хранит код команды на протяжении всего времени ее выполнения.

Регистр адреса предназначен для хранения адресов и данных, используемых во время выполнения команды в АЛУ.

Регистр флагов хранит информацию о результате операции в АЛУ и представляет собой несколько триггеров, выходы которых находятся в 1 или 0. Например, флаг нулевого результата устанавливается в 1, если в А ноль.

Достоинства и недостатки архитектур МП

Архитектура с общей шиной распространена больше (в ПК, и в сложных микрокомпах).

Архитектура с раздельной шиной применяется в однокристальных компах.

Архитектура с общей шиной (фон-неймановская) проще, не требует от процессора одновременного обслуживания 2х шин и контроль обмена по 2м шинам.

Наличие единой памяти команд и данных позволяет гибко распределить ее объем между кодами данных и команд. Перераспределение памяти не вызывает проблем. В системах с такой архитектурой память бывает довольно большого объема, что позволяет решать самые сложные задачи.

Архитектура с разделенными шинами данных и команд сложнее. Заставляет процессор работать одновременно с двумя потоками кодов, обслуживать обмен по двум шинам одновременно. Программа может размещаться только в памяти команд, данные – только в памяти данных. Память данных и команд не слишком большого объема, поэтому применение систем с данной архитектурой ограничено.

При единой шине данных и команд процессор вынужден по одной шине принимать данные из памяти или устройств ввода вывода и передавать данные в память или устройства ввода вывода.

Современные процессоры способны совместить выполнение команд и проведение циклов обмена по системной шине. Использование конвейерных технологий и быстрой кэш-памяти позволяет ускорить процесс взаимодействия со сравнительно медленной системной памятью.

Повышение тактовой частоты и совершенствование структуры МП дают возможность сократить время выполнения команд, но дальнейшее увеличение быстродействия системы возможно только при совмещении пересылки данных и чтения команд, т.е. при переходе к архитектуре с двумя шинами.

В случае двухшинной архитектуры обмен по обеим шинам параллелен и независим во времени. Соответственно структуры шин (количество разрядов кода адреса и кода данных, порядок и скорость обмена информацией) могут быть выбраны оптимально для той задачи, которая решается каждой шиной. Переход на двухшинную архитектуру ускоряет работу МП системы, но требует усложнения аппаратуры и дополнительных затрат.

Память данных в этом случае имеет свое распределение адресов, а памят команд – свое. Основное применение двухшинной архитектуры в микроконтроллерах, которым не требуется решение сложных задач, но необходимо максимально быстродействие при заданной тактовой частоте.

Обоснование выбора МП

Для конкретной области применения можно сформулировать совокупность требований к аппаратуре, ПО и вспомогательным средствам.

Требования к МП как к элементу системы определяются функциональным назначением всей системы. В реальных системах можно выделить четыре основных сферы применения МП:

- встроенные СУ (программное управление станками, контроль расхода топлива и т.д.)

МП во встроенных СУ выполняет функции, ориентированные на обработку потоков входных и выходных сигналов.

В этих системах МП выполняет роль предпроцессора, т.е. процессора предварительной обработки данных, представленных в аналоговой форме.

Для таких МП важна надежность и способность быстрого выполнения арифметических и логических операций.

- МП, управляющие процессом или объектом в реальном масштабе времени. По сравнению с предыдущим типом МП, в данном случае важным является производительность, системны средства защиты питания, автоматический перезапуск после сбоя.

- МП для обработки сигналов связи, т.е. управляющие процессом приема, передачи сообщения, работают с нечисловой информацией. Сообщение состоит из набора символов передаваемых к месту назначения с минимальной обработкой. Важны гибкость систем адресации.

- МП в системах для научно-технических расчетов. Должны иметь развитые средства взаимодействия с пользователем, ПО с языками высшего уровня, развитую систему команд.

Критерии выбора МП можно разделить на две группы в зависимости от того, если рассматривать МП как микросхему или программно вычислительно устройство.

МП характеризуется следующими параметрами (как микросхема):

- типом базовой технологии

- степенью интеграции элементов

- числом источников питания, их номиналы и допуски на номиналы

- тип корпуса

- помехоустойчивость

- нагрузочная способность

- стоимость и т.д.

МП характеризуется следующими параметрами (как вычислительное устройство):

- разрядность обрабатываемых данных и выполняемых команд

- способность к наращиванию разрядности

- число команд

- число внутренних регистров

- возможность обеспечения режима прерываний

- число уровней прерываний

- тип интерфейса

- наличие и объем стека

- объем прямо адресуемой памяти

- наличие канала прямого доступа к памяти

- число входных и выходных шин и их разрядность

Основные критерии выбора МП для перечисленных сфер применения

|

Критерий выбора МП |

ВСУ |

УПВ |

ППС |

НТО |

|

1. производительность |

|

+ |

|

+ |

|

2. обработка битов |

+ |

+ |

+ |

|

|

3. развитая адресация |

|

|

+ |

+ |

|

4. многоуровневое прерывание |

+ |

+ |

|

|

|

5. развитый ввод-вывод |

+ |

+ |

|

|

|

6. наличие таймера |

+ |

+ |

|

|

|

7. канал прямого доступа к памяти |

|

|

+ |

|

|

8. защита питания от сбоев |

|

+ |

|

|

|

9. высокая надежность |

+ |

+ |

|

|

|

10. автоматический перезапуск после сбоя |

|

+ |

|

|

|

11. программное обеспечение я языками авсокого уровня |

+ |

|

|

+ |

|

12. средства взаимодействия с пользователем |

|

|

|

+ |

Оценка качества и выбор того или иного типа МП для конкретной области применения проводится ориентировочно, например с учетом весовых коэффициентов, учитывающих важность того или иного параметра для потребителя.

Весовые коэффициенты определяющие важность первичных характеристик аппаратных средств

|

Критерий выбора |

Весовой коэф, % |

Диапазон парм-ов |

Балл значимости |

|

1. разрядность данных |

20 |

4, 8, 16, 32 |

1, 2, 4 |

|

2. эффективность системы команд |

15 |

Малая, средняя, высокая |

1, 2, 4 |

|

3. число уровней приоритетов |

10 |

До 8, 16-32, 64 и более |

1, 2, 4 |

|

4. время реакции на прерывание в МКС |

13 |

Более 10, 1-10, менее 1 |

1, 2, 4 |

|

5. аппаратурные арифметические расширители |

10 |

- , средние, обширные |

1, 2, 4 |

|

6. число индексных регистров |

12 |

До 8, 16-32, 64 и более |

1, 2, 4 |

|

7. емкость памяти в Кбайт |

10 |

Менее 16, 16-64, более 64 |

1, 2, 4 |

|

8. цикл памяти, мкс |

10 |

Более 2, 1-2, менее 1 |

1, 2, 4 |

По данным таблицы числовая оценка в баллах.

![]()

Принципы проектирования МП систем

Положено три принципа (принцип 3х М):

1. м_одульность

2. м_агистральность

3. м_икропрограммируемость

Принцип модульности состоит в том, что система строится на основе ограниченного количества типов функционально и конструктивно законченных модулей.

Модульный подход способствует стандартизации элементов не на уровне интегральных схем, а на более высоком (плата, блок, шкаф).

Приводит к сокращению трудовых или интеллектуальных затрат на проектирование систем, а также упрощает наращивание и изменение конфигурации системы.

Принцип магистральности определяет характер связей между функциональными блоками МП системы.

Все блоки соединяются с единой системной шиной.

Среди способов организации связей элементов внутри модулей и между модулями в системе выделяют два основных:

1. с помощью произвольных связей реализующих способ «каждый с каждым»

2. с помощью упорядоченных связей (магистральный).

Магистральный способ обеспечивает обмен информацией между функциональными блоками МП системы – с помощью магистралей объединяющих входные и выходные шины.

Различают одно, двух и трех магистральные связи.

Магистральный способ позволяет минимизировать количество связей между блоками, повысить регулярность операционного устройства и устройства управления, обеспечить стандартизацию интерфейса, сократить число выводов БИС.

В этом случае осуществляется взаимосвязь схемотехнических и структурных решений, появляющиеся в виде создания двунаправленных буферных каскадов с тремя устойчивыми состояниями.

Принципы магистральности и модульности позволяют наращивать управляющие и вычислительные возможности МП путем подсоединения других модулей к системной шине.

Принцип регулярности структуры – предполагает повторяемость элементов структуры и связей между ними.

Применение этого принципа позволяет повысить эффективность интегрального исполнения устройств вследствие увеличения интегральной плотности, уменьшения длин связей, упрощения и сокращения времени топологического и схемотехнического проектирования, снижение стоимости средств.

Основными способами увеличения регулярности структур систем обработки информации:

- использование устройств памяти (ОЗУ, ПЗУ, логические матрицы)

- применение регистровых структур

- выполнение регистров общего назначения (РОН) в виде ячеек памяти ОЗУ

- использование магистрального способа обмена и т.д.

Принцип микропрограммного управления

Состоит в возможности осуществления элементарных операций – микрокоманд (сдвигов, пересылок информации, логических операций).

Используя определенные комбинации микрокоманд можно создать технологический язык, т.е. набор команд максимально соответствующий назначению системы.

В секционных МП набор команд можно изменить используя другие микрокоманды памяти.

Микропрограммное управление обеспечивает наибольшую гибкость при организации многофункциональных МП модулей и позволяет осуществлять проблемную ориентацию МП системы.

За счет возможности смены микропрограмм повышается гибкость устройства.

За счет рассредоточенности управления и распределенности памяти обеспечивается параллельное решение задач.

За счет применения серийно освоенных БИС повышается надежность системы.

За счет регулярности структуры упрощается контроль функционирования устройства.

КОЛЛОКВИУМ

Однокристальные МП (8 и 16-ти разрядные)

Однокристальные 8-ми разрядные процессоры

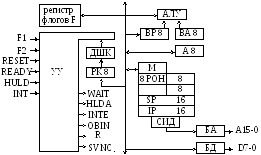

Структурная схема обобщенного 8-ми разрядного МП:

Схема имеет единую внутреннюю 8-ми разрядную шину, по которой передаются данные, коды команд и адреса.

Структурная схема содержит:

- устройство управления (УУ)

- дешифратор команд (ДШК)

- регистр команд (РК)

- арифметико-логическое устройство (АЛУ)

- аккумулятор (А)

- временной аккумулятор (ВА)

- временный регистр (ВР)

- регистр флагов (F)

- блок 8-ми разрядных регистров общего назначения (РОН)

- мультиплексор (М)

- указатель стека (SA)

- указатель команды (IP)

- буферный регистр адреса (БА)

- буферный регистр данных (БД)

- схема инкремента / декремента (СИД)

УУ – в соответствии дешифрованными кодами команд и внешними управляющими сигналами генерирует управляющие сигналы для всех блоков структурной схема.

ДШК – формирует сигналы для устройства управления в соответствии с дешифрованным кодом команд.

В 8-ми разрядном регистре команд хранится машинный код команды 1 байт.

АЛУ – построено на основе сумматора и логических элементах, которые сигналами с выхода УУ настраиваются на выполнение арифметической или логической операции.

А – 8-ми разрядный регистр в котором хранится один из операндов в двух операндных командах, а также результат операции, например ADD В.

В некоторых МП регистры общего назначения обозначаются буквами латинского алфавита (B, C, D, E, H, L, буферные: W, Z), в некоторых других R0, R1, R2.

|

W |

Z |

|

B |

C |

|

D |

E |

|

H |

L |

ВА, ВР – 8-ми разрядные буферные регистры, позволяющие определить входы АЛУ от его выходов т.е. исключить гонку сигналов.

Регистр флагов – представляет собой несколько триггеров, которые устанавливаются в 1 или сбрасываются в 0 в зависимости от результата операции в АЛУ (переноса, переполнения, четности)

Мультиплексор – устройство соединяющее один из регистров общего назначения с внутренней шиной.

Указатель стека – 16-ти разрядный регистр, в котором хранится адрес последней занятой ячейки стека.

Указатель команд – 16-ти разрядный регистр в котором хранится адрес последней выполняемой команды.

После выборки из памяти программ очередного байта команды содержимое IP увеличивается на 1.

РОН – блок 8-ми разрядных регистров, в которых хранятся данные и промежуточные результаты.

Блок РОН можно рассматривать как быстродействующее ОЗУ, расположенной на кристалле МП.

Некоторые типы 8-ми разрядных МП кроме 8-ми разрядных РОН содержат 16-ти разрядные регистры для организации косвенной адресации.

Другие предполагают обращение к паре 8-ми разрядных регистров как к одному 16-ти разрядному.

БА, БД – регистры с тремя состояниями выхода, предназначены для формирования сигналов на линиях шины адреса и шины данных.

СИД – устройство позволяющее без участия АЛУ увеличить или уменьшить на 1 содержимое одного из РОН, SP или IP.

Конструктивно БИС 8-ми разрядного процессора – микросхема 40-ка выводная из которых 16 – шина адреса, 8 – шина данных, 12 – управляющие сигналы, 2(4) - линии питания.

Основные входные и выходные сигналы

F1 F2 входы двух неперекрывающихся во времени последовательностей импульсов синхронизации.

RESET – вход сигнала установки (сброс)

READY – вход сигнала готовности внешнего устройства или памяти к обмену. Используется для организации обмена с менее быстродействующими устройствами по сравнению с МП.

WAIT – ожидание сигнала. Выход сигнала подтверждения ожидания. Активный уровень H(1) сигнала свидетельствует о том, что процессор перешел в режим ожидания и выполняет такты ожидания.

HOLD – вход сигнала прямого доступа к памяти или запроса захвата шин. Используется для организации обмена с устройствами, быстродействие которых больше, чем быстродействие МП.

HLDA – ожидание – выход сигнала подтверждения прямого доступа к памяти. Активный уровень сигнала H(1) свидетельствует о том, что процессор перевел шины адреса данных и управления в высокоимпедансное состояние (z – состояние, состояние высокого сопротивления).

INT – вход сигнала запроса прерывания.

INTE – выход сигнала разрешения прерывания.

DBIN (Data Bus In) – выход сигнала чтения. Высокий уровень (Н) сигнала свидетельствует о том, что двунаправленная шина данных находится в режиме приема информации.

WR – выход сигнала записи. Активное состояние у него 0. Низкий (L) уровень сигнала, свидетельствует о том, что двунаправленная шина данных находится в режиме выдачи информации.

SYNC – выход сигнала синхронизации. Высокий уровень сигнала (Н) свидетельствует о том, что по шине данных передается байт состояния, который используется для формирования управляющих сигналов.

Схемы конкретных 8 – разрядных МП отличаются количеством и обозначением регистров: B, C, D, E, H, L, R0, R1, R2 а также некоторыми управляющими сигналами i8080, KR580 ИK80 (ВМ80), Z80, z8085.

Например в МП i8085 вместо двух сигналов F1 и F2 используется один сигнал CLK, вместо DBIN – RD. Низкий уровень этого сигнала свидетельствует, о том, что двунаправленная ШД находится в режиме приема информации. Также здесь (в i8085) есть дополнительный сигнал M/I/O – Memory/Input – Output – это признак обращения к памяти (1) или к устройству ввода/вывода, но отсутствует сигнал SYNC.

Схема (*) работает следующим образом: при включении питания или при формировании сигнала начальной установки (RESET), содержимое указателя команд (IP) приобретает нулевое значение, начинается машинный цикл выборка (извлечение кода команд из памяти).

Содержимое ячейки памяти по нулевому адресу через буферный регистр данных (БД), и внутреннюю шину МП поступает в регистр команд, а затем в ДШК. Соответственно дешифрованным кодам команд и внешним сигналам синхронизации УУ формирует управляющие импульсы для каждой микрооперации команды.

Праграммной моделью МП называется совокупность программно доступных регистров (тех, содержимое которых можно прочитать или изменить с помощью команд).

В программную модель МП i8085 и КР580ИК80 входит А, РОП, регистр флагов (F), указатель стека, и указатель команд (или программный счетчик).

Организация памяти

Максимально возможная емкость памяти с прямой адресацией определяется разрядностью ША. Большинство 8-разрядных процов (z80, i8080, i8085, Motorola 6800) имеют 16-разрядную ША, т.е. могут адресовать: 216 = 64 КБ памяти.

МП с 8-разрядной ШД имеют 4 основных способа адресации операндов:

1. прямая адресация (2 и 3 байты команды содержат данные или адрес)

2. регистровая адресация (в мнемонике команды, указывается РОН, в котором находится операнд)

3. непосредственная адресация (в этом режиме 2-й и 3-й байты команды содержат 8-ми или 16-ти битовый операнд, операнд в этом случае находится в памяти программ)

4. косвенно – регистровая адресация (указывается в команде регистр или пара регистров, содержащих адрес ячейки памяти)

Организация ввода/вывода

8-разрядные МП имеют возможность передать или принять данные из внешних устройств ввода/вывода.

УВВ соединены с системной шиной МП с помощью портов ввода/вывода, которые представляют собой 8-разрядные регистры со схемами выборки и управления чтением-записью. Количество таких портов определяется разрядностью адресов портов. При 8-разрядном адресе имеется возможность обращаться (подключать) 256 портов ввода или 256 портов вывода.

В качестве портов могут быть использованы буферные регистры КР580ИР82, КР589ИР12 или параллельный интерфейс КР580ВВ55.

Ввод или вывод данных может осуществляться двумя способами:

1. с использованием отдельного адресного пространства УВВ – разрешает выполнять ввод и вывод данных по командам INPUT и OUTPUT (IN, OUT).

2. с использованием общего с памятью адресного пространства. Предусматривает расположение адресов портов в общем с памятью адресном пространстве, при этом, обращение к портам какое же, как и обращение к памяти.

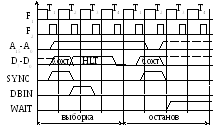

Временная диаграмма цикла выборка

(извлечение кода команд из памяти)

Временная диаграмма (запись в память)

Выполнение команд в МП Intel 8080

Каждая команда выполняется в МП на протяжении командного цикла, который состоит из цикла (фазы) выборки команды и цикла ее выполнения.

Продолжительность цикла выборки команды зависит от формата команды (количество байт в машинном коде команды).

Команды занимают от 1 до 3-х байт в программной памяти. Многобайтные команды хранятся в соседних ячейках памяти.

Продолжительность цикла исполнения команды зависит от способа адресации операндов.

Например при выполнении команд с регистровой адресацией не нужно обращения к памяти для чтения операнда, в отличии от команд с косвенной адресацией.

Поэтому продолжительность командного цикла в МП Intel 8080 различна для различных команд и определяется количество обращений к памяти или внешнему устройству.

Интервал, на протяжении которого осуществляется одно обращение к памяти или внешнему устройству называется (определяется) как машинный цикл (М).

В команде может быть от одного (для однобайтных команд с регистровой адресацией) до пяти (для трехбайтных сложных команд) машинных циклов.

Машинный цикл разбивается на некоторое число машинных тактов, на протяжении каждого из которых выполняется элементарное действие – микрооперация (Т).

Количество тактов микрооперации в цепи определятся кодом команды и лежит в пределах от 3-х до 5-ти.

Продолжительность такта задается периодом импульсов синхронизации и определяется как интервал времени между фронтами соседних импульсов последовательности F1.

Для синхронизации проца с памятью и внешними устройствами, которая характеризуется меньшим быстродействием для организации работы проца в режиме ПДП и останове проца предусмотрено 3-и режима: ожидание, захват шин, останов, продолжительность которых имеет произвольную, но кратную продолжительности такта величину.

В зависимости от действий, выполняемых МП различают следующие типы машинных циклов:

1. выборка (чтение одного первого байта команды)

2. чтение памяти (чтение 2 и 3 байта команды или чтение операнда)

3. запись в память

4. чтение в стеке

5. запись в стек

6. ввод данных из внешнего устройства

7. вывод данных на внешнее устройство

8. прерывание

9. останов

10. прерывание при останове

Первым машинным циклом всегда является цикл выборка, на протяжении которого осуществляется выборка из памяти байта кода команды по адресу, определяемому содержимым указателя команд (IP).

Содержимое IP в цикле увеличивается на 1.

Для выполнения однобайтных команд с регистровой адресацией требуется 1 цикл – выборка. Для выборки 2-х или 3-х байтных команд кроме цикла «выборка» нужны 1 или 2 МЦ для чтения второго или 2 и 3 байтов команды (циклы чтение памяти).

Этот цикл чтение памяти необходим также при выполнении команд с косвенной или прямой адресацией.

Для записи операндов или сохранения адресов при выполнении команд пересылок необходимы МЦ «запись в память».

В командах с обращением к стеку необходимы циклы «чтение стека» и «запись в стек».

Адрес памяти определяется указателем стека (SP). Для выполнения команд ввода/вывода выполняется МЦ «ввод и вывод».

Для организации прерываний и остановки проца циклы 8, 9, 10.

Каждый МЦ проца идентифицируется байтом, называемым байтом состояния (слово состояния процессора).

Байт состояния выдается на ШД в начале каждого МЦ и сопровождается одновременной выдачей сигнала SYNC синхронизации на одноименный контакт МП.

Байт состояния несет информацию о последующих действиях МП. Его можно заполнить по сигналу SYNC (синхронизации) и сформировать определенные управляющие сигналы.

СМ ДИАГРАММЫ.

Такты отсчитываются по передним фронтам последовательности F1, а микрооперации в каждом такте определяются передним фронтом последовательности F2.

При тактовой частоте 2 МГц продолжительность такта составляет 0.5 мс. Сигналы на линиях А15-А0 Д7-Д0 изображены в виде линий L и H-уровней. На этих линиях указывается тип информации (присутствие адреса или данных) z-состояние – высокоимпедансное состояние.

В первом машинном такте Т1 на шину адреса А15-А0 выдается адрес (содержимое указателя команд IP, если выполняется цикл выборка, или содержимое указателя адреса, если выполняется цикл чтение памяти).

На ШД линии Д7-Д0 выдается байт состояния, а также формируется сигнал синхронизации на одноименном выводе МП.

Во втором такте Т2 заканчивается поступление байта состояния и сигнал синхронизации SYNC, продолжительность которых равна 1 такту.

В МЦ «выборка» содержимое указателя команд увеличив на 1 для адресации следующего байта команды или следующей команды.

В этом же такте УУ МП производит анализ сигналов на выходах READY - готов, и HOLD – запрет захвата, а также контроль выполнения команды HLT – останова.

Если память или внешнее устройство не готов к обмену (READY=0) в следствии того, что поступил сигнал запрос ПДП (HOLD=1) или выполняется команда останова HLT, то обмен данными производиться не может и проц переходит в режим ожидания.

Кроме того может выполняться один из особых режимов захват шин или останов.

В этих режимах осуществляется ожидание сигнала на протяжении нескольких тактов ожидания (Tw), количество которых определяется внешними сигналами.

В такте Т2 READY=0, а в такте Тw-“1”.

В такте Т3 в зависимости от типа машинного цикла осуществляется обращение к памяти, стеку или входному устройству. В результате в МП вводится 1 временная диаграмма или из него выводится 2 временная диаграмма, байт команды, адреса или данных.

В зависимости от типа команды МЦ может содержать такты Т4 и Т5 (не обязательны, например: если для выполнения команды необходима обработка операндов).

В последнем такте команды (Т3, Т4 или Т5) анализируется наличие сигнала INT – запрос прерывания. Если прерывание разрешено (INTE=1), тогда проц переходит к выполнению МЦ «прерывания».

Особые режимы работы МП Intel 8080

МП имеет следующие особые режимы работы: прерывание, ожидание, захват шин при ПДП, который инициируется внешними сигналами управления и режим «останов» (переход к этому режиму осуществляется программно).

Прерывание

В МП Intel 8080 существуют средства обработки запросов прерываний восьми уровней. Если одно из внешних устройств, соединенных с системой прерывания МП инициирует запрос прерывания, то система формирует сигнал H-уровня на выводе INT (вывод запрос прерывания) одновременно система прерываний посылает на ШД код RSTV (прерывание по вектору V). Вектор V представляет собой код, который указывает начальный адрес в подпрограмме обслуживания данного запроса прерывания.

Последовательность действий МП в режиме прерываний:

1. прием запроса прерывания и блокировка входа запроса прерывания (INT)

2. прием команды RSTV

3. сохранение адреса возврата (содержимого указателя команд IP в стеке)

4. формирование адреса подпрограммы обслуживания запроса прерывания.

Запросы прерывания МП принимаются со входа INT триггером прерываний, которым управляет триггер разрешения прерывания. Его можно программно установить в 1 или в 0, соответственно 1 разрешает прием прерываний от входа INT, а 0-запрещает.

Система прерываний может установить активный уровень сигнала на линии INT в любой момент выполнения программы.

Однако, прием этого сигнала INT синхронизируется следующим образом: при наличии сигнала разрешено прерывание (триггер разрешения прерываний установлен в 1) , триггер прерываний устанавливается в последнем такте последнего машинного цикла на протяжении которого поступил запрос.

Это дает возможность процу завершить выполнение команды прежде чем начнется обработка прерывания. Если прерывание не разрешено (триггер разрешения прерываний установлен в 0) запрос прерываний по входу INT игнорируется.

СМ ДИАГРАММУ.

После приема сигнала запроса прерывания проц переходит к выполнению цикла прерывания, который состоит из 3-х машинных циклов: 1 (м1) предназначен для приема команды RSTV, 2, 3 (м2, м3) для сохранения адреса возврата в стеке.

В первом такте Т1 цикла м1 в байте состояния формируется сигнал подтверждения прерывания, который используется для управления чтением каманды RSTV. В такте Т3 проц принимает по ШД байт команды RSTV, формируемы системой прерываний. В тактах Т4 и Т5 формируется адрес первой ячейки стека, отведенной для хранения адреса возврата из подпрограммы обслуживания запроса прерывания. В циклах м2 и м3 осуществляется запись адреса возврата (содержимого указателя команд в стек). В следующем цикле (который за прерыванием) выбирается первая команда подпрограммы обслуживания прерывания по адресу, определяемому командой RSTV. В частном случае с помощью подпрограммы осуществляется хранение содержимого основных рабочих регистров проца, управление триггером разрешения прерывания, восстановление содержимого регистров и возврат в основную прогу (т.е. восстановление содержимого указателя команд IP).

Захват шины или ПДП

Этот режим используется для организации выполнения операций ПДП. Для этого МП имеет вход HOLD (ЗПДП) и соответствующий ему выход HLDA (ППДП).

Внешнее устройство запрашивает режим ПДП сигналом H-уровня на линии HOLD. При этом проц останавливает выполнение операции и отсоединяется от внешних ША и ШД. Линии шин переходят в высокоимпедансное состояние.

Проц подтверждает принятие запроса ПДП установкой сигнала H-уровня (т.е. 1) на выходе HLDA. Пока действует сигнал на входе HOLD, шины проца находятся в распоряжении внешнего устройства, которое послало прямой запрос к памяти (запрос ПДП).

Сигналы управления обменом информацией между внешним устройством и памятью формируется специальный БИС – контроллером ПДП.

Чтение памяти в режиме ПДП

Сигнал HOLD воспринимается процом в такте Т2, если на входе READY присутствует 1, то на входе внутреннего триггера захвата также устанавливается H-уровень, благодаря чему по фронту следующего за этим импульса F1 сигнал HLDA переключается в 1. При выполнении циклов чтения или ввода проц подтверждает захват в начале такта Т3 по окончании чтения. В циклах записи и вывода это осуществляется в такте, следующим за Т3 по окончании записи.

В обоих случаях шины проца переводятся в высокоимпедансное состояние по фронту импульса F2, следующего за импульсом F1, за которым выполнялось переключение выходов HLDA (утверждение захвата). Проц выходит из режима захвата следующим образом: по окончании сигнала захвата (HOLD) импульсом F2 сбрасывается триггер захвата, благодаря чему по переднему фронту импульса F1 на выходе подтверждения захвата HLDA формируется сигнал низкого уровня (L) и проц переходит к выполению следующего машинного цикла – останов.

Останов

Проц входит в режим останова при выполнении команды HLT.

Переход в режим останова осуществляется за 2 машинных цикла. В первом машинном цикле «выборка» осуществляется считывание из памяти первого байта команды HLT.

Во втором машинном цикле останов по окончании такта Т2 проц переходит в режим останова, в котором ШД и АД переводятся в высокоимпедансное состояние, и проц выполняет такты ожидания.

Режим останова подтверждается битом Д3 в байте состояния, который выдается на ШД в тактах Т1 и Т2 машинного цикла.

Выход из режима останова осуществляется 3-мя способами:

1. подачей сигнала на линию RESET, при этом указатель команд IP приобретает нулевое значение и проц переходит к машинному циклу выборка команды по нулевому адресу.

2. подачей сигнала на вход HOLD – захват. По окончании этого сигнала проц входит в режим останова по переднему фронту импульса F1.

3. подачей сигнала прерывания INT (при наличии сигнала разрешения прерывания INTE), благодаря чему проц по фронту импульса F1 переходит в режим прерывание, начиная с такта Т1. Для этого перед началом режима останова необходимо выполнять установление триггера разрешения прерываний командой EI (DI – запрет прерывания).

Обработка запросов захвата шин и прерывание при останове

Включение МП НАЙТИ САМИМ

КОЛЛОКВИУМ

Однокристальные 16-разрядные МП

К 16-разрядным МП первого поколения относятся МП Intel 8086/8088, Intel 80186/80188, Intel 80286, К 1810ВМ86.

БИС МП i8086 имеет 40 контактов, содержит около 29 тысяч транзисторов, потребляет 1,7 Вт мощности от источника питания +5В, тактовая частота 5, 8 или 10 МГц.

МП выполняет операции над 8-ми и 16-разрядными данными в 2-ом или 2-10-ом виде. Может обрабатывать отдельные биты, строки и массивы данных. Имеет встроенное аппаратное средство умножения/деления.

МП имеет внутреннюю СОЗУ емкостью 14х16 байт, шина адреса является 20-разрядной, что позволяет адресовать 220=1.048.576 (1 Мб) ячеек памяти.

Пространство адресов ввода/вывода составляет 64 кб. В данном МП реализована многоуровневая система прерывания с количеством векторов до 256. Предусмотрена организация ПДП, по которой МП прекращает работу и переводит линии шин в высоимпедансное состояние.

Среднее время выполнения команды составляет 12 тактов.

Особенностью МП i8086 является возможность частичной реконфигенации аппаратной части для обеспечения работы в 2-х режимах: минимальный и максимальный. Режимы работы задаются аппаратно.

В минимальном режиме, используемом для построения однопроцессорных систем, микропроц самостоятельно формирует все сигналы управления врутренним системным интерфейсом.

В максимальном режиме, используемом для построения мультипроц-х систем, микропроц формирует на линиях состояния 2-ный код, зависящий от типа цикла шины. В соответствии с этим кодом контроллер (к1810ВТ88) формирует сигналы управления шины. Контакты, которые освободились в результате кодирования информации используется для управления мультипроцессорным режимом. При использовании арифметического сопроцессора необходимо выбирать максимальный режим.

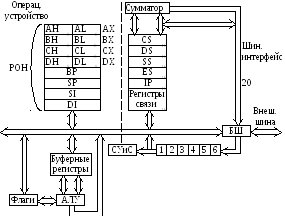

Структурная схема микропроца i8086

В МП i8086 применена конвейерная архитектура, которая позволяет совмещать во времени циклы исполнения и выборки из памяти кодов последующих команд. Это достигается параллельной работой 2-х независимых устройств – операционного устройства и шинного интерфейса.

Операционное устройство выполняет команду, а шинный интерфейс осуществляет взаимодействие с внешней шиной: выставляет адреса, считывает коды команд и операнды, записывает результаты вычисления в память или устройства ввода/вывода.

Операционное устройство состоит из РОН для хранения промежуточных результатов вычислений (данных и адресов).

РОН делится на:

1. Регистры данных – 4е 16ти разрядных регистра (АХ, ВХ, СХ, ДХ), каждый из которых состоит из 2х 8ми разрядных регистров и регистры-указатели (BP, SP, SI, DI). Они служат для хранения адресов при косвенной адресации.

2. АЛУ с буферными регистрами.

3. Схема управления и синхронизации, дешифрует коды команд и генерирует управляющие сигналы для всех блоков схемы МП.

4. Шинный интерфейс, состоит:

- 4х сегментных регистров (CS, DS, SS, ES): CS – сегмент кодов, DS – сегмент данных, SS – сегмент стека, ES – сегмент дополнительных данных.

- указатель команд IP

- регистры связи

- буферная схема шин адреса/данных

- сумматора

- 6-ти байтная регистровая память (очередь команд) работает по принципу FIFO-FIRSTINPUT-FIRSTOUTPUT (первый пришел – первый вышел), сохраняет на выходе порядок поступления команд.

Длина очереди 6 байт.

Если операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует выборку кодов команд из памяти в очередь команд.

//Флаг регистр 16- разрядный устанавливает 9 флагов.//

Выборка из памяти очередного командного слова осуществляется когда в очереди команд обнаруживаются 2 свободных байта. Очередь увеличивает быстродействие МП в случае последовательного выполнения команд. При выборке команд переходов, запросов и возвращения из подпрограмм обработки запросов прерываний, очередь команд сбрасывается и выборка начинается с нового места программной памяти.

Шинный интерфейс формирует физический 20-ти разрядный адрес из 2х 16ти разрядных слов. Первым словом является содержимое одного из сегментных регистров, второе слово зависит от типа адресации операнда или кода команды. Суммирование 16-ти разрядных слов происходит со смещением на 4 разряда и осуществляется с помощью сумматора, который входит в состав шинного интерфейса.

Назначение выводов микропроцессора i8086

Назначение выводов, используемых в обоих режимах работы

|

Обозн-е |

Назначение |

Тип сиг-а |

|

AD15-AD0 |

Мультиплексная двунаправленная шина адреса/данных по которой с разделением во времени передаются адреса и данные. Адреса передается в первом такте цикла шины и сопровождаются сигналом ALE, а данные во второй половине цикла шины и сопровождаются сигналом DEN |

Вх/вых z-состояние |

|

BHE/ST7 |

Вых сиг разрешения старшего байта / сигнал состояния. В первом такте цикла одновременно с адресной информацией передается сигнал BHE. Активный уровень этого сиг (L) означает, что по шине адр/дан (AD15-AD0) передаются 8-разрядные данные. Сиг BHE используется для разрешения доступа к старшему банку памяти или к внешнему устройству с байтовой организацией, подключенному к старшей половине шины данных. В других тактах формируется сигнал состояния ST7. |

Вых. z |

|

RD |

Выходной сигнал чтения указывает на то, что МП выполняет цикл чтения. |

|

|

READY |

Входной сигнал готовности подтверждает, что ячейка памяти или устройство ввода/вывода, адресуемое в команде готово к взаимодействию с МП при передаче данных. |

|

|

INTR |

Входной сигнал запроса маскированного прерывания. Если прерывания разрешены, МП переходит к подпрограмме обработки прерывания, в противном случае игнорирует этот сигнал. |

|

|

RESET |

Входной сигнал аппаратного сброса при H-уровне. Переводит МП в начальное состояние, при котором сброшены сегментные регистры кроме CS (сегмент - кодов), все разряды которого устанавливаются в «1». Указатель команд IP, все флаги, регистры очереди команд и все внутренние триггеры устройства управлении (все сброшено). Сигнал RESET не влияет на состояние РОН. Во время действия этого сигнала все выходы, имеющие 3-и состояния переводятся в высокоимпедансное состояние, выходы, которые имеют 2 состояния становятся пассивными. Минимальная продолжительность сигнала RESET при первом включении МП составляет 50 мкс, при повторном запуске 4 такта синхронизации, т.е. 0,8 мкс при тактовой частоте 5 МГц. По окончании сигнала RESET начинается цикл выборки из памяти команд. |

|

|

TEST |

Входной сигнал проверки. Используется вместе с командой ожидания (WAIT), выполняя которую МП проверяет уровень сигнала TEST. Если TEST=0, МП переходит к выполнению следующей команды после команды ожидания. Если TEST=1, то МП находится в состоянии ожидания и выполняет холостые такты. Периодически с интервалом 5 тактов сигнал CLK (5T CLK) проверяет значение сигнала TEST. |

|

|

CLK |

Входные тактовые импульсы, обеспечивающие синхронизацию работы МП. |

|

|

MN/MX |

(минимакс) Вход сигнала выбора минимального или максимального режимов. Определяет режим работы МП: 1 - минимальный режим, 0 – максимальный режим |

|

Назначение тактов МП в минимальном режиме

|

INTA |

Выходной сигнал подтверждения прерывания. Определяет чтение вектора прерываний. |

|

ALE |

Выходной сигнал разрешения фиксации адреса выдается в начале каждого цикла и используется для записи адреса в регистр-фиксатор. |

|

DEN |

Выходной сигнал разрешения данных определяет появление данных на шине адреса данных. |

|

DT/R |

Выходной сигнал передачи/приема данных определяет направление передачи данных по шине адрес/данные. Предназначен для управления шинными формирователями, действует на протяжении всего цикла шины. |

|

M/IO |

Выходной сигнал признака обращения к памяти (=1) или внешнему устройству (=0). Используется для распределения адресного пространства памяти и устройств ввода/вывода. |

|

WR |

Выходной сигнал записи указывает на то, что МП выполняет цикл «запись в память или ВУ» и сопровождает данные, которые выдаются МП на ШД. |

|

HOLD |

Входной сигнал запроса захвата шин от ВУ или КПДП. |

|

HLDA |

Выходной сигнал подтверждения захвата шин указывает на то, что МП перевел шины адрес/данные, адрес–состояние и управления в z–состояние. |

Назначение выводов, используемых в максимальном режиме

|

ST2-ST0 |

Выходные сигналы состояния характеризуют тип выполняемого цикла шины. Используются для формирования управляющих сигналов. |

Вых. 1, 0, z |

|

RQ/GT0 RQ/GT1 |

Два входных/выходных сигнала запроса/предоставления локальной шины. Используются для связи с другими процами (с арифметическим сопроцом). Линия RQ/GT1 имеет меньший приоритет. Сопроцы – вспомогательные процы, работают параллельно ЦП по одной программе, выбирает из нее инструкции собственного набора команд. |

|

|

LOCK |

Выходной сигнал блокировки (занятости) шины информирует другие процы и устройства о том, что они не должны запрашивать системную шину. |

|

|

QS1, QS0 |

Выходные сигналы состояния очереди идентифицируют состояние внутренней 6-байтной очереди команд, действуют на протяжении всего такта синхронизации после выполнения операции над очередью. Предназначены для сопроцов, которые контролируют шину адрес/данные, фиксирует момент выборки из памяти программы предназначений для него командой, и определяет момент когда эта команда должна выполниться. |

|

Линии состояния

Линии состояния ST2-ST0 идентифицируют тип цикла шины в соответствии в таблицей:

|

Линии состояния |

Тип цикла шины |

||

|

ST2 |

ST1 |

ST1 |

|

|

0 |

0 |

0 |

подтверждение прерывания INTA |

|

0 |

0 |

1 |

ввод (чтение внешних устройств) |

|

0 |

1 |

0 |

вывод (запись во внешнее устройство) |

|

0 |

1 |

1 |

останов |

|

1 |

0 |

0 |

выборка команды |

|

1 |

0 |

1 |

чтение памяти |

|

1 |

1 |

0 |

запись в память |

|

1 |

1 |

1 |

цикла шины нет |

Циклом шины называется обращение к ячейке памяти или ВУ.

В 16-разрядных процах цикл шины может инициировать не только МП, но и арифметический проц или спец проц.

Начало цикла определяется переводом линии состояния ST2-ST0 из пассивного состояния (111) в активное (000). Сигналы ST2-ST0 подаются на входы контроллера шины, который дешифрует их и формирует сигналы управления системной шины:

IOR – сигнал чтения ВУ

IOW – запись во ВУ

MEMR – чтение памяти

MEMW – запись в память

INTA – подтверждение прерывания

ALE – разрешение фиксации адреса

DEN – разрешение фиксации данных

Сигнал ST2 является логическим эквивалентом M/IO, сигнал ST1 является эквивалентом DT/R.

Сигналы ST4, ST3 определяют какой сегментный регистр используется в том или ином цикле

|

ST4 |

ST3 |

Сегментные регистры |

|

0 |

0 |

ES |

|

0 |

1 |

SS |

|

1 |

0 |

CS |

|

1 |

1 |

DS |

Кроме того ST4 и ST3 используются для расширения адресного пространства системы. В этом случае отельный банк памяти емкостью 1 Мбайт выделяется любому из 4х сегментных регистров к выводам ST4, ST3 подключается дешифратор, который выбирает соответствующий банк памяти. Это обеспечивает расширение адресного пространства до 4х Мбайт и защиту от ошибки записи в сегмент, которая перекрывается с другим сегментом.

Сигнал ST5 соответствует состоянию флага разрешения прерывания.

Сигналы ST6, ST7 не используются, зарезервированы для последующих моделей МП.

Идентификация состояния очереди команд осуществляется с помощью QS1, QS0. Значение этих линий определяет операцию над очередью команд.

|

QS1 |

QS0 |

Операции над очередью |

|

0 |

0 |

операции нет, в последнем такте не было выборки из очереди |

|

0 |

1 |

из очереди команд выбран 1-й байт команды |

|

1 |

0 |

очередь песта: была опустошена команда передачи управления |

|

1 |

1 |

из очереди выбран следующий байт команды |

Линии запроса / предоставление локальной шины

Двунаправленные линии RQ/GT0, RQ/GT1 используются для запроса / разрешения доступа к локальной шине. Процесс доступа к шине осуществляется следующим образом: сначала устройство, которое подключено к локальной шине требует доступ к общим ресурсам, формирует импульс продолжительностью 1 такт. После этого в конце текущего цикла МП выдает соответствующий импульс, подтверждающий возможность доступа к локальной шине. В следующем такте МП переводит шины адреса/данных и управления в z – состояние и отключается от канала. По окончании работы с каналом устройство выдает в ту же линию 3-й импульс, указывающий на окончание захвата канала. В следующем такте МП восстанавливает управление шиной и продолжает вычисления. Все 3-и импульса имеют одинаковую продолжительность и низкий активный уровень. Сигналы на линиях не зависимы, но при одновременном поступлении запросов линия RQ/GT0 имеет больший приоритет. Эти линии используются для установления режима захвата шин и эквивалентных линиям HOLD-HLDA.

Организация памяти 16-разрядного МП

Память – массив емкостью 1 Мбайт = 2^20, 8-разрядных ячеек. В памяти хранятся байты и 16-разрядные слова. Слова располагаются в следующих ячейках памяти: старший байт – в ячейке со старшим адресом. Адрес слова – адрес младшего байта.

Организация памяти, при которой каждому адресу соответствует содержимое одной ячейки памяти, называется линейной.

В МП i8086 используется сегментная организация памяти, характеризующаяся тем, что программно доступной является не вся память, а лишь некоторые ее сегменты, внутри которой используется линейная адресация.

Введение сегментной организации можно объяснить следующим образом. МП i8086 имеет 16-разрядный регистр и сумматор, 16-разрядную внутреннюю шину. Стремление разработчиков адресовать большой массив памяти обусловлено 20ти разрядной ША.

Программная модель i8086

Состоит из РОН, сегментных регистров, IP и регистров флага.

РОН делятся на: регистры данных и регистры указателей.

|

Регистры данных |

Регистры указатели |

|||

|

|

15…8 |

7…0 |

|

15…8 |

|

AX |

АH |

AL |

SP |

|

|

BX |

BH |

BL |

BP |

|

|

CX |

CH |

CL |

SI |

|

|

DX |

DH |

DL |

DI |

|

|

Сегменты данных |

|

Указатель команд |

|

15…0 |

15…0 |

|

|

CS |

IP |

|

|

DS |

Регистр флагов |

|

|

SS |

15…0 |

|

|

ES |

X/X/X/X/OF/DF/IF/TF/ST/ZF/X/AF/X/PF/X/CF |

OF-11; SP – указатель стека

DF=10; BP – базовый регистр

IF-9; SI – индекс источника

TF-8; DI – индекс назначения

SF-7; CS – сегмент кодов

ZF-6; DS – сегмент данных

AF-4; SS – сегмент стека

PF-2; ES – дополнительный сегмент данных

CF-0;

РОН делятся на регистры данных и указателя . К регистрам данных относятся 4е 16ти разрядные регистры, любой из которых состоит из 2х-8ми разрядных регистров, которые можно независимо адресовать символическими именами AH, BH, CH, DH соответственно AL, BL, CL, DL, регистры указателей 16ти разрядны и предназначены для хранения адресов операндов при косвенной адресации. Все РОН можно использовать для хранения данных, но в некоторых командах допускается использование определенного регистра по умолчанию.

AX – при умножении и делении, в воде и выводе слов (16разрядов);

AL – умножение-деление, ввод-вывод байтов, десятичной коррекции;

AH – умножение-деление битов;

BX – используется при трансляции;

CX – счетчик циклов и указатель длины слов в строчных командах;

CL – хранение числа сдвигов в командах;

DX – умножение и деление слов, ввод и вывод с косвенной адресацией;

SP – операции со стеком;

SI/DI – при строковых операциях.

В отличии от 8ми разрядного МП в регистре SP хранится смещение последней занятой ячейки стека, а полный адрес стека определяется SS:SP. Сегментных регистры определяют начальные адреса 4х сегментов памяти в зависимости от типа обращения к памяти (выборка команд, адресация переменной, стековые операции и т.д.).

Регистр флагов хранит признаки результата выполнения арифметических и логических операций и управляющие признаки, которые можно установить и сбросить программно.

AF – флаг вспомогательного переноса или заема из младшей тетрады в старшую из разряда F3 в F4, используется в командах обработки двоично-десятичных чисел.

CF – флаг переноса или заема устанавливается (1) при выходе результата суммирования (вычитания) без знаковых операндов за границу диапазона. В командах сдвига фиксирует значение старшего бита.

OF – флаг переполнения устанавливается при выходе знакового результата за границу диапазона.

CF – флаг знаки. Для положительных чисел CF=0, для отрицательных CF=1.

PF – флаг четности, устанавливается при четном количестве единиц в результате операции.

ZF – флаг результата = 0. Устанавливается при 0ом результате операции.

DF – флаг управления направлением обработки массивов данных в строковых командах. При DF=1 индексные регистры SI и DI, которые принимают участие в строковых командах автоматически декрементируются, а при DF=0 инкрементируются.

IF – флаг разрешения прерывания IF=1, разрешается выполнение маскированных аппаратных прерываний.

TF – флаг трассировки (пошагового режима) при его установке после выполнения каждой команды вызывается внутреннее прерывание.

Для формирования 20ти разрядного адреса в 16ти разрядном процессоре используют информацию 2х-16ти разрядных регистров.

В МП i8086 20ти разрядный адрес формируется из 2х-16ти разрядных адресов, которые называются логическими. Первый логический адрес 16ти разрядный, заполненный 0000 представляет собой начальный адрес сегмента емкостью 64 Кбайта.

Второй логический адрес определяет смещение в сегменте, т.е. расстояние от начала сегмента до адресованной ячейки, если это расстояние = 0000, то адресуется первая ячейка сегмента, т.о. логическое адресное пространство разделено на блоки соседних адресов емкостью 64 Кбайта.

Получают 20ти разрядный физический адрес.

Пример:

Сегментный подход к организации памяти удобен еще и потому, что память обычно логически делится на области кода (программная память) данных и стека.

Физический 20ти разрядный адрес ячейки памяти формирется из 2х-16ти разрядных адресов: адреса сегмента (seg) и исполнительного адреса (смещение EA), которые суммируются со смещение на 4 разряда влево.

Смещение адреса сегмента на 4 разряда влево эквивалентно уменьшению на 2^4, т.е. физический адрес: 16*Seg+EA.

В качестве первого логического адреса сегмента используется содержимое одного из 4х сегментных регистров: CS, SS, DS, ES.

CS: Второй логический адрес EA зависит от сегмента, так в сегменте кодов используется содержимое указателя команд (CS, IP). В сегменте данных значение EA зависит от средства адресации операнда. В сегменте стека для указания 2го логического адреса используется содержимое (SS:SP, SS:BP).

Преобразованиелогических адресов в физические всегда однозначно, т.е. в паре сегмент: EA соответствует единственный адрес.

Обратное преобразование не является однозначным. Физический адрес можно использовать: 64Кб/16=4086

Адресация портов ввода-вывода 16ти разрядного МП

Пространство адресов портов ввода-вывода не сегментировано, занимает 64кБ и адресация 16 младшими разрядами 20ти разрядной шины: адреса А19-А0, А15-А0.

Порты могут быть как 8 так и 16 разрядные, любые 2 смежных 8ми разрядных порта можно рассматривать как 1н 16ти разрядный, при этом для обмена с 8-ми разрядными портами используется регистр AL с 16ти разрядными AX

При выводе информации из 8ми разрядного порта с адресом 56H в регистр AL:

Чтобы передать информацию из 8ми разрядного порта с определенным адресом в аккумулятор AL можно выполнить ввод-вывод:

- 1й операнд команд 8ми разрядный аккумулятор;

- 2й операнд номер порта (56), получаем: IN AL,56H; AL<-P8(58H)

2. вывести информацию из регистра аккумулятора AX в 16ти разрядный порт с адресом с адресом 34H.

Чтобы вывести информацию из AX в 16ти разрядный порт надо выполнить команду вывода OUT.

Первый операнд команды номер порта 34H, аккумулятор AL если выводится байт инфы или AX если выводится слово, получаем: OUT 34H,AX; AX->P`16(34H)

3. Вывести информацию из 8ми разрядного порта с адресом, который содержится в регистре DX в регистр аккумулятор AL. Чтобы ввести информацию надо выполнить команду IN.

первый операнд – аккумулятор AL, второй регистр DX.

IN AL,DX; AL<-P`8(DX)

Содержимое регистра DX должно быть определено к моменту выполнения команды ввода.

Типы адресации операндов

В МП i8086 используется прямая, регистровая, непостредственная и косвенная адресация, что и для 8ми разрядных процессоров.

Косвенная адресация имеет 3 разновидности:

1. Базовая – эффективный адрес операнда (EA смещение), вычисляется суммрованием содержимого базовых регистров BX и PP, и смещения. В частном случае смещения может не быть.

Задача: Переслать в регистр аккумулятор AX содержимое ячейки памяти, которая расположена в сегменте данных и имеет эффективный адрес (смещение в сегменте FA) равный сумме содержимого регистра BX и 2000H.

Чтобы переслать содержимое ячейки памяти в аккумулятор надо использовать команду пересылки MOV dest,src

dest – операнд назначения (А<-B)

src – операнд-источник.

- пересылка данных из регистра ячейки памяти или пересылка непосредственного операнда к регистр или ячейку памяти.

Операндом назначения (dest) – регистр AX

Операнд источника информации – ячейка памяти (BX+2000H)

Т.о. MOV AX,[BX+2000H);

AX<-DS:[BX+2000H]

Перед использованием команды содержимое AX и DX должно быть определено.

2. Индексная адресация – качестве адреса смещения используется сумма содержимого индексных регистров (SI DI) и смещения в виде числа.

Переслать в регистр – аккумулятор AX содержимое ячейки памяти, расположенное в сегменте данных с эффективным адресом (смещение в сегменте) равным сумме содержимого регистра SI и числа 5000H.

Команда: MOV AX,[SI+5000H];

AX<-DS:[SI+5000H]

Содержимое DS и SI должно быть определено.

3. Базово – индексная адресация.

Эффективный адрес операнда EA равен сумме содержимого базовых регистров BX и BP, индексных регистров SI и DI и некоторого смещения, задаваемого в команде.

Переслать в регистр аккумулятор AX содержимое ячейки памяти, расположенное в сегменте данных и имеющее эффективный адрес равный сумме содержимого регистров SI и BX.

MOV AX,[SI+BX]; AX<-DS:[SI+BX].

Циклы шины процессора (машинные циклы)

На протяжении цикла шины МП выставляет адрес ячейки памяти или устройства ввода-вывода на шину адреса, формирует управляющие сигналы чтения-записи, а после этого считывает или записывает данные.

Кроме циклов чтение и запись в память у устройства ввода-вывода существует также циклы подтверждения прерывания и захват шины.

Цикл шины может инициировать не только независимый процессор i8086, но и арифметический сопроц или сопроц ввода-вывода.

Различают циклы в min и и max режимах.

Цикл шины состоит как min из 4х тактов. Такт определяется в данном случае как промежуток времени между задними фронтаим двух соседних импульсов сигналов тока F1 и CLK.

Любой цикл шины может быть растянут с помощью сигнала готовности READY, при этом МП выполняет такты ожидания Tw.

Цикл обращения к портам отличается от циклов обращения к памяти тем, что старшиме разряды шины адреса имеют нулевое значение. При косвенной адресации с помощью DX сигналы на линиях А19-А16 имеют L(0) уровень (косвенная).

При прямой адресации L-уровень приобретает А19-А8 (прямая)

На линиях в первом случае А15-А0, во втором случае (А7-А0) устанавливается адрес порта.

Типы прерываний i8086

Проц i8086 может обрабатывать до 256 типов прерываний. Каждому прерыванию соответствует свой вектор.

Двойное слово, которое содержит адрес CS:IP вызываемой плдпроги.

Подвекторы прерываний в общем пространстве памяти отводятся 1бит начиная с 0 адреса.

Карта векторов прерываний

При переходе к подпроге обработки прерывания INTn, где n – тип прерывания.

Проц перемещает в стек содержимое регистров IP и CS, регистра флагов F сбрасывает флаг разрешения прерывания, включает адрес 4×n, где n – тип прерывания.

Сброс флага IF не разрешает прерывать выполнение подпроги обработки прерывания до ее завершения или выполнение команды STI (разрешение выполнения маскируемых аппаратных прерываний). Последней командойподпроги обработки прерывания является команда IRET (возврат из подпроги прерывания).

По этой команде МП выбирает из стека адрес возврата (адрес команды, следующей за командой INT) и содержимое регистра флагов.

Типы прерываний

Прерывания делятся на внешние, аппаратные и внутренние.

Запросы прерываний IRQ внешних аппаратных прерываний поступают в систему прерывания или на линию не массированного прерывания NMI МП.

Система прерываний формирует сигнал INTR массированного прерывания МП.

Маскированное отличается от не маскированного тем, что первое может быть запрещено программно командой сброса флага разрешения прерывания INT. В этом случае при поступлении запросов прерывания они будут игнорироваться.

Внутреннее прерывание МП делят на программные и аппаратные.

Источниками внутренних программных прерываний являются:

Тип 0 – ошибка деления.

Тип 1 – пошаговый режим.

INT 0 (тип 4) – выполение прерывания 4 если флаг переполнения в регистре признаков OF=1.

Внутренние программные прерывания INTn INT3 выполняются по команде прерывания и разрешают вызывать подпрогу обработки прерывания без применения вызовов подпрог.

В отличии от INTn прерывание INT3 является однобайтной командой и используется для передачи управления подпроге-отладчику.

Внутреннее аппаратное прерывание возникает:

- при делении на 0.

- при установленном флаге трассировки TF; в этом случае прерывание происходит после выполнения каждой команды.

- после команды INT0, если установлен флаг переполнения 0F.

Аппаратное прерывание возникает при активном уровне сигналов на выводах NMI - немаскируемые прерывания (тип2), и команды INTR – маскированное прерывание (тип5-255).

Маскированное прерывание выполняется при установленном флаге IF (разрешение прерываний).

При переходе к подпроге обработки аппаратного прерывания проц последовательно формирует 2 цикла подтверждения прерывания в которых генерируется сигнал INTA (сигнал подтверждения прерывания) после 2го импульса этого сигнала контроллер прерываний передает по шине данных номер вектора прерываний.

Система команд i8086

Содержит 91 мнемокод. Команды можно разделить на 5 групп:

1. команды передачи информации (пересылка, работа со стеком, команды ввода-вывода).

н/п: MOV dest,src

dest – операнд назначения

src – операнд-источник

2. команды обработки информации (арифметические, логические, сдвига)

DAA – команда десятичной коррекции

INC r/m

r – регистр; m – память.

3. строковые команды

REP MOV SW (повторить пересылку слов)

4. команды передачи управления.

Выполняют команды прерывания.

JNC – переход если не перенос; если CF=0

JC – альтернатива

JMP – безусловный переход

LOOP target (метка) – переход на метку

5. управление состоянием МП

WATT – ожидание (сигнала 1 на TEST)

HLT – останов

NOP – пустая операция (нет операций)

Отличие МП i8088 от i8086

Отличие заключается в том что i8088 имеет внешнюю шину данных 8ми разрядную при внутренней 16ти разрядной. Уменьшение разрядности ШД упрощает построение блоков памяти и связи с внешними устройствами, но производительность падает на 20-30%.

Структуры МП аналогичны, но длина очереди команд сокращена до 4х байт. С программной точки зрения идентичны, система команд и набор регистров одинаковы.

Так же как и i8086, i8088 выполняет 8ми и 16ти разрядные операции, арифметические и логические включая умножение и деление, операции со троками поддерживают режимы прерывания ПДП, операции с портами.

Расположение и назначение выводов совпадает но i8088 АД15-АД8 используется только для адреса, а линия BHE заменена линией состояния ST0.

Сигналы DT/R, IO/M, ST0 могут использоваться для идентификации цикла шины. Более поздние классы МП i80196 (80198) программно совместимы с i8086.

ША 20ти разрядны, внешние и внутренние шины данных 8ми и 16ти разрядны. Эти процы имеют встроенные переферийные контроллеры прерываний ПДП, 3х канальный таймер и тактовый генератор.

А следующие классы i80c186 (80c188) имеют средства управления энергопотреблением, кроме того есть модификации со встроенным последовательным портом HART и контроллерами динамической памяти.