-

Техническое задание

1.2 Назначение и краткая характеристика разрабатываемого устройства

Устройство преобразователя параметров датчиков распределителей зажигания предназначено для измерений параметров датчиков зажигания с применением КР580ВИ53 для случая многоимпульсного датчика частоты вращения, сигналом которого квантуются соответствующие временные интервалы датчика зажигания.

Задача устройства – преобразователя реализующий квантование постоянной частотой, т.е. не требующий сложного многоимпульсного датчика.

Технические характеристики устройства

Питание 12 В постоянного тока

РАЗРАБОТКА

СХЕМЫ ЭЛЕКТРИЧЕСКОЙ ПРИНЦИПИАЛЬНОЙ

УСТРОЙСТВА ПРЕОБРАЗОВАТЕЛЯ ПАРАМЕТРОВ

ДАТЧИКОВ РАСПРЕДЕЛИТЕЛЕЙ ЗАЖИГАНИЯ.

РАЗРАБОТКА

СХЕМЫ ЭЛЕКТРИЧЕСКОЙ ПРИНЦИПИАЛЬНОЙ

УСТРОЙСТВА ПРЕОБРАЗОВАТЕЛЯ ПАРАМЕТРОВ

ДАТЧИКОВ РАСПРЕДЕЛИТЕЛЕЙ ЗАЖИГАНИЯ.

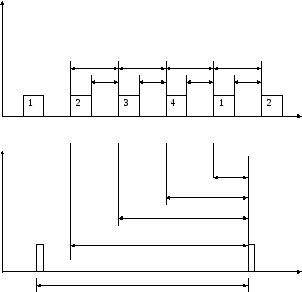

Краткое описание принципа работы преобразователя параметров датчиков распределителей зажигания сводится к измерению время – импульсных характеристик (рис. 1) и последующим вычислениям.

Измерение характеристик датчиков распределителей зажигания организовываем программно во внутренних регистрах микропроцессора. Однако при этом требуется аппаратная идентификация номера импульса датчиков распределителей зажигания, долговременная стабильность частоты вращения и значительное время для осуществления контроля. Поэтому я предлагаю аппаратное решение задачи с применением КР580ВИ53.

D3

D3

T23 T34 T41 T32

T2 T3 T4 T1

t2 t3 t4 t5 t6 t7 t8 t9 t

DП

![]() 1

1

![]() 4

4

![]() 3

3

![]() 2

2

t1

T

t10

t![]()

На этапе загрузки производятся настройка каналов КР580ВИ53 на режим программируемой задержки (режим 0) и запись в счетчики каналов начальных значений .

Операции загрузки КР580ВИ53.

Таблица 1.

|

Операции |

Данные |

Изменяемая часть А3…А7 адреса |

|

Управляющее слово канала 0 и сброс первого триггера Управляющее слово канала 1 Управляющее слово канала 2 Младший байт канала 0 Старший байт канала 0 Младший байт канала 1 Старший байт канала 1 Младший байт канала 2 Старший байт канала 2 |

30Н 70Н В0Н FFH FFH FFH FFH FFH FFH |

ВН 3Н 3Н OH OH 1H 0H 2H 2H |

Процесс загрузки сопровождается формированием сигнала ОТВ при совпадении неизменяемой части адреса А7…А4 с настройкой дешифратора.

По окончании загрузки начинается собственно измерение временных интервалов. Операции обмена на этом перечислены в таблице 2.

Процесс измерения заключается в следующем. После запуска D – триггер подготавливается к срабатыванию и при подаче импульса DП устанавливается в единичное состояние. При этом открываются оба ключа и квантующая частота fкв поступает на входы CLK всех трех каналов КР580ВИ53 на вход GATE канала 0 поступают временные интервалы Тij – Ti, на вход GATE канала 1 –временные интервалы Ti (время замкнутого состояния контактов), а также первый t2 – t1 и последний t10 – t9 интервалы, на вход GATE канала 2 –интервал Т. Процессы квантования временных интервалов и чтения результатов в каналах hgghhhhhgjjhjkkkllll;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

Таблица 2.

|

Операции |

Изменяемая часть А3….А0 адреса |

|

Запуск Младший байт канала 0 Старший байт канала 0 Младший байт канала 1 Старший байт канала 1 Младший байт канала 2 Старший байт канала 2 |

7Н 0Н 0Н 1А 1А 2Н 2Н |

0 и 1 чередуются, т.е. при квантовании в канале 0 из канала 1 осуществляется чтение и наоборот. Эти процессы управляются с помощью импульсов запроса прерывания ЗПРО по фронтам и срезам сигналов второго ключа и инверсного выхода D – триггера. Наличие сигнала ЗПРО интерпретируется МП, как необходимость чтения из соответствующего канала (0 или 1) с последующей записью в этот канал начального значения (FFFFH).

Выходы каналов OUT0…OUT2 объединены элементом ИЛИ с целью формирования сигнала ЗПР1, свидетельствующего о переполнении одного из каналов, т.е. о несоответствии уровня fкв квантуемому временному интервалу (аварийный останов).

Длительность этапа измерений равна Т и завершается вторым импульсом DП (момент t10), который устанавливает D – триггер в импульное состояние. На линии ЗПРО формируется десятый по счету импульс. В ответ МП выставляет на линии А3 Лог.0. устанавливая R, S и D – триггеры в нулевое состояние. По окончании этапа в ОЗУ хранится информация табл. 3.

Таблица

3.

Таблица

3.

|

Адрес ячейки ОЗУ |

Код |

Адрес ячейки ОЗУ |

Код |

|

4003Н,4004Н

4005Н,4006Н

4007Н,4008Н

4009Н,400АН

400ВН,400СН |

(t2 – t1) fкв

(t3 – t2) fкв

(t4 – t3) fкв

(t5 – t4) fкв

(t6 – t5) fкв |

400DH 400EH 400FH 4010H 4011H 4012H 4013H 4014H 4015H 4016H |

(t7 – t6) fкв

(t8 – t7) fкв

(t9 – t8) fкв

(t10 – t9) fкв

(t10 – t1) fкв |

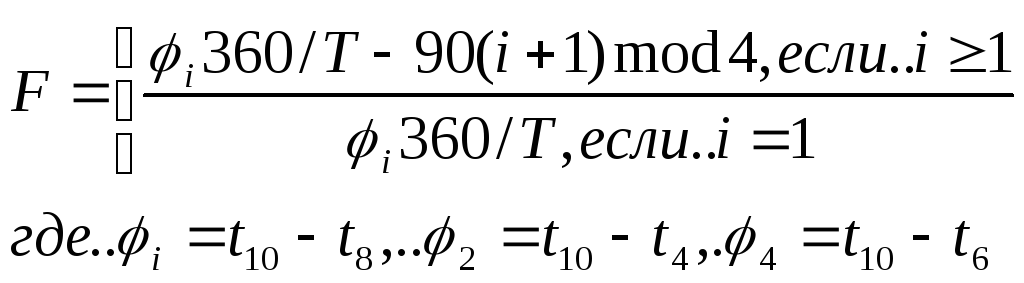

На третьем этапе МП вычисляет угловые характеристики датчиков распределителей зажигания табл. 4.

Таблица 4

|

Характеристика |

Алгоритм вычисления |

|

Асинхронизм

Угол замкнутого состояния контактов

Угол опережения зажигания

|

Aij=Tij360/T-90, где T12=T-T23-T34-T41, T23=t4-t2, T34=t6-t4, T41=t8-t6, T=t10-t1 U1=360Ti/T, где T1=T12-t9+t8, T2=t4-t3, T3=t6-t5, T4=t8-t7

|

3

ОБОСНОВАНИЕ ВЫБОРА МИКРОПРОЦЕССОРА

3

ОБОСНОВАНИЕ ВЫБОРА МИКРОПРОЦЕССОРА

Выделим основные критерии выбора микроконтроллера для данного устройства.

- 8-разрядное ЦПУ, оптимизированное для функций управления

- расширенные возможности по-битовой обработки

- встроенная Flash память программ

- встроенное ОЗУ данных

- двунаправленные индивидуально адресуемые линии ввода/вывода

- встроенные 16-разрядные таймеры/счетчики событий

- полный дуплексный UART

- несколько источников прерываний с несколькими уровнями приоритета

- встроенное ЭСППЗУ

- интерфейс последовательной шины SPI

- сторожевой таймер - пассивный (idle) и стоповый (power doun) режимы

- возможность расширения внешнего ОЗУ и ПЗУ до 64 Кбайт

- режим внутрисхемной эмуляции

Напряжение питания, В – 5,5

Тактовая частота, МГц – 4

В активном режиме микроконтроллеры на частоте 12 МГц потребляют порядка 25 мА и в пассивном режиме, при котором остановлено ЦПУ но система прерываний, ОЗУ, таймеры/счетчики событий и последовательный порт, остаются активными, потребление снижается до 15% от потребления в активном режиме. В стоповом режиме потребление не превышает 100 мкА.

EEPROM память данных организована как отдельное пространство данных с возможность считывания и записи отдельного байта. EEPROM обеспечивает 100000 циклов стирания/записи. Взаимодействие между EEPROM и CPU определяется регистром адреса EEPROM, регистром данных EEPROM и регистром управления EEPROM.

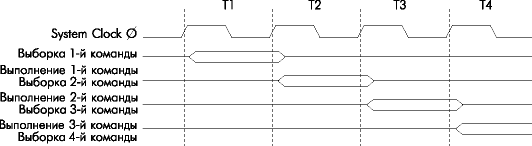

На Рисунке 1 представлен процесс параллельных выборки и выполнения команд, обеспечиваемые Гарвардской архитектурой, и концепция регистрового файла быстрого доступа. Это базовый принцип конвейерной обработки, обеспечивающий удельную производительность 1 MIPS/МГц при соответствующих результатах стоимости функции, количества функций на один такт и количества функций на единицу потребляемой мощности.

Р исунок

1 Параллельные выборка и выполнение

команд

исунок

1 Параллельные выборка и выполнение

команд

На рисунке 2 представлен принцип внутреннего тактирования регистрового файла. В течение одного тактового цикла выполнения операции ALU использует два операнда и результат возвращает в регистр назначения.

Р

Р исунок

2 Одноцикловая работа ALU.

исунок

2 Одноцикловая работа ALU.

На Рисунке 3 показано обращение к встроенной SRAM данных за два тактовых цикла

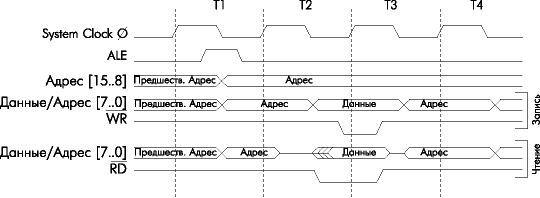

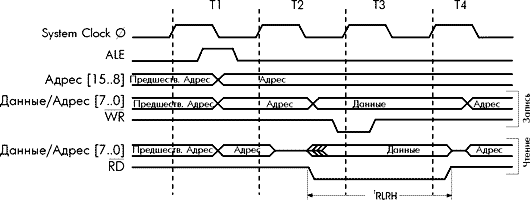

Рисунок 4 Циклы обращения к внешней SRAM данных без состояния ожидания (Wait State)

Система команд микропроцессора КР580ВИ53

Данные в микропроцессоре представлены в виде 8-разрядных кодов. Для идентификации отдельных разрядов в байте они нумеруются от D0 до D7 и считаются расположенными справа налево. При этом нулевой бит 0 соответствует младшему разряду, а D7 – старшему разряду. Однобайтовый код может рассматриваться либо как положительное целое число с диапазоном значений от 0 до 255, либо как целое число с диапазоном значений от -128 до +127. Для целых чисел используются двухбайтное и многобайтное представления [12].

Форматы команд

могут быть одно-, двух- или трехбайтными

(рисунок 6). Многобайтная команда

должна размещаться в последовательно

расположен ных

ячейках памяти, а в первом байте команды

В1 всегда указывается код операции.

ных

ячейках памяти, а в первом байте команды

В1 всегда указывается код операции.

Рисунок 6 – Форматы команд

Для управления процессом выполнения программы используется слово-состояние программы, формат которого представлен на рисунке 6, г. Старший байт слова-состояния составляет содержимое аккумулятора, а младший – содержит флаги условий регистра признаков, определяемые результатом выполнения арифметических и логических операций. Установка флагов производится при выполнении следующих условий:

-

флаг знака S, если знаковый бит результата операции равен 1, иначе

сбрасывается;

-

флаг нуля Z, если результат операции равен 0, в противном случае

сбрасывается;

-

флаг дополнительного переноса АС при наличии переноса из третьего

разряда, иначе сбрасывается;

-

флаг четности P, если результат содержит четное число единиц, иначе

сбрасывается;

-

флаг

переноса CY

при наличии переноса (при сложении) или

заема

флаг

переноса CY

при наличии переноса (при сложении) или

заема

(при вычитании) из старшего разряда результата, иначе сбрасывается.

В микропроцессоре используются пять способов адресации данных:

-

прямая – адрес М ячейки памяти, где расположен операнд, указывается

во втором (младшая часть адреса) и в третьем (старшая часть адреса)

байтах команды;

-

регистровая – в команде задается адрес оперативного регистра или

пары регистров, где находится соответственно 8- или 16-битовый

операнд;

-

регистровая косвенная – адрес М ячейки памяти, где расположен

операнд, определяется содержимым парного регистра, явно или неявно

указанного в команде; при этом старший байт адреса находится в

первом регистре пары, а младший – во втором;

-

непосредственная - операнд содержится в команде: для двухбайтовых

команд – во втором байте, для трехбайтовых – во втором (младшая

часть операнда) и в третьем (старшая часть операнда) байтах команды;

-

стековая – адрес ячейки памяти, содержащей операнд, находится в

указателе стека [10].

Специфический способ адресации памяти используется в однобайтовой команде, применяемой при обработке прерываний для вызова одной из восьми подпрограмм обслуживания прерываний. Команды RST различаются по номеру N, задаваемому в трехбайтовом поле кода команды. В результате выполнения команды RSTN управление передается по адресу, определяемому восьмикратным увеличением N.

По

функциональному признаку команды

микропроцессора делятся на пять групп

[6]:

По

функциональному признаку команды

микропроцессора делятся на пять групп

[6]:

-

команды передачи данных из регистра в регистр или память и из памяти в регистр;

-

арифметические команды: сложения, вычитания, инкремента, декремента;

-

логические команды: И, ИЛИ, исключающее ИЛИ, сравнение, сдвиг, инвертирование;

-

команды передачи управления и обработки подпрограмм;

-

команды ввода/ вывода и управления состоянием процессора.

Система команд микропроцессора содержит 78 команд, включающих 111 операций. Кодировка одиночных и парных адресов регистров микропроцессора, используемая при определении кодов команд, представлена в таблице 4.

Таблица 4 – Кодировка адресов регистров БИС КР580ИК80А

|

Регистр R |

Код SSS или DDD |

Регистр R |

Код SSS или DDD |

Парный регистр RP |

Код RR |

|

B C D E |

000 001 010 011 |

H L M A |

100 101 110 111 |

B – C D – E H – L S – P |

00 01 10 11 |

Основные временные параметры микропроцессора КР580ВИ53

Время выполнения команды микропроцессора зависит от типа команды и составляет от одного до пяти машинных циклов (М). Длительность машинного цикла может составлять от трех до пяти машинных тактов (Ti). Длительность машинного такта равна периоду тактовой частоты, задаваемой частотой фаз

СLK1, СLK2 генератора тактов.

Операции, выполняемые

микропроцессором в машинном цикле,

определяются 8-разрядной информацией,

характеризующей состояние внутренних

узлов микропроцессора. Этот байт

состояния называется также словом

состояния процессора и выдается на шину

данных микропроцессора в такте Т2 каждого

машинного цикла. Байт состояния может

использоваться для формирования

управляющих сигналов обращения к ЗУ,

УВВ, а также при организации различных

режимов работы микропроцессорной

системы [5].