курсовой проект / НА БАЗЕ МИКРОПРОЦЕССОРА К1810ВМ86 / Сканированные мп

.doc3.2. Архитектура и режим раб ты микропроцессора К1810ВМ86

БИС К1810ВМ86

однокристальный

тельный 16 - разрядный

выполненный I

канальной Ч< по усовершенствованной '

щей получить среднее время задержки

распространения i

2 не и обеспечить высокую функциональность

плотность

Основными | архитектурными

особенностями микросхемы К1810ВМ86, I

отличающими ее от микросхемы КР580ИА8ОА и позволяющими больше чем на порядок повысить производительность систем, являются:

1) более мощная система команд с расширенными возможностями адресации памяти, включающая команды уmhoжения, .деления и обработки последовательностей байтов или слов:

2| аппаратная реализация процесса совмещения операции выполнения и выборки команд;

3) более гибкая и мощная организация системы прерываний:

4) аппаратная реализация некоторых механизмов взаимодействия нескольких процессоров, упрощающая построение сложных мультипроцессорных систем.

Основные системные характеристики микропроцессора К1810ВМ86

Тактовая частота. МПц..... 5

Объем адресуемой памяти. Mбайт 1

Разрядность адресной шины . . . 20|

» шины ..ut!:M!,i:-..... i6

Число адресуемых устройств:

ввода/вывода........ \v,

основных команд.......

Максимальная потребляемая мощ-

тиГкорпус'а: : : : '. '. • • гт:*м,<п

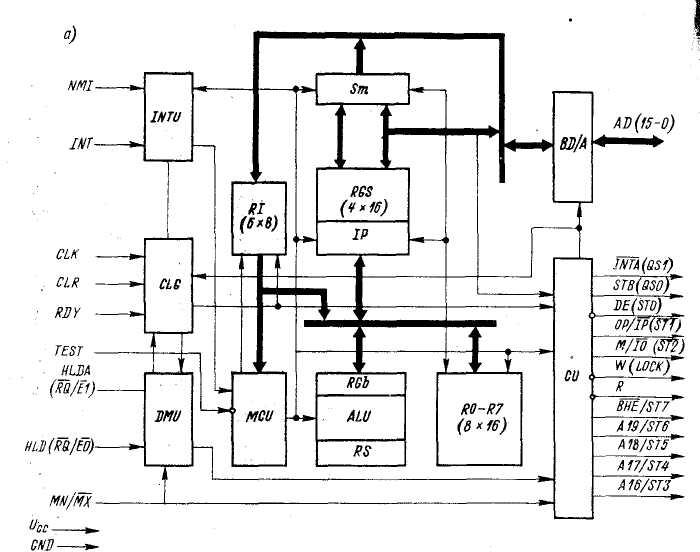

Структурная схема микропроцессора К1810ВМ86 представлена на рис. 3.1 а, она включает следующие устройства [2, У]- арифметико-логическое устройство \XlV) с тремя регистрами временного хранения операндов (RGB) и регистром признаков (RS); группу регистров общего назначения (R0 - R7); микропрограммное устройство управления (MCV) для упра-впения выполнением команд; схему управления доступом к магистрали (DMU); схему внутренней синхронизации (CLG), преобразующую внешние тактовые импульсы во внутренние последовательности синхроимпульсов и обеспечивающую синхронизацию МП с медленными ЗУ и УВВ; схему обработки запросов прерываний (INTU); схему управления циклами обмена (С С), осуществляющую управление работой 16-разрядного канала адреса/данных; буферы канала адреса/ цанных (BD/A); указатель команд (IP), выполняющий функции программного счетчика; сегментные регистры (RGS), содержащие базовые адреса программ, данных и стека; сумматор адреса (Sm), служащий для вычисления 20-разрядного физического адреса; регистры очереди команд (RI), предназначенные для формирования шестибайтной очереди команд, готовых к исполнению.

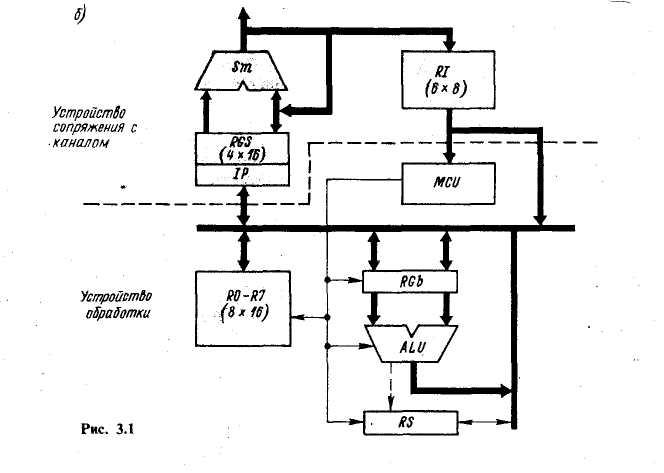

Отличительной особенностью архи-.тектуры микропроцессора К181ОВМ86 является наличие двух основных асинхронно работающих устройств: устройства обработки (УО) и устройства сопряжения канала (УСК). Упрощенная структурная схема, представляющая МП в виде двух независимых устройств, изображена на рис. 3.1,6. УО декодирует и выполняет команды, а УСК осуществляет связь с внешними устройствами, обеспечивает выборку команд и данных из памяти, формирует очередь команл Организация параллельной работы УО и УСК и уменьшение конфликтных ситуаций при обращении к памяти за счет применения очереди команд позволяет существенно повысить производитель-

ность систем на основе микропроцессора К181ОВМ86.

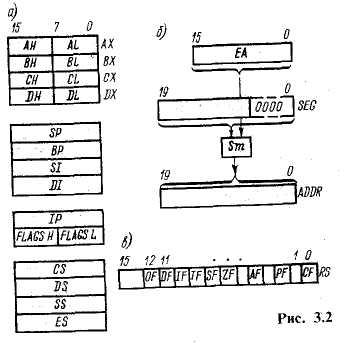

Регистровая модель микропроцессора К181ОВМ86 приведена на рис. 3.2, я. Регистры CS, DS, SS и ES называются сегментными регистрами и используются при обращении к памяти для вычисления

физических адресов ячеек. Основное назначение этих регистров следующее: регистр программного или кодового сегмента (CS) определяет текущий программный сегмент; содержимое регистра CS вместе с содержимым указателя команд (IP) задает адрес очередной команды выполняемой-программы; регистр сегмента данных, или информационного сегмента (DS), используется в командах при обращении к данным; регистр стекового сегмента (SS) определяет текущий стековый сегмент и используется в командах обращения к стеку, при обработке подпрограмм и прерывании; регистр дополнительного сегмента (ES) обычно применяется как вспомогательный сегмент данных.

Регистры общего назначения АХ, ВХ, СХ и DX, называемые также регистрами данных, используются при выполнении арифметических и логических операций. Эти же регистры могут выполнять некоторые специальные функции, что и нашло отражение в их мнемонических обозначениях- АХ - аккумулятор, ВХ - базовый регистр, СХ - счетчик. DX - регистр данных. Эти регистры общеп: .,:.-■: .•:.-■;;■<: допускают раздельную ллр ;

старшим (Я) и младшим (L) половинам и могут использоваться в виде набора 8-разрядных регистров.

Регистры общего назначения SP, ВР, SI и DI называются адресными регистрами, так как в них хранятся относительные адреса, используемые для определения адресов операндов в пределах одного из сегментов памяти. В указателе стека (SP) и в указателе базы (ВР) содержатся относительные адреса в пределах стекового сегмента памяти, а в регистре индекса источника (SI) и. регистре индекса приемника {DI) хранятся относительные адреса в пределах сегмента данных.

В пределах любого из сегментов емкостью в 64К байт обращение к операндам происходит с помощью 16-разрядного адреса смещения в сегменте. Этот адрес определяется способом адресации и называется также исполнительным адресом (ЕЛ). 20-разрядный физический адрес памяти (ADDR) формируется в сумматоре адреса (Sm) посредством сложения 16-разрядного адреса смещения в сегменте с 16-разрядным адресом в сегментном регистре, сдвинутым на четыре разряда влево (рис. 3.2,6).

Рассмотренные функции регистров микропроцессора К181ОВМ86 являются основными и реализуются в командах по умолчанию. Дополнительные возможности использования регистров указываются при описании конкретных видов команд.

Регистр признаков или флагов (RS) состоит из одноразрядных регистров, фиксирующих состояние процессора и применяемых для управления его функционированием (рис. 3.2, в). Флаги CF, PF, AF, SF и ZF аналогичны флагам микропроцессора КР580ИК80А и характеризуют результат выполнения последней арифметической или логической операции. Флаг переполнения OF устанавливается в состояние 1 при переполнении, возникающем в результате арифметических операций над величинами со знаком. Флаги DF, IF и TF применяются для управления микропроцессором. Флаг направления DF служит для автоматического увеличения или уменьшения адреса при обработке последовательностей символов (имитация режимов автоинкрементной

и автодекрементной адресации). Установка флага разрешения прерывания IF разрешает МП-прием запроса прерывания на входе INT. Установка флага трассировки TF переводит МП в состояние прерывания после выполнения каждой команды, т. е. организует режим пошагового выполнения программ.

Микропроцессор К1810ВМ86 предназначен для использования как в простых однопроцессорных, так и в сложных мультипроцессорных системах управления и обработки информации. В связи с этим МП имеет специальный вывод MN/MX (см. рис. 3.1, а) для задания минимального или максимального режимов функционирования. Каждый режим характеризуется некоторым набором управляющих сигналов, соответствующим сложности проектируемой системы. При подключении вывода MN/MX к выводу Uее микропроцессор настраивается на работу в минимальном режиме, в котором все сигналы управления периферийными устройствами вырабатываются самим МП. При подключении вывода MNIMX к выводу GND происходит изменение функций ряда управляющих сигналов и МП перенастраивается на работу в максимальном режиме. В этом режиме МП используется обычно с системным контроллером, генерирующим сигналы управления системой. Управляющие сигналы максимального режима работы на рис. 3.1, а заключены в круглые скобки.

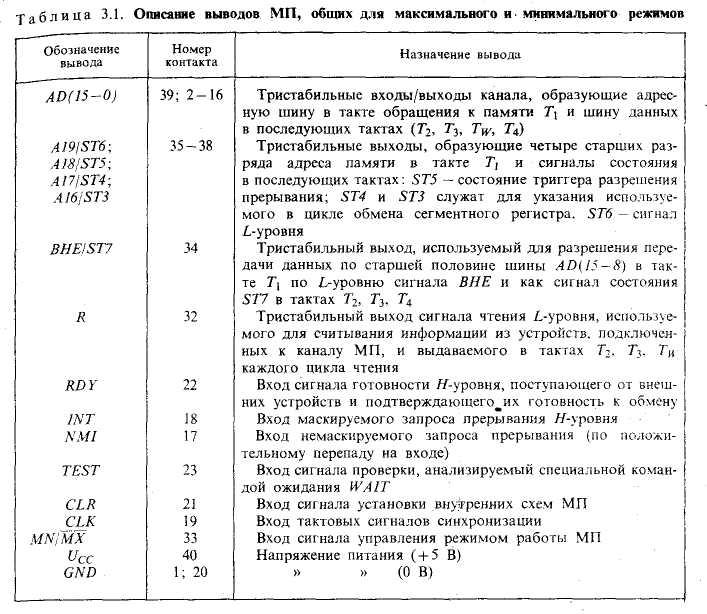

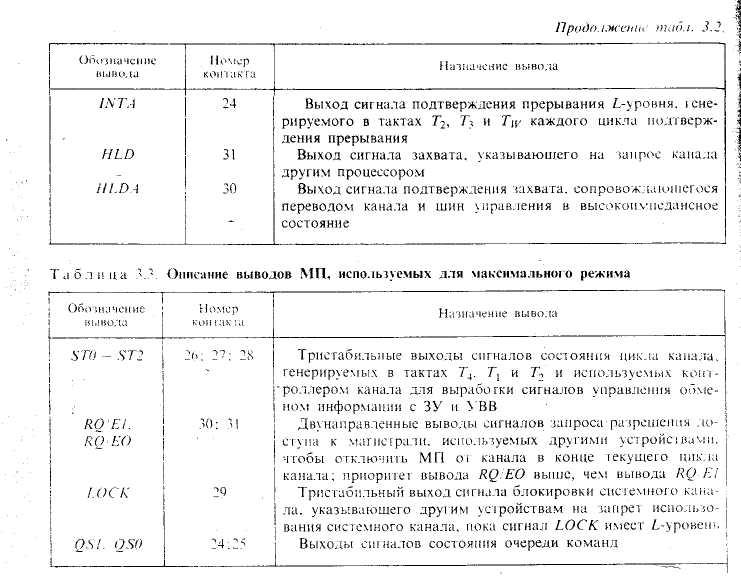

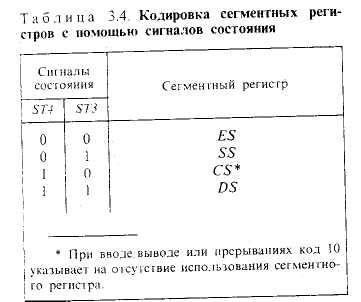

Назначения выводов МП и соответствующих им сигналов, общих как для максимального, так и для минимального режимов, приведены в табл. 3.1. Назначения выводов, относящиеся только к минимальному режиму, даны в табл. 3.2, а только к максимальному — в табл. 3.3. В максимальном режиме, как это видно из табл. 3.3, МП использует лишь три вывода ST0 — ST2 для управления периферией и ЗУ через контроллер, а на остальных пяти выводах генерируются сигналы, необходимые для организации работы МП в мультипроцессорных системах.

Микропроцессор К1810ВМ86 осуществляет обмен информацией с ЗУ и ВУ через 16-разрядный канал адреса/данных с помощью временного мультиплексирования. Цикл функционирования канала

включает обычно выдачу адресов ЗУ или УВВ. данных, а также сигналов, сопровождающих процесс обмена, и состоит из четырех машинных тактов (Tt. Г,. Т3. Г4). В такте Tv в канал выдается адрес ЗУ или

УВВ. Обмен данными для цикла записи происходит в тактах Т2. Г3. Т4. а для цикла чтения — в тактах Т3, Т4. Такт Т2 в цикле чтения используется тля переключения МП из режима записи в режп ■;

11тения. а канал переводится в высокоим-пелансное состояние. Для согласования с медленными УВВ или ЗУ с помощью сигнала RDY между тактами Т3 и Т4 могут включаться дополнительные такты ожидания (Ги), в течение которых данные в канале остаются неизменными. Наконец, в ряде случаев между отдельными циклами канала могут вводиться хо-юстые такты (Т5).

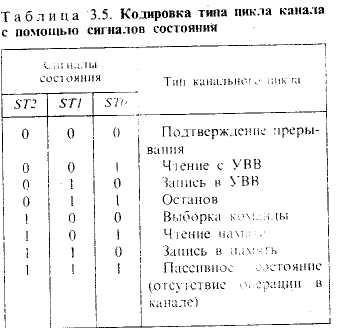

Временные диаграммы циклов чтения и записи для минимального режима приставлены на рис. 3.3. В цикле чтения [рис. j.j.ii) выдается сигнал чтения R, а также сигналы управления направлением обмена РО / 7Р и разрешением передачи данных DE. Сигнал DE разрешает шинным формирователям передать длимые в МП. В цикле записи (рис. 3.3,6) сигнал DE выдается раньше, чем в цикле чтения, а выдача данных и сигнала записи W производится по переднему фронту в такте Т2. Для многих ЗУ и УВВ тре-спетея постоянство адреса в течение всего цикла канала, поэтому в такте Т, каждого никла выдается стробирующий сигнал STB. позволяющий зафиксировать адрес по заднему фронту сигнала STB. Сигналы состояния ST3, ST4 указывают сегментный регистр, используемый в текущем цикле канала для вычисления физического адреса ячейки памяти, в соответствии с табл. 3.4. Определение типа

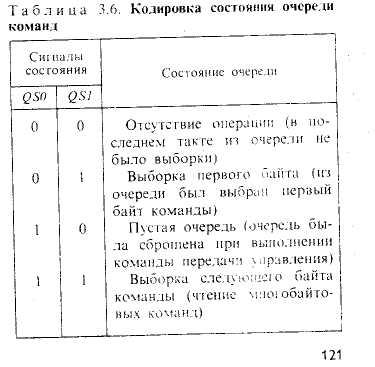

цикла канала для максимального режима с помошью сигналов ST2, ST1 и ST0 представлено в табл. 3.5. Назначение остальных сигналов состояния приведено в табл. 3.1.

Три 16-разрядных регистра очереди команд (ЯЛ микропроцессора обеспечивают временное хранение 6 бай г очереди команд (см. рис. 3.1.я). УО микропроцессора при выполнении команды извлекает из очереди байт кода команды, ме требуя доступа к каналу. УСК микропроцессора следит за состоянием очереди команд, пополняя се. когда apvi пе системные элементы не занимают память. При выполнении команд передачи управления очередь сбрасывается и после завершения перехода в место передачи управления начинает заполняться вновь. В максимальном режиме МП передает информацию о состоянии очереди на выходы OS0 и QSI. Эта информация используется внешними процессорами. Коды состояния очереди приведены в табл. 3.6.

конденсатора «5=1 мс. Поэтому для выдачи состояния низкого или высокого уровня сигнала на выходе БИС необходимо осуществлять периодическое восстановление информации (или се регенерацию) с периодом tREF ^ 1 -н 2 мс. Динамические микросхемы памяти строятся на основе биполярных МОП-транзисторов.

Модуль динамической памяти на МОП-структурах показан на рис. 14.5,». В основе запоминающего элемента лежат один конденсатор и один МОП-транзистор. На схеме конденсатор показан в виде отдельного элемента, хотя реально его функции выполняет емкость затвор-подложка.

Главные отличия динамических микросхем памяти от статических заключаются в следующем: отсутствует источник питания запоминающих ячеек; необходимы логические схемы, обеспечивающие регенерацию информации; обрамление требует более сложных схем; максимальная простота схемы накопителя для обеспечения минимально занимаемой площади; меньшая потребляемая мощность, поскольку динамический запоминающий элемент не потребляет тока, за исключением тех относительно коротких отрезков времени, когда к нему обращаются.

По способу организации регенерации информации динамические полупроводниковые ЗУ делятся на три вида: с пла-нарной регенерацией, с накачкой заряда, со строчной регенерацией [12].

Особенностью микросхем с планар-ной регенерацией является наличие усилителя считывания — регенерации в каждой запоминающей ячейке. Регенерация информации осуществляется в специальный цикл, так называемый цикл регенерации, повторяемый с частотой / = = 10 кГц, вне зависимости от режимов работы микросхемы. В этот цикл на микросхему подаются все сигналы, необходимые для работы при записи или считывании, кроме сигнала выборки. За цикл регенерации производится одновременно регенерация информации во всех ячейках памяти микросхемы. Если в течение времени регенерации к микросхеме памяти не было обращений, то для предотвращения потери информации должен быть сформирован служебный цикл обращения.

Отсчет времени периода регенерации может производиться, например, таймером pei енерации, запускаемым в момент отсутствия соответствующего импульса обращения. Недостатками микросхем с таким видом регенерации являются увеличение размера запоминающей ячейки и, как следствие, увеличение размеров кристалла и его стоимости.

Микросхемы с накачкой заряда, называемые иногда квазистатическими, имеют возможность одновременной регенерации информации во всех ячейках памяти с помощью специального импульса регенерации (накачки заряда), подаваемого обычно асинхронно на дополнительный вход микросхемы памяти с периодом регенерации tREF = 0,01 —0.1 мс.

Регенерация информации осуществляется по специальным цепям, что позволяет совмещать во времени подачу импульса регенерации с рабочими циклами обращения. Запоминающая ячейка в микросхемах этого типа имеет вид бистабиль-ного триггера, выполненного на четырех транзисторах и подключенного через ключи к шинам записи и считывания.

Микросхемы со строчной регенерацией содержат число усилителей считывания/записи, равное числу столбцов, и отличаются простотой выполнения запоминающей ячейки, которые состоят из трех транзисторов или одного. У однотран-зисторных микросхем памяти более сложный усилитель считывания, но размер кристалла существенно меньше, поскольку меньше размер ячейки памяти. Это позволяет иметь более высокий процент годных микросхем и более низкую их стоимость. Регенерация информации в микросхемах этого типа осуществляется формированием специального цикла регенерации, который, как правило, представляет собой либо цикл считывания по адресу регенерации, либо цикл записи по адресу регенерации с блокировкой записи.

В одном цикле регенерируют одновременно все ячейки памяти одной из строк памяти выбранного адреса. При изготовлении сверхбольших микросхем памяти используется последовательная адресация для сокращения числа выводов корпусов.

Вначале на адресные входы поступает адрес строки, запоминаемый в дополнительном регистре-фиксаторе, а затем

на те же входы подается адрес столбца, запоминаемый в другом регистре-фиксаторе. С регистров адресные коды поступают на адресные и разрядные формирователи.

ОЗУ динамического типа серии К565. Микросхемы серии К565 представляют собой оперативные запоминающие устройства с произвольной выборкой динамического типа, изготавливаются по л-ка-нальной МОП-технологии с кремниевыми затворами и двумя типами транзисторов (с индуцированным и встроенным каналом) и предназначены для построения накопителей ОЗУ большой емкости [11].

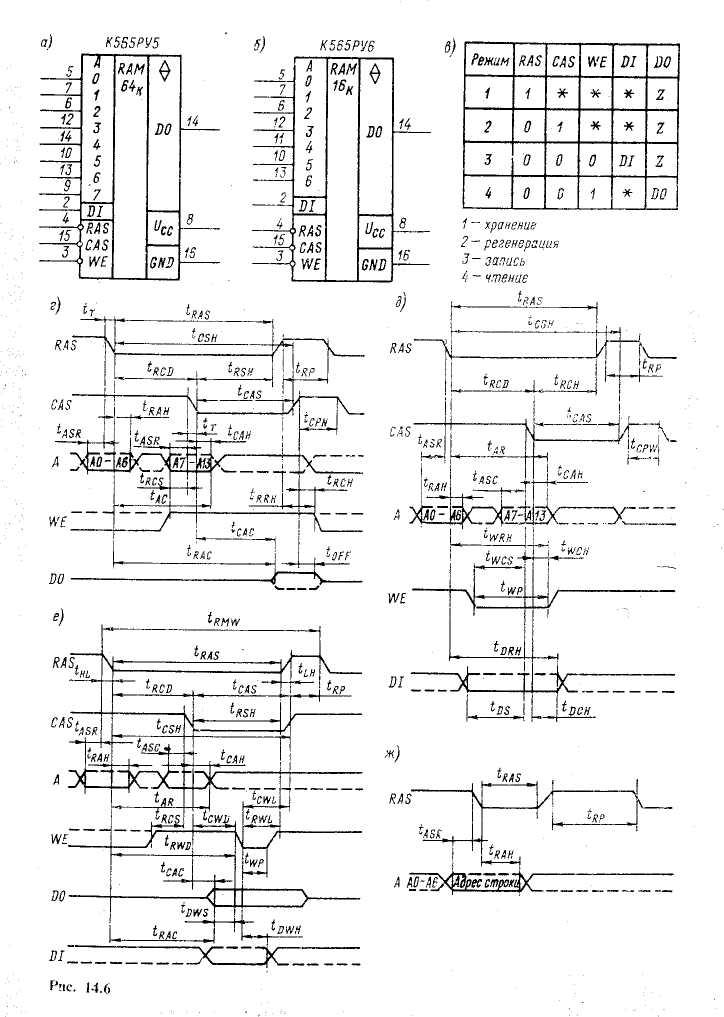

В состав серии входят: К565РУ5 (Б, В, Г, Д) емкостью 65 536 бит с организацией 65536x1 бит; К565РУ5 (Д1, Д2) емкостью 32 763 бит с организацией 32 768 х I бит; К565РУ5 (ДЗ, Д4) емкостью 16 384 бит с организацией 16 384 х 1 бит; КР565РУ6 (Б, В, Г, Д) емкостью 16 384 бит с организацией 16384 х 1 бит. Внешние сигналы: RAS — сигнал выбора адреса строк, С AS — сигнал выбора адреса столбцов, WE — сигнал записи/считывания, а также сигналы, вырабатываемые схемой управления, обеспечивают работу ОЗУ в режимах считывания, записи, постраничного считывания или постраничной записи, считывания-модификации-записи, регенерации по сигналу RAS.

Временные диаграммы работы микросхем в режимах считывания, записи. считывание — модификация — запись, регенерации приведены на рис. 14.6. г-ж. Это позволяет при работе в страничном режиме получить значительный выигрыш в быстродействии. Внутри страничного режима возможна любая комбинация режимов записи, считывания и считывание — модификация — запись.

Регенерация информации в динамических ячейках памяти осуществляется за 128 циклов путем обращения к каждой из 128 строк не ранее, чем через каждые 2 мс перебором адресов /1(0 — 6). Регенерация может быть осуществлена в ik>6on: из режимов ОЗУ, однако наиболее просто ее выполнить в режиме ра операции по сигналу RAS. когда сигнал CAS находится в неактивном высоком л;ч аческом состоянии (регенерация сигналом HAS). При регенерации в.этом режиме ;шегт место минимальная потребляемая мощность. При эксплуатации микросхем необходимо помнить, что после подачи" напряжения питания БИС ОЗУ переходит в нормальный режим функционирования через 2,0 мс и требует проведения j.-vrev, 16 рабочих циклов регенерации.

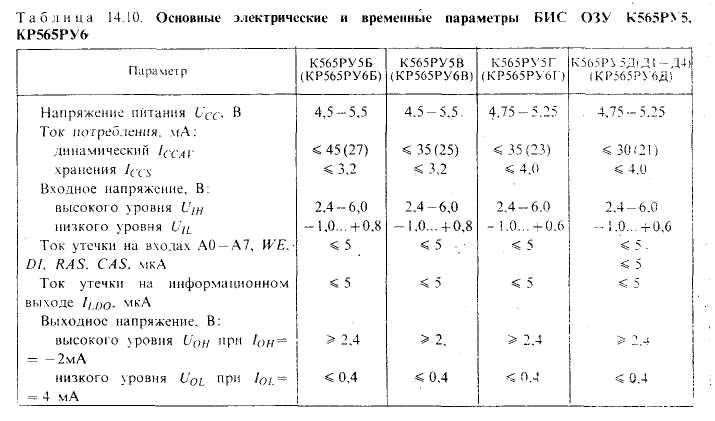

Основные электрические и временные параметры БИС ОЗУ К565РУ5. КР565РУ6 при температуре 25±!0:С приведены в табл. 14.10; условные графи-

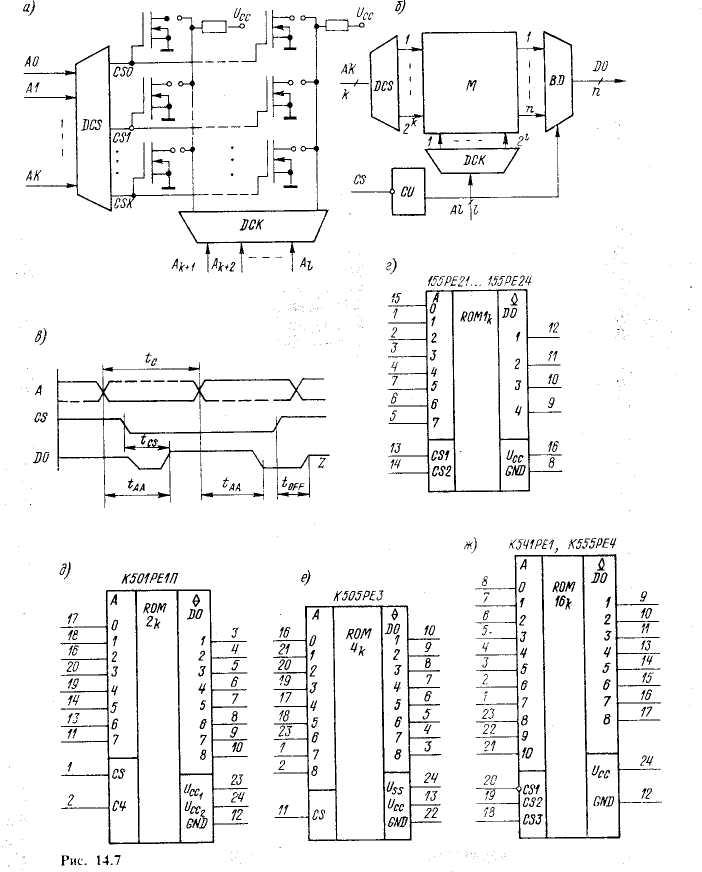

малой потребляемой мощностью. Организация масочного ПЗУ на МОП-транзисторах поясняется рис. 14.7, я.

Запоминающим элементом накопителя ПЗУ является один МОП-транзистор, выполняемый с тонким либо с толстым слоем под затвором в зависимости от того, какая информация должна храниться в данной ячейке.

Преимуществом ПЗУ, выполненных на биполярных транзисторах, является более высокое быстродействие по сравнению с ПЗУ па МОП-транзисторах. Запись информации в масочное ПЗУ производится с помощью сменного заказного фотошаблона. Документом, определяющим хранимую в накопителе информацию, является карта заказа на данную

микросхему. Изготовление маски довольно дорого, но с помощью одной маски можно запрограммировать любое число модулей памяти. Следовательно, масочные ПЗУ рентабельны при крупносерийном производстве.

Обобщенная логическая структура масочного ПЗУ приведена на рис, 14.7.6. В ее состав входят: дешифратор адреса строки (DCS); дешифратор адреса колонки (DCK); накопитель (М); устройство управления (СИ); буфер данных (BD).

Обобщенная временная диаграмма работы масочного ПЗУ приведена на рис. 14.7, в.

Масочные ПЗУ серии К155. Полупроводниковые интегральные микросхемы К155РЕ21, .... К155РЕ24. выполненные на основе транзисторно-транзисторной логики по планарно-эпитаксиальной технологии, представляют собой постоянные ЗУ емкостью 1024 биг для хранения и считывания информации в объеме 256 4-разрядных слов [5].

Все БИС по входам и выходам совместимы с ТТЛ-схемами и имеют выходы с открытым коллектором. Ниже приведено назначение БИС: К155РЕ21-ПЗУ на 1024 биг. преобразователь двоичного кода в код знаков русского алфавита; К155РЕ22 - ПЗУ на 1024 бит, преобразователь двоичного кода в код знаков латинского алфавита; К155РЕ23 — ПЗУ на 1024 бит, преобразователь двоичного кода в код арифметических знаков и цифр; К155РЕ24-ПЗУ на 1024 бит. преобразователь двоичного кода в код дополнительных знаков.

Условное обозначение и назначение выводов БИС приведены на рис. 14.7, г.

Основные электрические параметры БИС ПЗУ серии К155 при температуре 7„В = 25°С:

Напряжение питания Ucc, В . . . (5,0 + 0,25) В

Ток потребления 1Сс при Uее = 5,25 В, мА..... « 130

Выходное напряжение низкого уровня U0L при IOL = 12 мА, Ucc = 4,75 "в, В...... < 0,4

Выходной ток высокого уровня

1он при 6СС = 4,75 В, мкА < 100

Входное напряжение низкого уровня U,L при IIL = - 1 мА, 1'сс = 5,25 В, В...... «0,4

Входное напряжение высокого уровня 1]щ при 1щ = 40 мкА,

Ucc = 5.25 В, В...... 3= 2,4

Время выборки адреса tAA, не > 68

» выборки разрешения lcs, не > 30

» цикла считывания tc, не > 120

Входная емкость С/, пФ .... < 3

Выходная емкость Со, пФ ... < 5

Емкость нагрузки CL, пФ ... < 200

Масочные ПЗУ серии К501. Масочные ПЗУ серии К501РЕ1П, К501РЕ1, выполненные на основе МОП-технологии на р-канальных транзисторах, представляют собой ПЗУ емкостью 2048 бит для хранения и считывания информации в объеме 256 8-разрядных слов [15]. Масочные ПЗУ серии 50! несовместимы по входу и выходу с ТТЛ-схемами и требуют для согласования использования специальных элементов. Выходы БИС имеют три состояния.

Условное обозначение и назначение выводов БИС приведены на рис. 14.7,5.

Основные электрические параметры БИС ПЗУ серии К501 в диапазоне температур от —45 до 70 "С при Ь'Сс\ = = (-12) ±(+1,2) В, (Усс: = (-27) ± ±( + 2.7) В, RL= 1 МОм и С/.= 200 пФ: Ток потребления, мА:

по источнику C^ei ICci ■ ■ ■ < 22 ' по источнику иСс2 1сс2 ■ ■ ■ < 4,5 Выходное напряжение низкого уровня (j'ol, В.........< -1

Выходное напряжение высокого уровня U0lh В.........> - 10

Выходные токи низкого и высокого \ровней I0L, 1ОН, мкА ... ^50 Частота команды считывания /я,

кГц............«10

Время задержки команды считыва-вания относительно входа адреса

tRSA, мке..........> 2,0

Время считывания логического нуля

(д. мке..........> 4,0

Время считывания логической единицы lR, мке........^ 2,0

Время цикла считывания tc, мке > 6,0 Входная емкость С/7 пФ .... < 20 Выходная емкость Со. пФ .... < 11

Масочные ПЗУ серий К505, КР505.

Полупроводниковые интегральные микросхемы К5О5РЕЗ, КР5О5РЕЗ, выполненные на основе МОП-технологии на р-канальных транзисторах, представляют собой постоянные ЗУ емкостью 4096 бит

для хранения и считывания информации в объеме 512 8-разрядных слов [12]. Микросхемы К5О5РЕЗ, КР5О5РЕЗ могут быть нагружены и работать от сигналов ТТЛ ИС серии 155, причем каждый выход БИС ПЗУ может быть нагружен одним входом ИС вышеуказанной серии. Микросхемы ПЗУ на выходах имеют три состояния. Суммарная емкость монтажа, приведенная к одному адресному входу и входу CS, не должна превышать 50 пФ без учета входных емкостей самих БИС. Допускается объединять БИС по входам для увеличения разрядности и информационной емкости.

В настоящее время серийно выпускаются ПЗУ серии К505 со следующими прошивками: К5О5РЕЗ — 0002, К5О5РЕЗ - 0003 - генератор символов русского и латинского алфавитов, арифметические знаки и цифры, дополнительные знаки, 96 символов в формате 7x9, развертка по горизонтали (работают при совместном включении): К505РЕЗ-0004 - преобразователь кодов ДК0И8-К0И8; К5О5РЕЗ -0005 - преобразователь кодов КПК12 —ДК0И8; К5О5РЕ5-ОО1О - знакогенератор русского и латинского алфавитов, арифметические знаки и цифры, дополнительные знаки, 96 символов в формате 7x9, развертка знаков по вертикали; К5О5РЕЗ-0040...0049, К505РЕЗ-0О79-коэффициенты для быстрого преобразования ряда Фурье; К5О5РЕЗ-ОО51-функция (0 + 90) ° с дискретностью 10 мин ((9-12) разряды); К505РЕЗ-ОО52, К5О5РЕЗ - 0078 - функция sin (0-90)° с дискретностью 10 мин (1 — 8) разряды; К5О5РЕЗ -0059, К505РЕЗ -0060 - знакогенератор русского и латинского алфавитов, арифметические знаки и цифры, дополнительные знаки, 64 символа в формате 5x7, горизонтальная развертка знаков; К505РЕЗ-0063-0065 -знакогенератор русского и греческого алфавитов, арифметические знаки и цифры, дополнительные знаки, 256 знаков в формате 5x7, вертикальная развертка знаков; К5О5РЕЗ —0068 —функция sin (0 + 45)° (1 — 8 разряды t дискретностью 5'); К5О5РЕЗ-ОО69 -функция sin (0 + 45)° (9-16 разрядь с дискретностью 5'); К5О5РЕЗ-ОО7О-функция sin (45 + 90)° (1-8 разрядь

с дискретностью 5'); К5О5РЕЗ-ОО71 -функция sin (45 + 90)° (9-16 разряды с дискретностью 5'); К505РЕЗ-0О8О. К5О5РЕЗ-ОО81 -функция У= X2, где X изменяется от 1 до 128 (при совместном включении).

Условное обозначение и описание выводов БИС приведено на рис. 14.7. с.

Основные электрические параметры БИС ПЗУ серий К5О5. КР5О5 в диапазоне температур от —45 ( — 10 для КР) до

+ 70Х при С'сс = (-12)±(+ 1,2) В.

Ucc = {5±0,5) В:

Суммарный ток потребления 1(-с- МА:

при ТАТВ = 25"~С...... < 38

при ТАте= -10 С..... «54

при Т,7-в = 70°С...... «32

Выходное напряжение низкого уровня Uql при 1OL = 1.6 мА, В ... < 0.4 Выходное напряжение высокого

уровня иои при 1ОИ = 0.25 мА. В ■?■ 2,4 Выходной гок высокого уровня в

режиме хранения Iqh- мк'А . . . < 5,0 Входное напряжение низкого уровня UIL при I1L = 2,0 мкА, В .' . . < 0,2 Входное напряжение высокого уровня иш при 11Н = 2,0 мкА. В . . . > 2.5 Допустимое напряжение статической

помехи t'v. В........ < 0.2

Время выбора адреса .'.,_,. мке . . . >■ 1.3

» восстановления 'off* мкс * "■-