- •4.2 Схема тактирования и цикл выполнения команды

- •4.3 Организация памяти программ и стека

- •4.4 Организация памяти данных

- •4.5 Счетчик команд

- •4.6 Прямая и косвенная адресации

- •4.7 Порты ввода/вывода

- •4.8 Модуль таймера и регистр таймера

- •4.9 Память данных в рпзу (eeprom)

- •4.10 Организация прерываний

4.7 Порты ввода/вывода

Контроллеры PIC16F84 имеют два порта: PORTA (5 бит) и PORTB (8 бит) с побитовой индивидуальной настройкой на ввод или на вывод.

Порт A (PORTA) представляет собой 5-битовый фиксатор, соответствующий выводам контроллера RA<4:0>. Линия RA4 имеет вход триггера Шмит-та и выход с открытым стоком. Все остальные линии порта имеют ТТЛ входные уровни и КМОП выходные буферы. Адрес регистра порта А - 05h.

Каждой линии порта поставлен в соответствие бит направления передачи данных, который хранится в управляющем регистре TRISA, расположенном по адресу 85h. Если бит управляющего TRISA регистра имеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующего регистра-фиксатора порта. При включении питания все линии порта по умолчанию настроены на ввод.

Операция чтения порта А считывает состояние выводов порта, в то время как запись в него изменяет состояние триггеров порта. Все операции с портом являются операциями типа «чтение-модификация-запись». Поэтому запись в порт предполагает, что состояние выводов порта вначале считывается, затем модифицируется и записывается в триггер-фиксатор.

Порт В (PORTB) - это двунаправленный 8-битовый порт, соответствующий выводам RB<7:0> контроллера и расположенный по адресу 06h. Относящийся к порту В управляющий регистр TRISB расположен на первой странице регистров по адресу 86h. Если бит управляющего TRISB регистра имеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующего регистра защелки. При включении питания все линии порта по умолчанию настроены на ввод.

4.8 Модуль таймера и регистр таймера

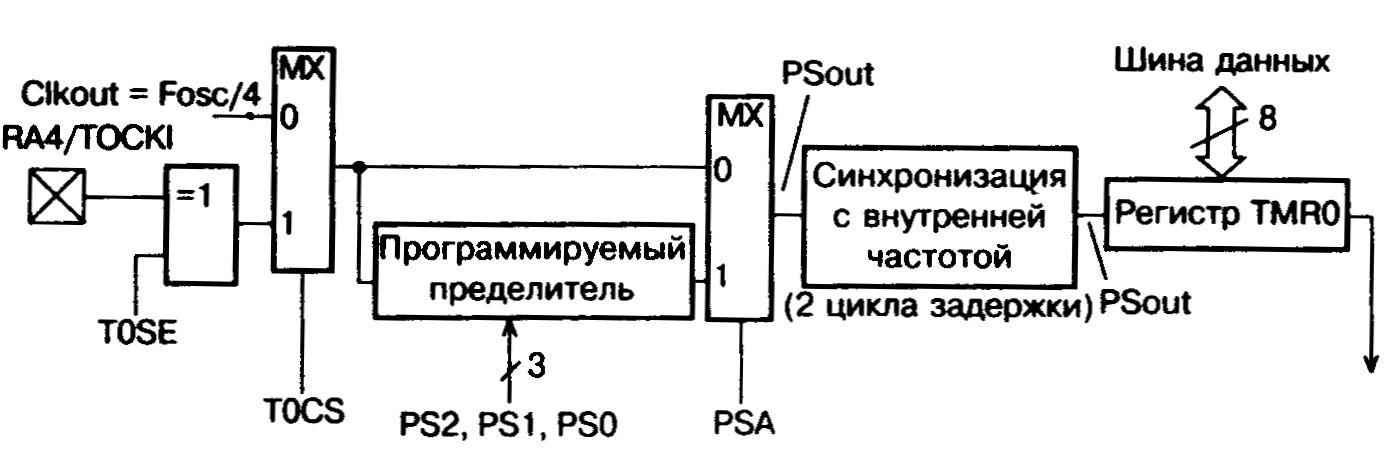

Структура модуля таймера/счетчика TIMER0 и его взаимосвязь с регистрами TMR0 и OPTION показаны на рисунке 8. T1MER0 является программируемым модулем и содержит следующие компоненты:

- 8-разрядный таймер/счетчик TMR0 с возможностью чтения и записи как регистр;

- 8-разрядный программно управляемый предварительный делитель (пределитель);

- мультиплексор входного сигнала для выбора внутреннего или внешнего тактового сигнала;

- схему выбора фронта внешнего тактового сигнала;

- формирователь запроса прерывания по переполнению регистра TMR0 с FFh до 00h.

Режим таймера выбирается путем сбрасывания в ноль бита T0CS регистра OPTION <5>. В режиме таймера TMR0 инкрементируется каждый командный цикл (без пределителя). После записи информации в TMR0 инкрементирование его начнется после двух командных циклов. Это происходит со всеми командами, которые производят запись или чтение-модификацию-запись TMR0 (например, MOVFTMRO, CLRFTMR0). Избежать этого можно при помощи записи в TMR0 скорректированного значения. Если TMR0 нужно проверить на равенство нулю без останова счета, следует использовать инструкцию MOVF TMR0,W.

Рисунок 8 – Структурная схема таймера/счетчика TMR0

Режим счетчика выбирается путем установки в единицу бита T0CS регистра OPTION<5>. В этом режиме регистр TMR0 будет инкрементироваться либо нарастающим, либо спадающим фронтом на выводе RA4/ T0CKI от внешних событий. Направление фронта определяется управляющим битом T0SE в регистре OPTION<4>. При T0SE = 0 будет выбран нарастающий фронт.

Пределитель может использоваться или совместно с TMR0, или со сторожевым (Watchdog) таймером. Вариант подключения делителя контролируется битом PSA регистра OPTION<3>. При PSA=0 делитель будет подсоединен к TMR0. Содержимое делителя программе недоступно. Коэффициент деления пределителя программируется битами PS2...PS0 регистра OPTION<2:0>.

Прерывание по TMR0 вырабатывается тогда, когда происходит переполнение регистра таймера/счетчика при переходе от FFh к 00h. Тогда устанавливается бит запроса T0IF в регистре INTCON<2>. Данное прерывание можно замаскировать битом T0IE в регистре INTCON<5>. Бит запроса T0IF должен быть сброшен программно при обработке прерывания. Прерывание по ТМ R0 не может вывести процессор из режима SLEEP потому, что таймер в этом режиме не функционирует.

При PSA=1 делитель будет подсоединен к сторожевому таймеру как постделитель (делитель на выходе).