- •2.2 Архитектура и режимы работы мп к580вм80

- •3 Разработка подсистемы памяти

- •3.1 Оперативно запоминающее устройство к134ру6

- •4.1 Архитектура программируемого таймера кр580ви53

- •4.2 Архитектура бис параллельного интерфейса кр580вв55

- •4.5 Архитектура контроллера прямого доступа к памяти кр580вт57

- •5 Разработка алгоритма работы микропроцессорной системы

3 Разработка подсистемы памяти

3.1 Оперативно запоминающее устройство к134ру6

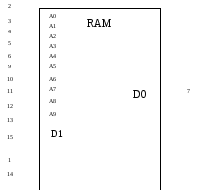

Микросхема ОЗУ серий К134 относятся к типу асинхронного статического ОЗУ, поэтому достаточно просты в применении. Обратим внимание лишь на некоторые особенности, знание которых необходимо для практики. На рисунке 12 представлена функциональные элементы микросхемы К134.

Рисунок 12 - Функциональные элементы микросхемы К134

Изготовлены на технологии ИИЛ в сочетании ТТЛ. Емкость данного типа микросхем составляет бит. Ее особенность заключается в том, что выход построен по схеме с открытым коллектором ОК. Наличие такого выхода не позволяет объединять информационные входы и выходы. При соединении нескольких микросхем по выходам можно использовать схему «монтажного ИЛИ» с подключением к точке соединения источника питания через внешний токоограничивающий резистор. Для расчета его сопротивления необходимо учитывать, прежде всего, значение выходного тока в состоянии логического 0, равное 16 мА. При хранении потребляемая мощность снижается вдвое.

Цоколевка ОЗУ К134РУ6 представлена на рисунке 13.

Рисунок 13 – Цоколевка ОЗУ К134РУ6

Микросхема может работать в режиме записи, считывания и хранения информации. В режиме записи сигнал CS можно подавать постоянным уровнем. В режиме считывания сигналы CS и можно подавать постоянным уровнем.

В режиме хранения невыбранная схема потребляет мощность в 2 раза меньшую, чем в режиме обращения. Выводы Д1 и Д0 в процессе работы запрещается объединять так как в режиме записи на выходе микросхемы логическая 1.

Таблица 8 - Обозначение выводов ОЗУ К134РУ6

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

7; 15 |

D0, D1 |

Д0, Д1 |

Выходы данных |

выход |

1,0,z |

|

2; 3;4; 5; 6; 9; 10; 11; 12; 13 |

А(0-9) |

А(0-9) |

Входы данных с локальной шины МП |

вход |

1,0,z |

|

1 |

CS (3-1) |

ЦС(3-1) |

Выбор микросхем, L-уровень сигнала подключения ОЗУ к системной шине |

вход |

1 |

|

14 |

|

З/С |

Запись/считывание |

Вход/ выход |

0 |

3.2 Постоянное запоминающее устройство К541РТ2

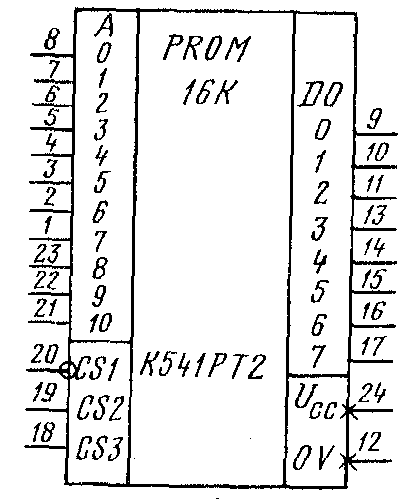

Микросхемы программируемых ПЗУ по принципу построения и функционирования аналогичны масочным ПЗУ, но имеют существенное отличие в том, что допускают программирование на месте своего применения пользователем. Операция программирования заключается в разрушении (пережигании) части плавких перемычек на поверхности кристалла импульсами тока амплитудой 30 ... 50 мА. Технические средства для выполнения этой операции достаточно просты и могут быть построены самим пользователем. Это обстоятельство в сочетании с низкой стоимостью и доступностью микросхем ППЗУ обусловило их широкое распространение в радиолюбительской практике. На рисунке 14 представлена цоколевка БИС ПЗУ К541РТ2.

Рисунок 14 — Цоколевка ПЗУ К541РТ2

В данном курсовом проекте рассматривается применение микросхемы ПЗУ К541РТ2.

Таблица 9 — Описание выводов БИС ПЗУ К541РТ2

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

17; 16; 15; 14; 13; 11; 10; 9 |

DO(7-0) |

ДО(7-0) |

Выходы данных |

выход |

0, 1, z |

|

1 |

2 |

3 |

4 |

5 |

6 |

|

8; 7; 6; 5; 4; 3; 2; 1; 23; 22; 19 |

А(10-0) |

А(10-0) |

Входы данных с локальной шины МП |

вход |

0, 1, z |

|

18 |

CS (3-1) |

ЦС(3-1) |

Выбор микросхем, L-уровень сигнала подключения ОЗУ к системной шине |

вход |

0 |

|

20 |

UCC |

UCC |

Напряжение питания (+5 В) |

вход |

0 |

|

10 |

OV |

ОБЩ |

Напряжение питания (0 В) |

вход |

1 |

Микросхемы ПЗУ серии К541 выполнены по технологии ИИЛ. Матрица до программирования, т. е. в исходном состоянии, содержит однородный массив проводящих перемычек, соединяющих строки и столбцы во всех точках их пересечений. Перемычки устанавливают из поликристаллического кремния. Перемычка в матрице выполняет роль ЭП. Наличие перемычки кодируют логической 1, если усилитель считывания является повторителем, и логическим 0, если усилитель считывания — инвертор. Следовательно, микросхема ПЗУ в исходном состоянии перед программированием в зависимости от характеристики выходного усилителя может иметь заполнение матрицы либо логическим 0, либо логической 1.

Программирование микросхемы, матрица которой в исходном состоянии заполнена 0, заключается в пережигании перемычек в тех ЭП, где должны храниться 1. Если матрица в исходном состоянии заполнена 1, то пережигают перемычки в ЭП, где должны храниться 0.

Микросхемы ПЗУ потребляют большую мощность от источника питания. Поэтому представляется целесообразным использовать их свойство работать в режиме импульсного питания, когда питание на микросхему подают только при обращении к ней для считывания информации. Особенности применения микросхем ПЗУ в этом режиме состоят; в следующем: во-первых, на управляющие входы должны быть поданы уровни, разрешающие доступ к микросхеме: если необходим 0, то данный вывод соединяют с общим выводом, если 1, то с шиной через резистор с сопротивлением 1 кОм; в этом случае функции сигнала выбора микросхемы выполняет импульс напряжения питания Ucc; во-вторых, для обеспечения1 режима импульсного питания применяют транзисторные ключи, на переходах которых падает часть напряжений, поэтому напряжение, подаваемое к внешним ключам, должно быть выбрано с учетом требования иметь на выводе питания микросхемы номинальное напряжение 5 В; в-третьих, из-за инерционности процессов коммутации цепи питания время выборки адреса микросхемы увеличивается в 2—3 раза.

При использовании импульсного режима питания среднее значение потребляемого тока и, следовательно, уровень потребляемой мощности существенно уменьшаются.

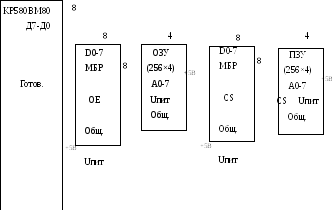

3.3 Подключение ОЗУ и ПЗУ к системной шине

Подключение БИС ОЗУ КР134РУ6 и БИС ПЗУ КР541РТ2 к магистралям зависит от их разрядности, а для оперативной памяти - от ее типа. В микропроцессорной системе удобнее всего использовать восьмиразрядные запоминающие устройства. Подключение статических ОЗУ осуществляется аналогично ПЗУ. Объем памяти определяется количеством используемых БИС. При большом их количестве в схемы ЗУ вводиться буферирование линий данных и адреса.

Схема подключение ОЗУ и ПЗУ к магистралям показа на рисунке 15.

Рисунок 15 - Подключение ОЗУ и ПЗУ к магистралям

4 РАЗРАБОТКА ПОДСИСТЕМЫ ПРЕРЫВАНИЙ, ВВОДА/ВЫВОДА. ВЫБОР ТАЙМЕРА.