БАЛАКОВСКИЙ ИНСТИТУТ ТЕХНИКИ, ТЕХНОЛОГИИ И УПРАВЛЕНИЯ

ФАКУЛЬТЕТ ИНЖЕНЕРНО-СТРОИТЕЛЬНЫЙ

КАФЕДРА «УПРАВЛЕНИЕ И ИНФОРМАТИКА В ТЕХНИЧЕСКИХ СИСТЕМАХ»

КУРСОВОЙ ПРОЕКТ

по дисциплине

Локальные системы управления

САУ ОЧИСТКИ ВЕТРОВОГО СТЕКЛА СПОРТИВНОГО

САМОЛЕТА

Выполнил ст. гр. УИТ –51

Удалов Ю.В.

Допущен к защите Защитил с оценкой _________

Руководитель проекта Скоробогатова Т.Н._________

Скоробогатова Т. Н. _______ «___» ______________2004 г

«___» ____________2004г

2004

СОДЕРЖАНИЕ

|

Введение |

3 |

|

1 Техническое задание |

4 |

|

2 Разработка электрической схемы электромузыкального синтезатора |

6 |

|

2.1 Модуль процессора |

7 |

|

2.2 Модуль клавиатуры и стробов |

8 |

|

2.3 Модуль генераторов тона |

10 |

|

2.4 Модуль задания параметров |

11 |

|

3 Обоснование выбора микропроцессора КР580ИК80А |

12 |

|

4 Описание микропроцессора КР580ИК80А |

14 |

|

4.1 Структура микропроцессора КР580ИК80А |

14 |

|

4.2 Система команд микропроцессора КК580ИК80А |

19 |

|

4.3 Основные временные параметры микропроцессора КР580ИК80А |

22 |

|

4.4 Цоколевка микросхемы КР580ИК80А |

32 |

|

5 Описание управляющей программы |

34 |

|

Заключение |

37 |

|

Список использованной литературы |

38 |

|

|

|

ВВЕДЕНИЕ

С развитием технологии и схемотехники цифровых интегральных схем появилась возможность создавать сложные устройства обработки цифровой информации в виде компактных микросхем. Однако увеличение сложности реализуемого алгоритма обработки, как правило, сужает область его применения. Устранить противоречие между сложностью БИС и ее универсальностью удалось за счет программирования выполняемых микросхемой функций.

В программируемых БИС потребитель может путем подачи определенных командных сигналов задать один из возможных режимов работы. Основным типом БИС являются БИС микропроцессоров.

Широкую популярность микропроцессоры получили благодаря своим высоким функциональным возможностям и эксплуатационным характеристикам, придавшим средствам вычислительной техники и автоматики качественно новые свойства: появились и получили широкое распространение микрокалькуляторы, микроЭВМ, персональные ЭВМ, интеллектуальные роботы. Такие характеристики микропроцессоров как малые габариты, масса, потребляемая мощность позволили применять их в областях, в которых использование традиционных средств вычислительной техники было принципиально невозможным.

Целью данной курсовой работы является проектирование многоголосого электромузыкального синтезатора (ЭМС) на базе микропроцессорного комплекта КР580, описание работы устройства и основных его характеристик, а также разработка соответствующего программного обеспечения.

Основная идея цифро-аналоговых электронных музыкальных синтезаторов эстрадного применения состоит в том, что с помощью специальных алгоритмов обработки сигналов от клавиатуры каждой нажатой клавише предоставляется во «временное пользование» канал синтеза звука, который в другой момент может предоставляться любой другой клавише, в отличие от полифонических ЭМС, в которых каждой клавише соответствует свой канал синтеза.

1 ТЕХНИЧЕСКОЕ ЗАДАНИЕ

Цифровые электронные музыкальные синтезаторы (ЭМС) представляют собой микроЭВМ, периферийными устройствами которых являются клавиатура, пульт управления и программируемые узлы синтеза спектральных и временных характеристик звука.

Основная идея цифро-аналоговых электронных музыкальных синтезаторов эстрадного применения состоит в том, что с помощью специальных алгоритмов обработки сигналов от клавиатуры каждой нажатой клавише предоставляется во «временное пользование» канал синтеза звука, который в другой момент может предоставляться любой другой клавише. Поскольку реальное число нажатых клавиш всегда меньше их общего числа, то это позволяет существенно уменьшить необходимое число каналов синтеза при незначительном сокращении функциональных возможностей инструмента. Число «голосов» в них обычно колеблется от четырех до десяти. Каждый канал содержит цифровые и аналоговые управляемые кодом узлы.

Любому звуку соответствует неразрывная совокупность его амплитудной и спектральной характеристик, изменяющихся во времени. Следовательно, задача синтезатора состоит в получении комплекса признаков – звуковысотного, спектрального и амплитудного. Соответствующий комплекс аппаратуры (управляемые генератор, фильтр, усилитель, генераторы функций времени) входит в состав канала синтеза. Поскольку определяющим признаком музыкального звука является его высота (т. е. частота основного тона), управляемый генератор должен обладать достаточной точностью в широком диапазоне генерируемых частот. Этому требованию удовлетворяет управляемый кодом генератор на основе счетчика с переменным коэффициентом деления. Он легко реализуется на таймерах, входящих в МПК КР580. Таблица коэффициентов деления для всех 48 клавиш размещена в ПЗУ, где каждый коэффициент занимает два байта.

Полученный на выходе таймера меандр проходит дальнейшую обработку в канале синтеза для получения необходимых спектрально- и амплитудно-временных характеристик.

Генераторы функций времени запускаются строб сигналом, который вырабатывается процессором для каждого канала на основании информации об изменении состояния клавиатуры [6].

Характеристики ЭМС:

- диапазон по клавиатуре, октав 4;

- число каналов синтеза 6;

- число тональных генераторов в канале 2;

- погрешность установления частоты основных тонов не более,

% от полутона 2,9;

- время срабатывания клавиши не более, мс 3,2;

- число оперативно выбираемых вариантов звучания 48.

2 РАЗРАБОТКА ЭЛЕКТРИЧЕСКОЙ СХЕМЫ МНОГОГОЛОСОГО

ЭЛЕКТРОМУЗЫКАЛЬНОГО СИНТЕЗАТОРА

На рисунке 1 представлена структурная схема музыкального синтезатора.

Рисунок 1 – Структурная схема ЭМС

6 6 Выход

Процессорный модуль является ведущим узлом. Под его управлением работают модули клавиатуры и стробов, задания параметров синтеза и генераторов тона. Модуль клавиатуры связывает процессор с клавиатурой и формирует строб-сигналы для каждого из шести каналов. Модуль задания параметров синтеза вырабатывает вектор управляющих напряжений, определяющий значения программируемых параметров синтеза звука. Модуль генераторов тона из двух опорных частот вырабатывает шесть пар тональных сигналов [6].

Цифро-аналоговый многоголосый ЭМС построен на базе микропроцессорного комплекта БИС КР580.

2.1 Модуль процессора

В состав процессорного модуля входят:

- микропроцессор D2– КР580ИК80А;

- генератор тактовых импульсов D3– КР580ГФ24;

- формирователь сигналов шины адресов, шины данных и шины

управления;

- дешифратор адреса D10 – К155ИД4;

- оперативное запоминающее устройство (ОЗУ) D7, D8– К155РУ2;

- постоянное запоминающее устройство (ПЗУ) D11 – КР556РТ5.

МП КР580ИК80А связан с генератором тактовых импульсов D3 посредством входов G1, G2 (входы фазы 1 и фазы 2), ГТ и СБР. Генератор тактовых импульсов стабилизирован резонатором Z1 с частотой 13000 кГц. Кроме того, элемент D3 формирует сигналы ГОТ и УСТ (начальная установка всех узлов схемы при включении питания). Внешние входы этих сигналов используются только при отладке схемы. Микросхемы D1 – К589АП16 и D4.6 – К155ЛН1 повышают нагрузочную способность тех линий шины адресов (ША), к которым требуется подключить более одного входа ТТЛ интегральных схем. На выходе МП формируется сигнал ПМ приема с ШД информации, выданной запоминающим устройством (ЗУ) или устройством ввода/вывода (УВВ), или сигнал ЗП выдачи байта информации на ШД для записи в ЗУ или УВВ. Сигнал ПМ, определяющий направление передачи, через элементы D4.2 и D4.3 поступает на входы выбора шины ВШ шинных формирователей D5, D6 – К589АП16, которые формируют сигналы двунаправленной ШД.

Оперативное запоминающее устройство емкостью 16 6-разрядных слов служит для хранения кодов клавиш, максимальное значение которых 2FH. Поэтому два старших разряда ШД в ОЗУ не используются.

Выходы ОЗУ подключаются к ШД через буферный элемент D9 – К155ЛН6 с тремя состояниями выхода. Программируемое ПЗУ (D11) содержит программу ЭМС, таблицу частот тональных генераторов и таблицу оперативно выбираемых звучаний. Используемое адресное пространство микропроцессора разбито на восемь страниц по 512 байт. Такое разбиение осуществляется дешифратором (D10), входы которого подключены прямо к ША [9], ША [10] и через D4.6 к ША |11]. При этом обращение ко всем внешним регистрам происходит так же, как к ячейкам памяти. В большинстве страниц используется 1...6 адресов (таблица 1). Такое распределение адресного пространства имеет целью упростить программу [6].

Таблица 1 – Распределение адресного пространства

|

Поле адресов |

Используемые адреса |

Назначение |

|

0000-01FF 0200-03FF 0400-05FF 0600-07FF

0800-09FF 0A00-0BFF 0C00-0DFF 0E00-0FFF |

0000-01FF 0200-0203 0400 0600-0603

0801-0806 0A00 0C00-0C0F 0E00 |

ПЗУ программ ППА модуля клавиатуры и стробов ПЗУ номера свободного канала ППА модуля задания параметров синтеза Регистры данных таймеров РУС таймеров ОЗУ Сброс триггера «ПРОГРАММА» |

2.2 Модуль клавиатуры и стробов

Модуль выполнен

на основе программируемого устройства

для ввода/вывода параллельной информации

(ППА) D1

– КР580ВВ55. Все три канала ППА настроены

для работы в режиме «0», причем каналы

А и В на вывод, а канал С на ввод информации.

Клавиатура представляет собой матрицу

(8![]() 6)

нормально разомкнутых контактов, столбцы

которой подключены к дешифратору D2

– 155ИД4, а строки ко входам мультиплексора

D4

– К155КЛ7. Диоды V1

– V48

исключают взаимное влияние нажатых

клавиш. Процессор последовательно

загружает в порт А ППА (его адрес 0200Н)

коды клавиш от 00Н до 2FH.

Три младшие линии порта А преобразуются

дешифратором D2

в позиционный код, а линии А3…А5 управляют

работой мультиплексора D4.

Если клавиша на пересечении выбранных

столбца и строки нажата, то на выходе

D4

появляется сигнал высокого уровня,

который считывается процессором по

линии С0. На основании этой информации

может быть произведена установка в «1»

одного из строб-сигналов СТР1…СТР6.

6)

нормально разомкнутых контактов, столбцы

которой подключены к дешифратору D2

– 155ИД4, а строки ко входам мультиплексора

D4

– К155КЛ7. Диоды V1

– V48

исключают взаимное влияние нажатых

клавиш. Процессор последовательно

загружает в порт А ППА (его адрес 0200Н)

коды клавиш от 00Н до 2FH.

Три младшие линии порта А преобразуются

дешифратором D2

в позиционный код, а линии А3…А5 управляют

работой мультиплексора D4.

Если клавиша на пересечении выбранных

столбца и строки нажата, то на выходе

D4

появляется сигнал высокого уровня,

который считывается процессором по

линии С0. На основании этой информации

может быть произведена установка в «1»

одного из строб-сигналов СТР1…СТР6.

По состоянию

сигналов СТР1…СТР6 с помощью ППЗУ D9

– КР556РТ4 определяется номер свободного

канала, у которого соответствующий

строб-сигнал имеет низкий уровень. Он

считывается процессором с линии ЩДО…ЩД3

по сигналу

![]() и выдается в порт В ППА, с линий которого

поступает на дешифратор D5

– 155ИД4. Сигнал ЗП через интегрирующую

цепь R4С1

поступает на вход разрешения дешифратора.

В результате на соответствующем выходе

D5

появляется отрицательный импульс, по

которому сигнал с выхода D4

переписывается в один из триггеров

D6…D8

– 155ТМ2. После этого в канал В заносится

код 00Н.

и выдается в порт В ППА, с линий которого

поступает на дешифратор D5

– 155ИД4. Сигнал ЗП через интегрирующую

цепь R4С1

поступает на вход разрешения дешифратора.

В результате на соответствующем выходе

D5

появляется отрицательный импульс, по

которому сигнал с выхода D4

переписывается в один из триггеров

D6…D8

– 155ТМ2. После этого в канал В заносится

код 00Н.

Сигнал «Программа» с кнопки S49 формируется триггером D10.1 – 155ТМ2 и через дифференцирующую цепочку С2R13 поступает на вход установки триггера D10.2 по линии С1 ППА. Активный уровень на этой линии инициирует отработку подпрограммы выбора синтезируемого звучания, которая заключается в загрузке портов А, В и С ППА модуля выбора параметров синтеза данными из таблицы в соответствии с кодом нажатой клавиши.

После отработки подпрограммы происходит сброс триггера записью произвольного слова по адресу 0Е00Н. Светодиод HL1 служит для индикации режима «Программа» и расположен на передней панели ЭМС.

Появление на выходах D9 четырех нулей свидетельствует о том, что все каналы заняты. В этом случае процессор производит операции с нулевымканалом, который физически не существует, то есть выполняет операции по обработке канальной информации в холостую [6].

2.3 Модуль генераторов тона

Модуль (рисунок 2) выполнен на четырех таймерах КР580ВИ53. С помощью ППЗУ КР556РТ4 регистрам таймеров присваиваются адреса (таблица 2), что позволяет упростить программу. Этот прием также как и применение ППЗУ в модуле клавиатуры и стробов, служит для упрощения программы.

Рисунок 2 – Модуль генераторов тона

Решение части задач аппаратными средствами необходимо не только для уменьшения объема ППЗУ, но и для уменьшения времени «срабатывания» клавиш, которое зависит от продолжительности одного полного прохода цикла программы и совместно с механическими характеристиками клавиатуры определяет ее качество. Это время не должно быть более 6 мс [6].

Таблица 2 – Адреса регистров таймера

|

Входы ППЗУ |

Выходы ППЗУ |

Регистр- приемник |

|||||||

|

ВУ0800 |

ВУ0А00 |

А2 |

А1 |

А0 |

БМ2 |

БМ1 |

А1 |

А0 |

|

|

1 0 0 0 0 0 0 1 |

0 1 1 1 1 1 1 1 |

Х 0 0 0 1 1 1 Х |

Х 0 1 1 0 0 1 Х |

Х 1 0 1 0 1 0 Х |

0 1 1 1 0 0 0 1 |

0 0 0 0 1 1 1 1 |

1 0 0 1 0 0 1 1 |

1 0 1 0 0 1 0 1 |

РУС PD0 PD1 PD2 PD0 PD1 PD2 - |

2.4 Модуль задания параметров

Модуль построен на основе ППА КР580ВВ55. Все порты модуля настроены на вывод в режиме «0». Совокупность линий портов А, В и С – это один 24-разрядный выходной регистр, каждый разряд которого можно использовать для управления параметром, имеющим два значения (например, скважность тонального сигнала 2 или 4), а группа разрядов – для выбора значений управляющего напряжения (посредством ЦАП или аналогового коммутатора). Конкретное назначение каждого разряда определяется при выборе схемы каналов синтеза и набора управляемых параметров [6].

3 ОБОСНОВАНИЕ ВЫБОРА МИКРОПРОЦЕССОРА

Цифровой электронный музыкальный синтезатор выполнен на базе микропроцессорного комплекта (МПК) КР580, позволяющий создавать эффективные вычислительные устройства, ориентированные на реализацию вычислительных задач и устройств управления. Основу МПК составляет центральный процессорный элемент КР580ИК80А, являющийся функционально-законченным однокристальным параллельным 8-разрядным микропроцессором с фиксированной системой команд. В МП отсутствуют возможности аппаратного наращивания разрядности обрабатываемых данных.

Микропроцессорный комплект БИС серии КР580 предназначен для создания широкого класса средств вычислительной техники и обработки информации. На основе комплекта строятся микроЭВМ контрольно-измерительных систем, микроЭВМ для управления технологическими процессами, контроллеры периферийных устройств, бытовых приборов и игровых автоматов.

Выбор между различными микропроцессорами должен выполняться на основе анализа особенностей их применения, требования точности, разрядности и т.д.

Аналогом процессора КР580ИК80А является 8-разрядный параллельный однокристальный микропроцессор типа 8080 фирмы Intel, серийно выпускаемый с 1974 г. Сравнительный анализ данных микропроцессоров приведен в таблице 3.

При сравнении МП КР580ИК80А и 8080 видно, что они обладаю почти одинаковыми характеристиками. Так же известно, что выбранный МП КР580ИК80А обладает меньшим быстродействием и отсутствием возможности наращивания разрядности.

Однако, несмотря на недостатки, МП КР580ИК80А отличается простотой архитектуры и дешевизной, что является важным условием при построении простых устройств, которые не требуют высокой точности и высокого быстродействия, а значит, нет необходимости в дополнительной сложности и затратах.

Таблица 3 – Характеристики МП КР580ИК80А и 8080

|

Микропроцессор |

КР580ИК80А |

8080 |

|

Разрядность слова данных/команд, бит |

8 |

8 |

|

Технология изготовления |

n-МОП |

n-МОП |

|

Емкость непосредственно адресуемого ЗУ, байт |

64К |

64К |

|

Число основных команд |

246 |

78 |

|

Максимальная тактовая частота, МГц |

2,5 |

4,77 |

|

Время выполнения команды наим./наиб., мкс |

1/3,2 |

1,5/3,75 |

|

Число уровней прерываний |

2 |

1 |

|

Число регистров общего назначения |

6 |

8 |

|

Число выводов корпуса |

40 |

40 |

|

Напряжение питания, В |

5,12 |

5,12 |

В МП КР580ИК80А используется радиальная система прерываний, рассчитанная на малое число активных периферийных устройств – до восьми. Так как в ЭМС периферийных устройств немного (клавиатура, пульт управления и программируемые узлы синтеза спектральных и временных характеристик звука), выбор МП с радиальной системой прерываний является вполне оправданным.

Таким образом, в цифровом электромузыкальном синтезаторе предпочтительнее использование МП КР580ИК80А, который благодаря своей архитектуре и фиксированному набору команд является наиболее подходящим для применения в подобных устройствах.

4 ОПИСАНИЕ МИКРОПРОЦЕССОРА КР580ИК80А

4.1 Структура микропроцессора КР580ИК80А

Структурная схема микропроцессора приведена на рисунке 3.

Рисунок 3 – Структурная схема микропроцессора КР580ИК80А

В состав БИС КР580ИК80А входят:

-

8-разрядное арифметико-логическое устройство (ALU);

-

регистр признаков (RS), фиксирующий признаки, вырабатываемые ALU в процессе выполнения команд;

-

аккумулятор (А);

-

регистр аккумулятора (RGa);

-

регистр временного хранения операндов (RGb);

-

десятичный корректор (DAA), выполняющий перевод информации из двоичной в двоично-десятичную форму;

-

регистр команд (IR), предназначенный для хранения первого байта команды, содержащего код операции;

-

дешифратор команд (DCU);

-

блок регистров для приема, выдачи и хранения информации в процессе выполнения программ, содержащий программный счетчик (РС), указатель стека (SP), регистр адреса (PGA), шесть регистров общего назначения (B, C, D, E, H, L) и вспомогательные регистры (W, Z);

-

схема управления и синхронизации (CU) формирующая последовательности управляющих сигналов для работы ALU и блока регистров;

-

16-разрядный буферный регистр адреса (ВА);

-

8-разрядный буферный регистр данных (BD);

-

двунаправленный мультиплексор (MUX) для обмена операндами и результатами операций между ALU и блоком регистров.

Микропроцессор ИК850ИК80А имеет 16 – разрядный трехбайтовый канал адреса А (15-0), 8-разрядный двунаправленный трехстабильный канал данных D(7-0), четыре входных и шесть выходных выводов управления. МП обеспечивает адресацию внешней памяти объемом до 64К байт, а также адресацию 256 устройств ввода и 256 устройств вывода [4].

Функционально МП БИС можно разбить на блоки: блок регистров, арифметико-логическое блок, блок регистров команд и устройства управления, буферные схемы шин адреса и данных.

4.1.1 Блок регистров. Включает в себя шесть 16-ти разрядных регистров. Таким образом, Микропроцессор КР580ИК80А содержит программно-доступные 8-разрядные регистры:

-

регистр аккумулятора (RGa);

-

общие регистры B, C, D, E;

-

регистр признаков RS;

-

16-разрядные специализированные регистры: счетчик команд (PC);

-

регистр-указатель стека (SP);

-

сдвоенный регистр косвенного адреса HL (Н – регистр старшего полуадреса, L – регистр младшего полуадреса).

Кроме того, имеются программно-недоступные регистры:

-

8-разрядные регистры временного хранения W, Z;

-

8-разрядный регистр команды (IR);

-

16-разрядный регистр адреса РGА.

Шесть 8-и разрядных регистров общего назначения могут использоваться как отдельные 16-и разрядные регистровые пары. Они предназначены для хранения операндов, промежуточных и конечных результатов, а также адресов и индексов при косвенной и индексной адресациях.

Регистр - аккумулятор используется в качестве источника одного из операндов и места, где фиксируется результат операции. В команде аккумулятор в явном виде не адресуется. Для того, чтобы аккумулятор мог одновременно являться регистром операнда и регистром результата операции, он строится на основе двухступенчатых триггеров.

Использование аккумулятора и общих регистров позволяет при выполнении команд уменьшить количество обращений к памяти и тем самым повысить быстродействие МП.

Наличие в блоке регистров специализированного регистра косвенного адреса HL позволяет иметь команды с подразумеваемой косвенной адресацией, то есть без указания в команде номера регистра, хранящего исполнительный адрес.

При выполнении операций в МП возникает потребность в кратковременном хранении некоторых операндов и результатов выполнения операций. Для этой цели служат регистры временного хранения данных W, Z. [2].

В состав блока регистров входит регистр-защелка адреса памяти. Собственно регистр адреса недоступен программисту. Однако любая пара регистров (BC, DE, HL) может быть использована для задания адресов команд и данных в программе. Этот адрес под воздействием соответствующих команд не только может быть загружен в регистр-защелку адреса, но и модифицирован в процессе загрузки. Регистр-защелка адреса передает адрес в буферную схему и далее в шину адреса.

Указатель стека SP содержит адрес вершины стека, а сам стек может использовать любую зону ОЗУ объемом до 64К байт или специальной ОЗУ, адресуемое сигналом STACK. SP содержит адрес памяти, начиная с которого ее можно применять для хранения и восстановления содержимого программно-доступных регистров МП БИС. Содержимое указателя стека уменьшается на 2, когда данные загружаются в стек, и увеличивается на 2, когда данные извлекаются из стека. [4].

4.1.2 Арифметико-логический блок. Включает в себя: восьмиразрядную комбинированную схема ALU; десятичный корректор, построенный на базе ПЗУ; регистр признаков; аккумулятор и регистр временного хранения операндов.

АЛУ выполняет арифметические и логические операции над 8-разрядными числами в процессе межрегистровых пересылок. К одному из входов схемы АLU всегда подключен аккумулятор, к другому через регистр Т (регистр временного хранения) может быть подключен любой из общих регистров.

АLU непосредственно связано с регистром признаков, в соответствующих разрядах которого фиксируются особенности выполнения каждой операции: нулевой результат в аккумуляторе – Z, перенос из старшего разряда – CY, знак результата – S, паритет – Р и вспомогательный перенос из младшего полубайта – АС. Наличие в МП регистра признаков упрощает осуществление программных переходов в зависимости от состояния одного или более триггеров признаков. АLU позволяет в процессе межрегистровых «пересылок с перекосом» выполнять операции сдвига на один разряд вправо или влево. Многократный сдвиг реализуется последовательностью одноразрядных сдвигов, то есть последовательно расположенными в программе командами сдвига.

Схема десятичного корректора DAA, предназначена для того, чтобы под воздействием специальной команды интерпретировать результат выполнения двоичной операции как результат операции десятичной арифметики.

АLU реализует простейшие арифметические и логические операции (сложение, вычитание, сдвиг, сравнение, логическое умножение). Все более сложные операции (умножение, деление, вычисление элементарных функций) выполняются по подпрограммам [2].

4.1.3 Буферные схемы шин адреса и данных.

Двунаправленный буфер шины данных предназначен для логического и электрического разделения внутрипроцессорной шины данных и внешней, системной шины ШД. Буфер состоит из регистра-защелки и выходной схемы с тремя состояниями, то есть схемы, обеспечивающей на выходе состояние 0, 1 и полное электрическое отключение от нагрузки (высокоимпедансное состояние).

В режиме ввода информации внутренняя шина данных подсоединяется к регистру-защелке буфера, загрузку которого из внешней шины производит буферная схема под управлением команды. В режиме вывода информации буферная схема передает в шину данных содержимое буферного регистра-защелки, на вход которого по внутренней шине с одного из регистров загружен код.

Во время выполнения операций МП, не связанных с процедурами обмена с внешними по отношению к МП устройствами системы, буферная схема отключается от шины данных ШД, то есть переходит в высокоимпедансное состояние «не нуль, не один», которое называется «плавающим» состоянием.

Буферная схема шины адреса (однонаправленная) обеспечивает передачу адресов команд и данных, а также номера периферийных устройств от МП в систему. Выход буфера адреса, точно так же как и буфера данных, может переходить в отключенное состояние [2].

4.1.4 Блок регистра команд и устройства управления. Данный блок содержит регистр команд, дешифратор команд и устройство управления. При извлечении команды из памяти первый бай, содержащий код команды помещается в регистр команд, а затем поступает на дешифратор команд. В свою очередь, дешифратор команд с устройством управления и сигналами F1 и F2 тактового генератора формирует управляющие сигналы для всех внутренних блоков МП БИС, а также его выходные сигналы управления и состояния.

4.2 Система команд микропроцессора КК580ИК80А

Данные в микропроцессоре представлены в виде 8-разрядных кодов. Для идентификации отдельных разрядов в байте они нумеруются от D0 до D7 и считаются расположенными справа налево. При этом нулевой бит D0 соответствует младшему разряду, а D7 – старшему разряду. Однобайтовый код может рассматриваться либо как положительное целое число с диапазоном значений от 0 до 255, либо как целое число с диапазоном значений от -128 до +127. Для целых чисел используются двухбайтное и многобайтное представления.

Форматы команд могут быть одно-, двух- или трехбайтными (рисунок 4). Многобайтная команда должна размещаться в последовательно расположенных ячейках памяти, а в первом байте команды В1 всегда указывается код операции.

Рисунок 4 – Форматы команд

Для управления процессом выполнения программы используется слово-состояние программы, формат которого представлен на рисунке 4, г. Старший байт слова-состояния составляет содержимое аккумулятора, а младший – содержит флаги условий регистра признаков, определяемые результатом выполнения арифметических и логических операций. Установка флагов производится при выполнении следующих условий:

- флаг знака S, если знаковый бит результата операции равен 1, иначе сбрасывается;

- флаг нуля Z, если результат операции равен 0, в противном случае сбрасывается;

- флаг дополнительного переноса АС при наличии переноса из третьего разряда, иначе сбрасывается;

- флаг четности P, если результат содержит четное число единиц, иначе сбрасывается;

- флаг переноса CY при наличии переноса (при сложении) или заема (при вычитании) из старшего разряда результата, иначе сбрасывается.

В микропроцессоре используются пять способов адресации данных:

- прямая – адрес М ячейки памяти, где расположен операнд, указываетсяво втором (младшая часть адреса) и в третьем (старшая часть адреса) байтах команды;

- регистровая – в команде задается адрес оперативного регистра или пары регистров, где находится соответственно 8- или 16-битовый операнд;

- регистровая косвенная – адрес М ячейки памяти, где расположен операнд, определяется содержимым парного регистра, явно или неявно указанного в команде; при этом старший байт адреса находится в первом регистре пары, а младший – во втором;

- непосредственная - операнд содержится в команде: для двухбайтовых команд – во втором байте, для трехбайтовых – во втором (младшая часть операнда) и в третьем (старшая часть операнда) байтах команды;

- стековая – адрес ячейки памяти, содержащей операнд, находится в указателе стека.

Специфический способ адресации памяти используется в однобайтовой команде, применяемой при обработке прерываний для вызова одной из восьми подпрограмм обслуживания прерываний. Команды RST различаются по номеру N, задаваемому в трехбайтовом поле кода команды. В результате выполнения команды RSTN управление передается по адресу, определяемому восьмикратным увеличением N.

По функциональному признаку команды микропроцессора делятся на пять групп:

-

команды передачи данных из регистра в регистр или память и из памяти в регистр;

-

арифметические команды: сложения, вычитания, инкремента, декремента;

-

логические команды: И, ИЛИ, исключающее ИЛИ, сравнение, сдвиг, инвертирование;

-

команды передачи управления и обработки подпрограмм;

-

команды ввода/ вывода и управления состоянием процессора.

Система команд микропроцессора содержит 78 команд, включающих 111 операций. Кодировка одиночных и парных адресов регистров микропроцессора, используемая при определении кодов команд, представлена в таблице 4 [4].

Таблица 4 – Кодировка адресов регистров БИС КР580ИК80А

|

Регистр R |

Код SSS или DDD |

Регистр R |

Код SSS или DDD |

Парный регистр RP |

Код RR |

|

B C D E |

000 001 010 011 |

H L M A |

100 101 110 111 |

B – C D – E H – L S – P |

00 01 10 11 |

4.3 Основные временные параметры микропроцессора КР580ИК80А

Время выполнения команды микропроцессора зависит от типа команды и составляет от одного до пяти машинных циклов (М). Длительность машинного цикла может составлять от трех до пяти машинных тактов (Ti). Длительность машинного такта равна периоду тактовой частоты, задаваемой частотой фаз СLK1, СLK2 генератора тактов.

Операции, выполняемые микропроцессором в машинном цикле, определяются 8-разрядной информацией, характеризующей состояние внутренних узлов микропроцессора. Этот байт состояния называется также словом состояния процессора и выдается на шину данных микропроцессора в такте Т2 каждого машинного цикла. Байт состояния может использоваться для формирования управляющих сигналов обращения к ЗУ, УВВ, а также при организации различных режимов работы микропроцессорной системы.

Для фиксации слова-состояния процессора можно использовать внешний 8-разрядный регистр. На рисунке 5 приведена временная диаграмма и схема записи слова состояния в многорежимный буферный регистр К589ИР12. Запись осуществляется сигналом CLK1 в такте Т2 с использованием сигнала SYNC.

Рисунок 5 – Временная диаграмма и схема записи слова состояния в многорежимный буферный регистр К589ИР12

Наименование и назначение сигналов состояния, а также соответствующие им разряды шины данных микропроцессора указаны в таблице 5.

Таблица 5 – Сигналы состояния микропроцессора

|

Обозначение сигнала |

Разряд шины данных |

Назначение сигнала |

|

INTA

WO

STACK

HLTA

OUT

M1

INT

MEMR |

D0

D1

D2

D3

D4

D5

D6

D7 |

Подтверждение прерывания; используется для стробирования приема команды RST в МП из схемы прерывания Запись; L – уровень сигнала указывает на запись данных в ЗУ или ВУ; H – уровень сигнала – запись в микропроцессор Стек; Н – уровень сигнала указывает, что на шине адреса установлено содержимое SP Подтверждение останова; Н – уровень сигнала указывает на переход МП в состояние останова Ввод; Н – уровень сигнала указывает, что на шине адреса установлен код ВУ и можно осуществить ввод данных в МП по сигналу DBIN=1 Н – уровень сигнала указывает, что МП принимает первый байт команды Ввод; Н –уровень сигнала указывает, что на шине адреса установлен код ВУ и можно осуществить ввод данных в МП по сигналу DBIN=1 Чтение; Н – уровень сигнала указывает, что осуществляется чтение содержимого ЗУ по адресу, установленному на шине адреса |

Разновидности машинных циклов микропроцессора приведены в таблице 6. Цикл выборки команды MI является первым и обязательным машинным циклом всех команд микропроцессора.

Таблица 6 – Разновидности машинных циклов микропроцессора

|

Машинный цикл |

Обозначение сигнала слова-состояния процессора |

|||||||

|

INTA |

WO |

STACK |

HLTA |

OUT |

M1 |

INP |

MEMR |

|

|

Цикл М1 – выборка команды Цикл чтения из ЗУ » запись в ЗУ » чтение из стека Цикл записи в стек Цикл ввода » вывода » прерывания » останова » прерывания при останове |

0

0 0 0 0 0 0 1 0 1 |

1

1 0 1 0 1 0 1 1 1 |

0

0 0 1 1 0 0 0 0 0 |

0

0 0 0 0 0 0 0 1 1 |

0

0 0 0 0 0 1 0 0 0 |

1

0 0 0 0 0 0 1 0 1 |

0

0 0 0 0 1 0 0 0 0 |

1

1 0 1 0 0 0 0 1 0 |

Управление функционированием микропроцессорной системы на базе микропроцессора КР580ИК80А осуществляется генерацией управляющих сигналов по двум шинам: по шине управления собственно микропроцессором (WR, DBIN, INTE, …) в каждом такте работы микропроцессора Ti и по шине данных путем генерации слова-состояния процессора (PSW) в каждом машинном цикле М.

Диаграмма состояний микропроцессора при выполнении типового машинного цикла с внешними управляющими сигналами READY, HOLD, INT и сигналом HLTA, формируемым по команде HLT, приведена на рисунке 6.

Рисунок 6 – Диаграмма состояния микропроцессора при выполнении

типового машинного цикла

Из диаграммы состояний микропроцессора можно выделить следующие основные особенности функционирования:

1) Любой машинный цикл включает, по крайней мере, три такта (T1, Т2 и Т3). Такты Т4, Т5 не обязательны и применяются для внутренних операций МП.

2) Подача сигнала Н-уровня на вход RESET длительностью не менее трех периодов тактовой частоты микропроцессора устанавливает его в исходное состояние. В программный счетчик заносятся нули, а схема управления начинает формировать такт Т1 машинного цикла выборки команды М1.

3) В такте Т2 микропроцессор анализирует сигналы READY, HLTA и HOLD. При наличии на входе READY напряжения Н-уровня и отсутствии сигналов HLTA и HOLD микропроцессор переходит к такту Т3. в зависимости от вида выполняемой команды машинный цикл завершается после выполнения тактов Т3, Т4 или Т5. Если выполнение команды не закончено, то микропроцессор переходит к следящему машинному циклу команды, начиная с такта Т1. В конце каждой команды микропроцессор проверяет наличие запроса прерывания. Если есть Н-уровень сигнала на входе INT и триггер разрешения прерывания установлен (INTE=1), то МП устанавливает триггер прерывания (ТТ1) и приступает к выполнению машинного цикла прерывания, начиная с такта Т1. При наличии на входе READY сигнала L-уровня в такте Т2 МП переходит в состояние ожидания (Tw), пока не появится сигнал READY от внешнего устройства.

4) В такте Т2 при наличии сигналов на входах READY и HOLD производится установка внутреннего триггера захвата (ТТ2). Однако переход к режиму захвата до такта Т3 не разрешается, чтобы МП мог закончить обмен с внешним регистром в начале такта Т3. По окончании состояния захвата МП всегда переходит к такту Т1 следующего машинного цикла. Если текущий машинный цикл содержит такты Т4 и Т5, то они совмещаются с режимом захвата.

5) В состоянии останова МП переходит при наличии сигнала HLTA, формируемого во втором машинном цикле команды HLT, при этом внутренние шины адреса и данных переводятся в высокоимпедансное состояние и появляется Н-уровень напряжения на выходе WAIT – выполнение программы прекращается. Из состояния останова МП выходит по сигналу сброса или по сигналу запроса прерывания INT при установленном триггере разрешения прерывания (INTE = 1). В состоянии останова МП может переходить в режим захвата, если поступает сигнал напряжения Н-уровня на вход HOLD.

На рисунке 7 изображена временная диаграмма приема информации в микропроцессор в цикле чтения из ЗУ и цикле ввода. В такте Т1 по каналу данных поступает информация о состоянии текущего цикла; в канал адреса выдается адрес ячейки памяти, из которой считывается информация о состоянии текущего цикла; в канал адреса выдается адрес ячейки памяти, из которой считывается информация в текущем цикле; формируется сигнал Н-уровня. В такте Т2 микропроцессор устанавливает сигнал высокого уровня DBIN, а канал данных принимает информацию с шины данных по импульсу синхронизации CLK2 при условии, что есть сигнал высокого уровня READY. Если необходимо согласовывать по времени работу ЗУ и МП, то можно увеличить длительность сигнала приема DBIN подачей L-уровня сигнала READY. Тогда МП переходит в состояние ожидания и выдает сигнал Н-уровня WAIT, а канал адреса, канал данных и сигнал DBIN не изменяют своего состояния. По сигналу READY Н-уровня МП переходит в такт Т3, изменяются уровни сигналов WAIT и DBIN; канал данных переводится в высокоимпедансное состояние. В такте Т4 информация в адресном канале изменяется и становится неопределенной до начала следующего цикла. В течение всего цикла приема информации сигнал WR сохраняет Н-уровень напряжения. Временная диаграмма основных сигналов при выдаче информации из МП для цикла записи в ЗУ и цикла вывода отличается отсутствием сигнала DBIN и формированием после такта Т2 сигнала WR L-уровня. В такте Т2 микропроцессор выдает информацию на шину данных для записи в ЗУ или УВВ.

Рисунок

7 - Временная диаграмма приема информации

в микропроцессор

Рисунок

7 - Временная диаграмма приема информации

в микропроцессор

в цикле чтения из ЗУ и цикле ввода

Микропроцессор приступает к обработке запроса прерывания, поступившего на вход INT, если внутренний триггер разрешения прерывания установлен (INTE = 1). Установка или сброс триггеров разрешения прерывания может производиться программно, с помощью команд Е1 (разрешение прерывания) или D1 (запрещение прерывания). Если запрос прерывания принят, то МП начинает выполнение машинного цикла прерывания. В такте Т1 этого цикла на шину адреса выдается содержимое программного счетчика, а на шину данных – слово-состояние процессора (рисунок 7, б). Слово-состояние цикла прерывания содержит единицы в разрядах D0 (INTA), D1 (WO), D5 (M1) (таблица 6). Сигнал подтверждения прерывания INTA используется в микропроцессорной системе для квитирования микропроцессором приема запроса прерывания. В такте Т1 по сигналу CLK2 производится также сброс триггера разрешения прерывания (INTE = 0), что приводит к запрету приема последующих запросов прерываний. В такте Т2 по сигналу DBIN обычно вводится код операции из памяти, но слово-состояние цикла прерывания содержит в разряде D7 (MEMR) нуль-запрет на чтение из памяти, поэтому код операции должно сформировать внешнее устройство. В такте Т2 сбрасывается также внутренний триггер прерывания, а содержимое РС не изменяется. В такте Т3 команда RST, сформированная ВУ, с шины данных передается в регистр команд МП, а в тактах Т4 и Т5 производится ее дешифрирование. По команде RST содержимое РС (адрес возврата) запоминается в стеке, а в РС заносится адрес первой команды программы обработки прерывания, определяемой номером команды RST. Запоминание адреса возврата из прерывания в стеке выполняется в циклах М2 и М3 – запись в стек.

Для обмена информацией с быстродействующими ВУ используется режим прямого доступа к памяти, в котором выполнение программы приостанавливается, буферы адреса и данных МП переходят в высокоимпедансное состояние, и контроллер прямого доступа у памяти организует обмен данными между ВУ и памятью микроЭВМ. Временная диаграмма режима прямого доступа к памяти в цикле чтения из ЗУ изображена на рисунке 8. При наличии сигнала READY Н-уровня МП переходит в состояние захвата в такте Т3. Для режима прямого доступа в цикле записи в ЗУ при наличии сигнала READY переход в состояние захвата осуществляется после такта Т3 [4].

Рисунок

8 - Временная диаграмма режима прямого

доступа к памяти в

Рисунок

8 - Временная диаграмма режима прямого

доступа к памяти в

цикле чтения из ЗУ

Основные электрические параметры микропроцессора КР580ИК80А при температуре окружающей среды (+25±10)ºС [4]:

- потребляемая мощность, В А ≤1,25;

- время выполнения команды типа R – R, мкс ≤1,6;

- выходное напряжение логической единицы Uон, В ≥3,7;

- выходное напряжение логического нуля UOL, В ≤0,4;

- ток потребления от источника питания IBC, мА ≤50;

- ток потребления от источника питания IСС, мА ≤70;

- ток потребления от источника питания IBS, мА ≤ 1,0;

- ток утечки на входах RESET, READY, INT, HOLD, IIL, мА ≤ ±1,0;

- ток утечки на входах CLK1, CLK2, IIL, мкА ≤ ±1,0;

- ток утечки на шинах данных и адреса в режиме

захвата шин ≤ ±10.

4.4 Цоколевка микросхемы КР580ИК80А

Цоколевка микросхемы КР580ИК80А представлена на рисунке 9.

R

Рисунок 9 - цоколевка микросхемы КР580ИК80А

Назначение выводов [4]:

А(15 - 0) – трехстабильная 16-разрядная шина адреса;

D(7 – 0) – двунаправленная трехстабильная 8-разрядная шина данных;

WR – выход сигнала «выдача» - напряжение L-уровня указывает на выдачу байта информации на шину D(7 – 0)для записи в ЗУ или УВВ;

DBIN – выход сигнала «прием» - напряжение Н-уровня указывает на прием с шины D(7 – 0) байта информации, выданного ЗУ или УВВ;

INTE – выход сигнала «разрешение прерывания»;

INT – вход сигнала «запрос на прерывание»;

HLDA – выход сигнала «подтверждение захвата» - напряжение Н-уровня указывает на перевод шин адреса и данных МП в высокоимпедансное состояние;

HOLD – вход сигнала «захват» - напряжение Н-уровня указывает на запрос другими устройствами системы на управление шинами системы;

WAIT – выход сигнала «ожидание» - напряжение Н-уровня указывает на

состояние ожидания МП;

READY – вход сигнала «готовность» - напряжение Н-уровня указывает на готовность данных на шине D(7 – 0) к вводу в МП или на готовность внешних устройств к приему информации, служит для синхронизации микропроцессоров с ЗУ или УВВ;

SYNC – выход сигнала «синхро» - напряжение Н-уровня идентифицирует начало каждого машинного цикла;

CLK1, CLK2 – тактовые сигналы, определяют тактовую частоту работы МП БИС;

R – вход установки 0 – установка счетчика команд в нуль, сброс триггеров разрешения прерывания и захвата шин;

UCC1 – напряжение питания (+5 В);

UСC2 – напряжение питания (+12 В);

UСС3 – напряжение питания (-5 В);

GND – общий вход (напряжение питания 0 В).

5 ОПИСАНИЕ УПРАВЛЯЮЩЕЙ ПРОГРАММЫ

Для нормальной работы многоголосого музыкального синтезатора необходимо программное обеспечение, связывающее и корректирующее работу всех устройств по заданному алгоритму.

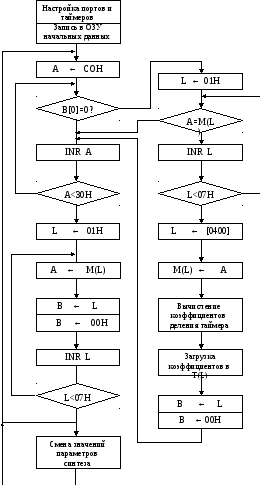

На рисунке 10 представлен алгоритм работы ЭМС, где:

А – код клавиши (состояние порта А ППА в модуле клавиатуры и стробов);

В – код строб-сигнала (состояние порта В ППА);

L – номер канала синтеза;

M(l) – ячейка озу, соответствующая каналу с номером l; t(l) – регистр данных таймера, соответствующий каналу с номером l.

При включении питания ЭМС происходит сброс процессора и программируемого параллельного интерфейса ППА. С адреса 0000Н начинается обработка программы: настройка портов и таймеров для работы в соответствующих режимах и заполнение ячеек ОЗУ последовательностью кодов от 31Н до 36Н. Это необходимо для исключения «молчащих» клавиш, которые могут появиться при случайной установке кодов в ОЗУ после подачи питания.

Основная часть программы начинается с опроса нулевой клавиши. Если она не нажата, то опрашивается следующая клавиша и так далее. Если очередная клавиша нажатая, то выполняется часть программы, обрабатывающая коды нажатых клавиш. Она определяет, содержится ли код данной клавиши в памяти одного из каналов, если нет, ставит в соответствие ей свободный канал синтеза. Это достигается вводом номера свободного канала из ПЗУ модуля клавиатуры и стробов, загрузкой кода клавиши в ячейку ОЗУ, соответствующую этому каналу, выбором из таблицы и загрузкой в таймер двухбайтного кода, определяющего частоту тонального сигнала и установкой активного уровня канального строб-сигнала. Далее осуществляется переход к опросу следующей клавиши. После опроса всех клавиш устанавливаются строб-сигналы каналов в соответствии с состоянием клавиш. После этого алгоритм повторяется с опроса нулевой клавиши. Если сигнал «Программа» принимает активный уровень, то после очередного прохода выполняется программа смены звучания, состоящая в поиске нажатой клавиши и загрузке ППА модуля задания параметров синтеза соответствующими ей кодами из таблицы 7.

Таблица 7 – Содержимое ПЗУ программ

|

ADR |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

A |

B |

C |

D |

E |

F |

|

0000 |

3E |

89 |

32 |

03 |

02 |

3E |

80 |

32 |

03 |

06 |

3E |

36 |

32 |

00 |

0A |

3E |

|

0001 |

76 |

32 |

00 |

0A |

3E |

B6 |

32 |

00 |

0A |

3E |

31 |

32 |

06 |

0C |

3C |

32 |

|

0002 |

01 |

0C |

3C |

32 |

02 |

0C |

3C |

32 |

03 |

0C |

3C |

32 |

04 |

0C |

3C |

32 |

|

0030 |

05 |

0C |

3A |

02 |

02 |

E6 |

02 |

C2 |

FD |

00 |

0E |

00 |

79 |

32 |

00 |

02 |

|

0040 |

3A |

02 |

02 |

E6 |

01 |

C2 |

6A |

00 |

0C |

79 |

FE |

30 |

DA |

3C |

00 |

26 |

|

0050 |

0C |

2E |

01 |

7E |

32 |

00 |

02 |

7D |

32 |

01 |

02 |

3E |

00 |

32 |

01 |

02 |

|

0060 |

2C |

7D |

FE |

07 |

DA |

53 |

00 |

C3 |

32 |

00 |

26 |

2E |

2E |

01 |

7E |

E6 |

|

0070 |

3F |

B9 |

CA |

48 |

00 |

2C |

7D |

FE |

07 |

DA |

6E |

00 |

3A |

00 |

04 |

6F |

|

0080 |

26 |

0C |

71 |

26 |

08 |

16 |

00 |

79 |

07 |

C6 |

9D |

5F |

1A |

77 |

1C |

1A |

|

0090 |

77 |

7D |

32 |

01 |

02 |

3E |

00 |

32 |

01 |

02 |

C3 |

48 |

00 |

D8 |

06 |

75 |

|

00A0 |

06 |

19 |

06 |

C1 |

05 |

6E |

05 |

20 |

05 |

D7 |

04 |

91 |

04 |

50 |

04 |

12 |

|

00B0 |

04 |

D7 |

03 |

A0 |

03 |

6C |

03 |

3B |

03 |

0DC |

03 |

E1 |

02 |

B7 |

02 |

90 |

|

00C0 |

02 |

6B |

02 |

49 |

02 |

28 |

02 |

09 |

02 |

EC |

01 |

D0 |

01 |

B6 |

01 |

9D |

|

00D0 |

01 |

86 |

01 |

70 |

01 |

5C |

01 |

48 |

01 |

36 |

01 |

24 |

01 |

14 |

01 |

04 |

|

00E0 |

01 |

F6 |

00 |

E8 |

00 |

DB |

00 |

CF |

00 |

C3 |

00 |

B8 |

00 |

AE |

00 |

A4 |

|

00F0 |

00 |

9B |

00 |

92 |

00 |

8A |

00 |

82 |

00 |

7B |

00 |

74 |

00 |

0E |

00 |

79 |

|

0100 |

32 |

00 |

02 |

3A |

02 |

02 |

E6 |

01 |

C2 |

0F |

01 |

0C |

C3 |

FF |

00 |

79 |

|

0110 |

E6 |

3F |

51 |

C6 |

40 |

4F |

06 |

01 |

0A |

32 |

00 |

06 |

79 |

C6 |

40 |

4F |

|

0120 |

0A |

32 |

01 |

06 |

79 |

C6 |

40 |

0A |

32 |

02 |

06 |

06 |

00 |

7A |

32 |

00 |

|

0130 |

02 |

3A |

02 |

02 |

E6 |

01 |

C2 |

31 |

01 |

32 |

00 |

0E |

C3 |

3A |

00 |

FF |

Часть адресов ППЗУ с 0140Н по 01FFН зарезервированы под таблицу вариантов звучания и программируется в процессе окончания настройки ЭМС после отработки звучаний [6].

0032

0030

006Е

Нет

Да

0048 Да

Нет

Да

Да

Нет

Нет 004F

0053

Да

Нет

00FD

Рисунок 10 – Алгоритм работы ЭМС

ЗАКЛЮЧЕНИЕ

В курсовой работе был разработан многоголосый электромузыкальный синтезатор на базе микропроцессора КР580ИК80А серии КР580. Данный МП удовлетворяет всем требованиям, которые были предъявлены к проектируемому устройству.

Для электромузыкального синтезатора была рассмотрена управляющая программа, представленная в виде блок-схемы алгоритма работы ЭМС.

Таким образом, курсовая работа была выполнена в соответствии с техническим заданием, электромузыкальный синтезатор на базе микропроцессорного комплекта КР580 может успешно применяться, обеспечивая надежную работу.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

-

Алексеев В. Н., Коновалов А. М., Колосов Р. Т. Микропроцессорные средства производственных систем. – Л.: Машиностроение, 1988.

-

Горбунов В. Л., Панфилов Д. И., Преснухин Д. Л. Справочное пособие по микропроцессорам и микроЭВМ. – М.: Высшая школа, 1988.

-

Майоров С. А., Кириллов В. В., Приблуда А. А. Введение в микроЭВМ. – Л.: Машиностроение, 1988.

-

Хвощ С. Т., Варлинский Н. Н., Попов Е. А. Микропроцесоры и микроЭВМ в системах автоматического управления: Справочник. – Л.: Машиностроение, 1987

-

Преснухин Л. Н. Микропроцессоры. – М.: Высшая школа, 1986.

-

Книгин С. Б. Многоголосый электромузыкальный синтезатор // Микропроцессорные средства и системы. – 1986. – №5.

-

Фомина Н. Н. Разработка конструкции печатных плат. Методические указания к выполнению практической работы по дисциплине «Конструкторско-технологические особенности проектирования и изготовления модулей аппаратурной реализации САУ». – Саратов, 1995.

ПРИЛОЖЕНИЕ А

(обязательное)