- •1 Анализ технического задания

- •2.2 Арифметическо-логическое устройство

- •2.3 Память микроконтроллера

- •2.4 Управление работой микроконтроллера

- •2.5 Организация ввода-вывода информации в микроконтроллере

- •3.2 Постоянное запоминающее устройство

- •4.3 Контроллер прямого доступа к памяти (кпдп)

- •4.4 Программируемый интервальный таймер (пит)

- •5.2 Шинный формирователь к580ва86

4.3 Контроллер прямого доступа к памяти (кпдп)

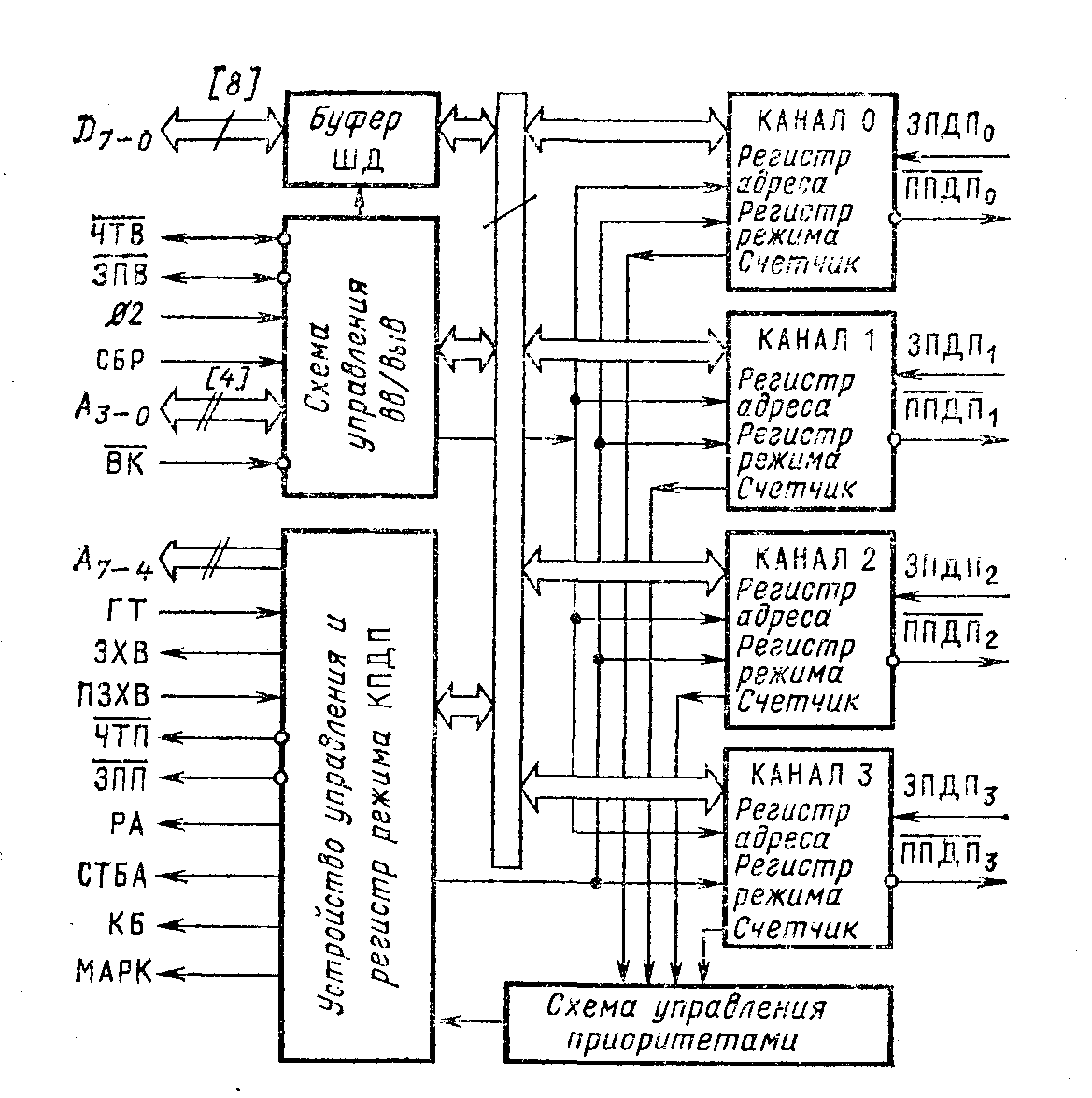

Схема контроллера прямого доступа к памяти (КПДП) К580ВТ57, показанная на рисунке 25, реализует функции аппаратурно-управляемого (внепроцессорного) обмена данными между основной памятью и внешними устройствами (чаще всего с внешней памятью на магнитном носителе).

Контроллер

ПДП имеет четыре независимых канала

ПДП, в состав каждого из которых входят:

16-разрядный регистр адреса, 14-разрядный

счетчик длины блока данных и 2-разрядный

регистр режима канала. Каждый канал ПДП

имеет один входной сигнал запроса

прямого доступа ЗПДП и один выходной

сигнал подтверждения прямого доступа

![]() .

Буфер ШД обеспечивает информационную

связь КПДП с системной шиной.

.

Буфер ШД обеспечивает информационную

связь КПДП с системной шиной.

На этапе инициализации МП загружает через него в КПДП начальные адреса областей ОЗУ, размер блоков данных и коды режимов, а в процессе работы может считывать содержимое любого регистра и счетчика, кроме регистра режима.

Рисунок 25 - Схема контроллера прямого доступа к памяти (КПДП)

К580ВТ57

Кроме перечисленных функций, через буфер ШД контроллер, получая из МП разрешение на управление системной шиной, выдает в ШД старший байт адреса (А15-8) из регистра адреса инициированного канала ПДП. При этом на одной из линий управления (СТБА) генерируется сигнал строба адреса, по которому выданный байт адреса загружается во внешний МБР (К589ИР12), выходы которого в свою очередь подсоединяются к линиям А15-8 шины адреса.

Устройство управления КПДП и схема управления вводом—выводом в зависимости от комбинации управляющих сигналов переводят КПДП в одно из двух возможных состояний: на этапе инициализации КПДП, а также при считывании содержимого регистров по инициативе МП контроллер является ведомым, а в режиме ПДП — ведущим. Ниже приводится перечень имен управляющих и адресных сигналов и соответствующих им линий, а также описываются действия, выполняемые КПДП под их воздействием или при их генерации.

![]() —

чтение

ввода—вывода. В зависимости от того,

является КПДП ведомым или ведущим,

данная линия может быть входной или

выходной. По сигналу ЧТВ = 0 ведомого

КПДП на ШД передается содержимое

внутреннего регистра, адресуемого по

линиям Аз-о. Ведущий КПДП формирует в

этой линии управляющий сигнал, который

используется для передачи байта данных

из внешней памяти на ШД.

—

чтение

ввода—вывода. В зависимости от того,

является КПДП ведомым или ведущим,

данная линия может быть входной или

выходной. По сигналу ЧТВ = 0 ведомого

КПДП на ШД передается содержимое

внутреннего регистра, адресуемого по

линиям Аз-о. Ведущий КПДП формирует в

этой линии управляющий сигнал, который

используется для передачи байта данных

из внешней памяти на ШД.

![]() —

запись

ввода — вывода. Сигнал на этой линии

также может быть входным или выходным.

У ведомого КПДП входной сигнал 0 на линии

ЗПВ управляет загрузкой байта из ШД

во внутренний регистр, адресуемый по

линиям Аз-о. Ведущий КПДП выходным

сигналом ЗПВ записывает байт из ШД в

буферный регистр селектированного

внешнего устройства.

—

запись

ввода — вывода. Сигнал на этой линии

также может быть входным или выходным.

У ведомого КПДП входной сигнал 0 на линии

ЗПВ управляет загрузкой байта из ШД

во внутренний регистр, адресуемый по

линиям Аз-о. Ведущий КПДП выходным

сигналом ЗПВ записывает байт из ШД в

буферный регистр селектированного

внешнего устройства.

Ф2 — входная линия, на которую подаются сигналы второй фазы синхронизации системы.

СБР — сигнал сброса, по которому сбрасывается в нуль содержимое регистра режима КПДП, что приводит к дезактивации контроллера: КПДП не реагирует на сигналы запроса ПДП до тех пор, пока не будет завершена программная инициализация.

А3-0 — младший полубайт адреса. Для ведомого КПДП эта шина (4 линии) является входной и используется для адресации одного из регистров контроллера при инициализации или считывании. Ведущий КПДП выдает в шину младший полубайт адреса ОЗУ из регистра адреса работающего канала ПДП.

ВК - выбор корпуса. Сигнал на этот вход контроллера подается с одного из выходов адресного дешифратора. Сигнал ВК=0 задает контроллеру состояние ведомого и является разрешающим для входных сигналов ЧТВ и ЗПВ. Когда КПДП выступает в качестве ведущего, то вход ВК блокируется с тем, чтобы при адресации ОЗУ контроллер не мог сам себя выбрать.

А7-4 — четыре выходные адресные линии, которые подсоединяются к соответствующим линиям ША и на которые КПДП выдает второй полубайт адреса памяти.

ГТ — готовность — входной сигнал, обеспечивающий временное согласование контроллера с медленно действующей памятью. По сигналу ГТ = 0 устройство управления КПДП переходит в состояние ожидания Sож и обеспечивает асинхронный режим обмена с памятью (см. ниже).

ЗХВ — захват — выходной сигнал КПДП, который, поступая на вход ЗПДП микропроцессора К580, отключает его от системной шины после такта Т3 текущего машинного цикла.

ПЗХВ — подтверждение захвата—входной сигнал с одноименного выхода МП, свидетельствующий о том, что КПДП становится ведущим, а режим прямого доступа разрешен.

![]() —

чтение

памяти — выходной сигнал 0 используется

для управления чтением из ОЗУ в режиме

ПДП. Во всех остальных случаях на выходе

линии ЧТП — высокоимпедансное состояние.

—

чтение

памяти — выходной сигнал 0 используется

для управления чтением из ОЗУ в режиме

ПДП. Во всех остальных случаях на выходе

линии ЧТП — высокоимпедансное состояние.

![]() —

запись

в память — выходной сигнал 0 управляет

записью в ОЗУ при передачах с прямым

доступом. Так же, как и линия ЧТП, она

является трехстабильной, что позволяет

эти линии прямо соединять с одноименными

линиями, исходящими из системного

контроллера (К580СК28).

—

запись

в память — выходной сигнал 0 управляет

записью в ОЗУ при передачах с прямым

доступом. Так же, как и линия ЧТП, она

является трехстабильной, что позволяет

эти линии прямо соединять с одноименными

линиями, исходящими из системного

контроллера (К580СК28).

РА — разрешение адреса — выходной сигнал, который применяется для перевода ША и ШД и некоторых линий ШУ других модулей системы в высокоимпедансное состояние. Линия сигнала РА заводится на входы разрешения выдачи РВ или выбора корпуса ВК шинных драйверов, через которые все модули системы (кроме ОЗУ) соединены с системной шиной.

СТБА — строб адреса — выходной сигнал, который сопровождает выдачу контроллером в ШД старшего байта адреса ОЗУ и используется для загрузки этого байта в МБР для последующей трансляции в ША.

КБ — конец блока — выходной сигнал, генерируемый контроллером в последнем цикле ПДП текущего блока данных. Так как. сигнал КБ формируется при переходе вычитающего счетчика байтов через нуль, то на этапе инициализации для задания длины блока байт в счетчик необходимо загрузить двоичный код N—1. Так как разрядность канальных счетчиков 14 бит, то максимальный размер блока данных равен 16 Кбайт.

МАРК—маркер — выходной сигнал, генерируемый КПДП для сопровождения каждого 128-го байта от начала передачи блока данных в режиме ПДП. В основе схемы генерации сигнала МАРК лежит 7-разрядный счетчик по mod 128. Как правило, размерность блока данных N кратна 128.

Схема управления приоритетами КПДП реализует заданный режим распределения приоритетов между четырьмя каналами ПДП. Программным путем на этапе инициализации каналам присваиваются фиксированные приоритеты (Ко — высший, Кз — низший), а кроме того, может быть задан режим циклического приоритета, при котором после реализации передачи по некоторому каналу ПДП ему присваивается низший приоритет, а приоритеты остальных каналов изменяются по замкнутому кругу: Ко-К1-К2-К3-К0. При этом приоритеты всех четырех внешних устройств, работающих через данный КПДП, оказываются равными.

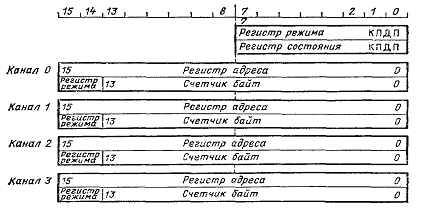

Инициализация КПДП. С точки зрения программиста КПДП представляет собой массив из 18 специализированных регистров с форматами, показанными на рисунке 26.

Рисунок 26 – Массив регистров КПДП

Все регистры КПДП программно-доступны, но в регистр режима КПДП можно только записать, а из регистра состояния КПДП можно только считать байт данных. Канальные регистры могут работать в режимах записи и считывания. Инициализация КПДП осуществляется загрузкой УС и исходных данных в адресуемые регистры по командам OUT или командам MOV в зависимости от способа раскраски адресной шины в МП-системе. При этом линии A15-4 ША после дешифрирования формируют сигнал ВК контроллера, а линии А3-0 адресуют один из внутренних регистров КПДП как это показано в таблице 6.

Назначение линий А3-0 шины адреса следующее: А3 селектирует обращение к регистрам каналов (А3=0 ) или к регистрам КПДП (A3=l), A2=1 выбирает один из четырех каналов ПДП, а А0 задает регистр адреса (А0=0) или счетчик (Ао=1) в выбранном канале.

Обмен с каждым из 16-разрядных регистров канала осуществляется парой команд OUT на этапе загрузки и парой команд IN при считывании.

Таблица 6 – Адреса регистров КПДП

С целью идентификации младшего и старшего байтов передаваемых слов в КПДП имеется программно-недоступный триггер М/С, который устанавливается в исходное нулевое состояние или по сигналу СБР, или при загрузке регистра режима КПДП, а затем при каждой очередной операции загрузки (соответственно при чтении) изменяет свое состояние на противоположное. Поэтому команды обращения к регистрам каналов КПДП должны следовать парой, и первая из них оперирует с младшим, а вторая — со старшим байтами слова. Для правильного срабатывания триггера М/С в системе необходимо предусмотреть меры, исключающие появление на входе ВК контроллера сигнала 0 во время действия сигналов ЧТВ или ЗПВ.

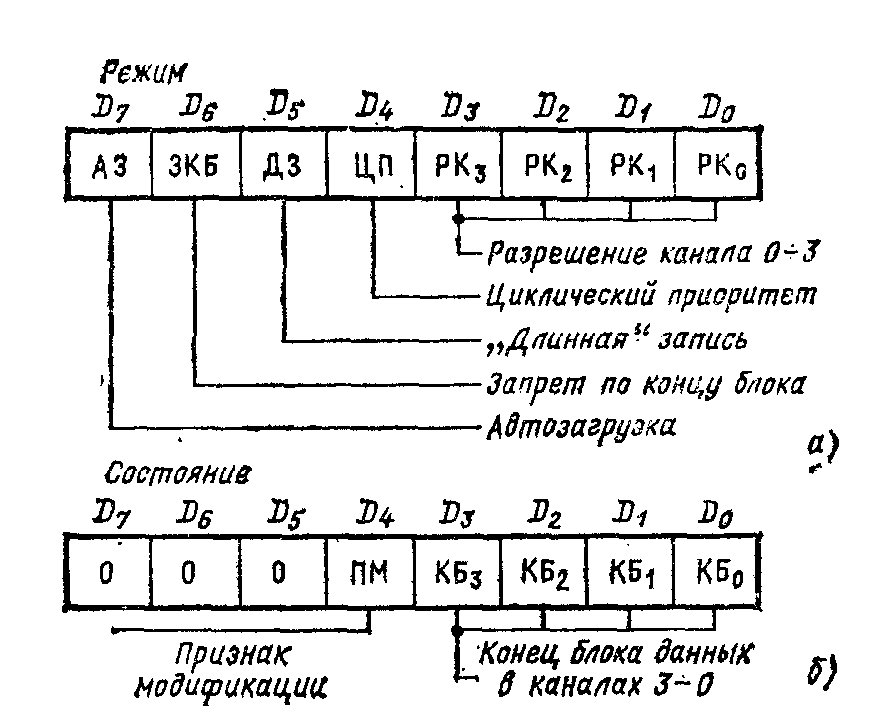

На рисунке 27 показаны форматы и назначение полей регистров режима и состояния КПДП.

Рисунок 27 - Форматы и назначение полей регистров режима и состояния

КПДП

Регистр режима устанавливается в нулевое состояние по сигналу СБР, запрещая тем самым работу всех каналов ПДП. Затем производится загрузка регистров адреса и счетчиков всех каналов, и только после этого выполняется загрузка УС в регистр режима ПДП. Такая последовательность инициализации КПДП позволяет избежать искажений содержимого ОЗУ от запросов ПДП, возникающих в период инициализации.

Младшие полбайта регистра режима КПДП используются для маскирования сигналов ЗПДП. Если разряд разрешения канала PKi=0, то КПДП удовлетворяет запрос ПДП i-гo канала.

Разряд ЦП определяет порядок работы схемы управления приоритетами: при ЦП=0 распределение приоритетов между каналами ПДП фиксировано, и при ЦП = 1 реализуется режим циклической смены приоритетов.

Если в управляющем сигнале, загружаемом в регистр режима КПДП, разряд «длинной» записи Д3 = 1, то контроллер генерирует сигналы ЗПВ и ЗПП с удвоенной длительностью, что во многих применениях позволяет обеспечить временное согласование с памятью без использования сигнала готовности ГТ и перевода КПДП в состояние ожидания.

Сигнал 1 в разряде запрета по концу блока (3КБ) позволяет каждому каналу ПДП осуществить передачу только одного блока данных, так как по сигналу КБ сбрасывается в нуль разряд разрешения работы РК соответствующего канала. Эту маску можно снять только путем загрузки нового УС в регистр режима КПДП. При 3КБ=0 реализуются многоблочные передачи данных по каналам ПДП.

В некоторых применениях МП-систем необходимо обеспечить повторную передачу блока данных или передачу двух «связанных» блоков данных. С целью исключения необходимости программной перенастройки КПДП между передачами блоков вводится специальный режим автозагрузки, который инициируется старшим битом A3 регистра режима КПДП. Повторная передача блока данных возможна только через канал 2. Если А3 = 1, то при загрузке исходных значений регистра адреса и счетчика канала 2 они автоматически переписываются в соответствующие регистры канала 3. После окончания передачи первого блока данных через канал 2 и генерации сигнала КБ исходные параметры блока данных из регистров канала 3 в цикле модификации переписываются в регистры канала 2, инициируя, таким образом, повторную передачу блока данных.

В регистре состояния КПДП четыре младших разряда КБ3-0 фиксируют сигналы окончания передачи блока данных в соответствующих каналах. Содержимое разрядов КБ3-0 автоматически обнуляется при считывании микропроцессором содержимого регистра состояния.

Признак модификации ПМ приобретает значение 1 в режиме автозагрузки (А3 = 1) на период передачи параметров из регистров канала 3 в соответствующие регистры канала 2, т. е. после окончания передачи первого блока данных. По окончании модификации регистров канала 2 признак модификации ПМ регистра состояния обнуляется. Пока ПМ=1, инициализация КПДП на передачу новых блоков данных должна быть запрещена. При считывании регистра состояния признак ПМ сохраняет свое значение. Сброс ПМ осуществляется загрузкой нового УС режима КПДП, в котором разряд автозагрузки АЗ = 0. На периоды инициализации и считывания КПДП прерывания в системе должны быть запрещены командой DI.

Контроллер ПДП после инициализации может работать в трех режимах: считывание (передача из ОЗУ во внешнее устройство), запись (передача из внешнего устройства в ОЗУ) и проверка канала ПДП (считывание содержимого канальных регистров для программного анализа).