- •Введение

- •1 Расшифровка и анализ задания

- •2.3.3 Организация ввода/вывода информации. Архитектура процессора содержит 27 резидентных линий ввода-вывода, организованных в три 8-разрядных порта bus, p1, p2

- •2.4 Разработка уточненной структурной схемы

- •3.2 Модуль пзу к541рт2

- •3.3 Подключение озу и пзу к системной шине

- •3.4 Многорежимный буферный регистр к589ир12

- •5 Разработка алгоритма работы мпс

- •6 Реализация контроллера магнитофона на основе оэвм к1816ве48

- •Заключение

- •Список использованных источников

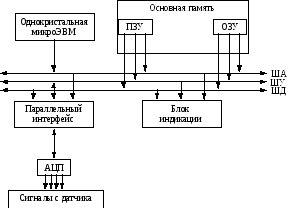

2.4 Разработка уточненной структурной схемы

Для создания управляющей микроЭВМ на базе однокристальной микроЭВМ необходимы следующие устройства:

-

память, состоящая из ПЗУ и ОЗУ;

-

параллельный интерфейс;

-

аналогово-цифровой преобразователь (АЦП) для преобразования аналоговых сигналов с датчиков в цифровые;

-

блок индикации.

Уточненная структурная схема микроЭВМ представлена на рисунке 6.

В качестве параллельного интерфейса выбрана микросхема К580ВВ55.

В качестве АЦП выбрана К1113ПВ1.

В качестве ОЗУ и ПЗУ выбраны соответственно КР132РУ6 и К541РТ2.

В качестве индикаторов выбраны АЛС321А, подключаемые через дешифратор К514ИД1.

Рисунок 6 – Уточненная структурная схема микроЭВМ

В рассматриваемой системе в контролере прямого доступа к памяти нет необходимости, так как реализуется система автоматического регулирования технологического процесса, и простое снятие показаний с датчика без обработки из на микропроцессоре и последующей записью данных в память в данной системе не применяется.

3 РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

3.1 Модуль ОЗУ КР132РУ6

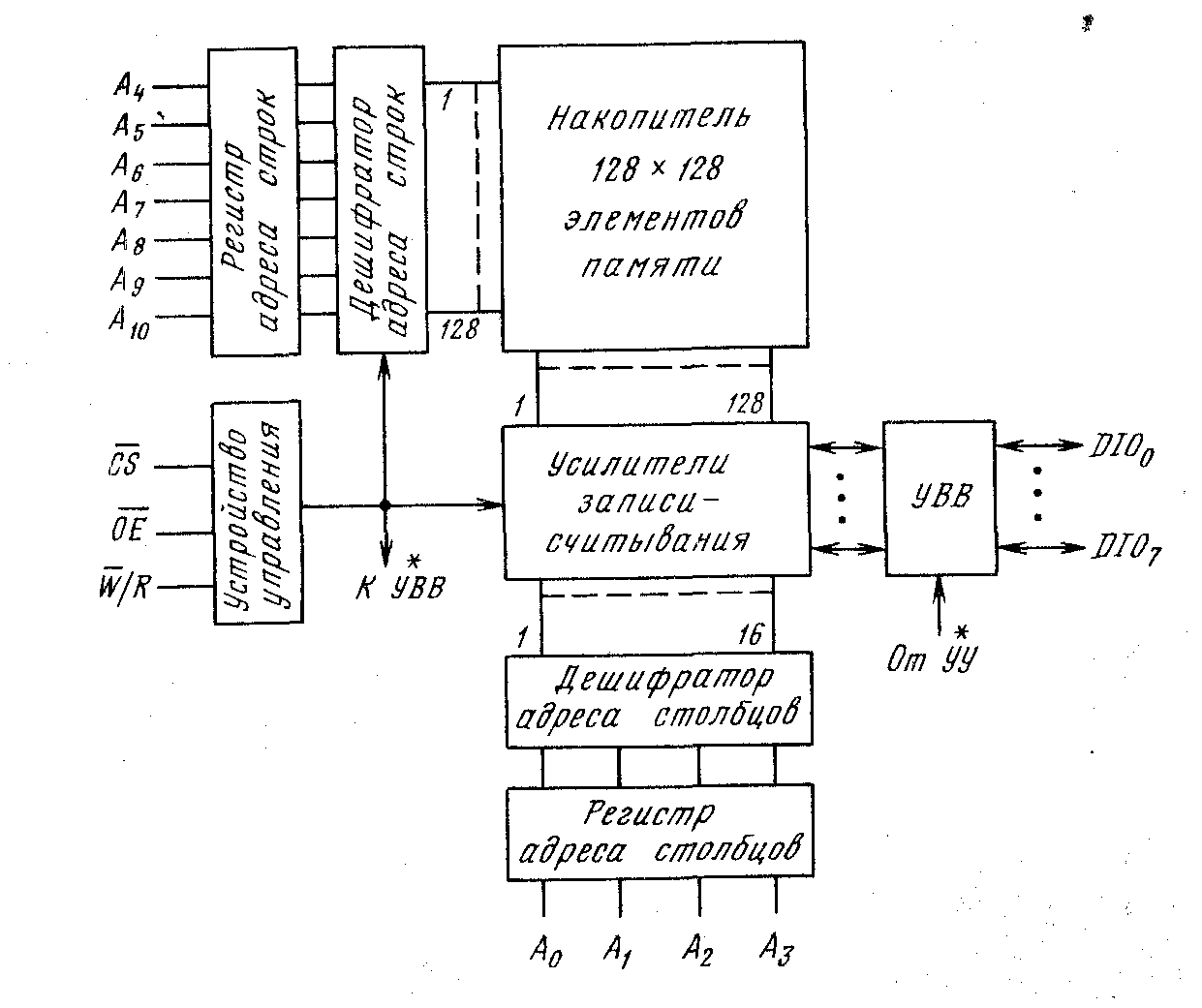

Для расширения памяти программ микроконтроллера в соответствии с заданием выберем КР132РУ6. Назначение выводов данной микросхемы приведено на рисунке 8. Структура статической ОЗУ показана на рисунке 7. Назначение выводов БИС ОЗУ КР132РУ6 представлено в таблице 3.

Рисунок 7 — Структура микросхемы статической ОЗУ

КР132РУ6 - микросхема статических ОЗУ высокого быстродействия: время цикла обращения лежит в диапазоне значений 55 ... 85 нс. Микросхема выполнена по n-канальной МДП-технологии. Основные электрические параметры микросхемы приведены в таблице 4.

Однако у микросхем серии К132 имеются ряд общих свойств, важных для их практического использования: единое напряжение питания 5 В, ТТЛ входные и выходные уровни напряжений О В: входные — соответственно не более 0.8 В, не менее 2 В, выходные не более 0,4 В, не менее 2,4 В; наличие выходов стремя состояниями, единая система сигналов управления: CS, W/R; способность работать на большую емкостную нагрузку (от 100 до 600 пФ для разных типов микросхем), возможность снижения уровня энергопотребления при переходе в режим хранения в 3—5 раз, а у некоторых микросхем до 20 раз.

Таблица 3 - Описание выводов БИС ОЗУ К134РУ6

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

DO |

8 |

Выход данных |

|

А (0-13) |

1; 2; 3; 4; 5; 6; 7; 13; 14 15; 16; 17; 18; 19 |

Входы данных с локальной шины МП |

|

W/R |

9 |

Вход сигнала чтения/записи в память |

|

DI |

12 |

Вход адресных данных |

|

CS |

11 |

Выбор микросхемы; L-уровень сигнала подключает ОЗУ к системной шине |

|

5 V |

20 |

Напряжение питания (+5 В) |

|

0 V |

10 |

Напряжение питания (0 В) |

Таблица 4 - Основные электрические параметры микросхемы К134РУ6

|

Название параметра |

Значение параметра |

|

Емкость |

16 Кх1 |

|

Напряжение питания в статическом режиме |

Ucc=5±0,5 В |

|

Время выборки |

70 нс |

|

Потребляемая мощность |

440 мВт |

|

Тип корпуса |

2140.Ю.20-3 |

По своей структуре микросхемы серии К132 близки к микросхемам рассмотренных серий К561, К537: они состоят из накопителя матричного типа, регистров и дешифраторов кода адреса, устройства ввода-вывода, блока ключей выбора строк и столбцов. В реализации названных элементов структурной схемы также имеется много общих решений. В частности, все входы - адресные, управляющие, информационные, имеют усилители, настроенные по схеме инвертора на двух транзисторах VТ1, VТ2 с защитой в виде резистивно-транзисторной цепи R, VТЗ. Охранный транзистор VТ3 своим p-n переходом сток-подложка предохраняет вход транзистора VТ3 от действия статического электричества и защищает от резких бросков напряжений на входах своей выходной емкостью, которая вместе с резистором образует интегрирующую цепочку..

Входные усилители-формирователи обладают высоким быст родействием, которое обеспечено выбором режима работы транзистора VТ2 и напряжением смещения подложки Uсм = - 2,7 В. Транзистор VТ2, имеющий встроенный канал n-типа, нормально открыт и при выключении VТ1 переходит в режим генератора тока, заряжая за короткое время выходную емкость. При включении VТ1 емкость также быстро разряжается через низкоомный канал открытого транзистора VТ1.

Рисунок 8 – Микросхема ОЗУ КР132РУ6

Напряжение отрицательного смещения р-подложки формирует встроенный в кристалл преобразователь из напряжения питания микросхемы 5 В. Это напряжение уменьшает порог включения транзисторов и снижает уровень токов утечки внутри кристалла.

В качестве ЭП применяют статический триггер на четырех транзисторах VТ1 — VТ4 и двух ключевых транзисторах VТ5, VТ6, затворы которых соединены с адресной шиной, а стоки — с разрядными шинами. При Хi = 1 ключевые транзисторы открываются и подключают триггер к разрядным шинам. При записи разрядные шины передают свой потенциал узловым емкостям С и обеспечивают переключение триггера в состояние, соответствующее записываемой информации. Этот процесс описан при рассмотрении работы КМДП-триггера. Аналогично обращение к ЭП происходит и при считывании, только теперь свой потенциал передает триггер высокоомным разрядным шинам.

Отличительной особенностью структуры микросхем памяти n-МДП-типа, в частности микросхем серии К132, является наличие в каждом столбце усилителя записи-считывания триггерного типа. Усилитель управляется внутренним сигналом Р: при его поступлении транзистор VТ5 открывается и уравнивает потенциалы двух входов-выходов триггера. В этом и заключается подготовка усилителя к приему информации. При считывании информации с выбранного ЭП на разрядных шинах РШ0, РШ1 создается асимметрия потенциалов, которая оказывает воздействие на состояние плеч усилителя, подключенного к этим разрядным шинам. В момент снятия сигнала Р, когда транзистор VТ5 закрывается, вносимая разрядными шинами асимметрия потенциалов определит состояние, в которое переключится триггер-усилитель. В результате слабый информационный сигнал, полученный с выхода ЭП, будет усилен и передан в устройство ввода-вывода. Усилитель составлен из транзисторов, отличающихся от транзисторов ЭП более высоким уровнем токов. Одновременно с усилением считываемого сигнала триггер-усилитель предотвращает возможность разрушения информации в выбранном ЭП, так как обеспечивает восстановление (регенерацию) заряда узловых емкостей триггера ЭП.

В некоторых микросхемах, например в КР132РУ6, К132РУ10 и др., ЭП выполнен на триггере, в котором вместо нагрузочных транзисторов сформированы высокоомные (до 109 Ом) резисторы. При такой технологии удается обеспечить более высокий уровень интеграции и, следовательно, увеличение информационной емкости микросхемы памяти. Кроме того, снижается потребляемая микросхемой мощность в режиме хранения.

Применение высокоомных резисторов в схеме триггера оказалось возможным благодаря усовершенствованию n-канальной технологии и снижению на этой основе паразитных токов утечки в структуре кристалла до значений пикоампер. Выходные каскады микросхем построены по схеме инверторов с тремя состояниями, формирующими ТТЛ-уровни.

Микросхемы серии К132 работают в режимах записи, считывания и хранения. Таблица истинности микросхемы КМ132РУ8 имеет отличия, обусловленные тем, что у этой микросхемы входы и выходы совмещены. Микросхема КР132РУ6 имеет дополнительно к названным режим «Считывание-модификация-запись».

При реализации названных режимов следует учитывать требования к форме представления сигналов управления: сигнала разрешения выбора микросхемы С5 и сигнала режима обращения W/R. По этому признаку, микросхемы статических ОЗУ делят на асинхронные и тактируемые. Микросхемы КР132РУ4А, Б, КМ132РУ5А, Б и КР132РУ6А, Б являются тактируемыми (КМ132РУ5А, Б — только в режиме записи), остальные микросхемы этой серии — асинхронные. Напомним, что при записи и считывании информации у тактируемых микросхем сигнал С5 или W/R подается импульсом. У микросхем КР132РУ4 и КР132РУ6 адресные, управляющие и информационные сигналы фиксируются («защелкиваются») на входных усилителях-триггерах по отрицательному перепаду сигнала СS. Поэтому для этих микросхем необходимо обеспечить требуемое время удержания названных сигналов относительно сигнала СS для их «захвата» входными триггерами. После фиксации сигналы могут принимать произвольные значения, например значения для следующего цикла обращения.

У микросхем асинхронных ОЗУ сигналы С5 и W/R можно подавать уровнем 0 или 1. В таком случае временные процессы в микросхеме определяют адресные сигналы. В асинхронных микросхемах управляющие сигналы можно подавать и импульсами. Тогда надо принимать во внимание требования к их минимальной длительности.

Режим «Считывание-модификация-запись» совмещает в себе два режима и обеспечивает считывание информации из выбранного ЭП и запись в этот же ЭП новой информации в одном цикле. Время цикла обращения к микросхеме в том режиме больше для КР132РУ6. Увеличивается и число учитываемых временных параметров.

В режиме хранения у многих микросхем серии К132 наблюдается снижение в 3—5 раз тока потребления. У микросхем К134РУ6 и КМ132РУ8 возможно многократное (более чем в 10 раз) снижение потребляемой мощности за счет выключения напряжения питания, но сохранения его уровня 5 В на выводе СS. В этом режиме через вход СS осуществляется питание только накопителя и формирователя напряжения смещения подложки, остальные функциональные узлы микросхемы находятся в выключенном состоянии.