- •Введение

- •Xseg Пространство внешней памяти;

- •2.1.7 Система прерываний. Упрощенная схема прерываний мк51 приведена на рисунке 6.

- •2.2.5 Работа с портами. Порты р1 - р3 имеют идентичные характеристики. Данные, записанные в них, статически фиксируются и не изменяются до перезаписи.

- •2.3 Упрощенная структурная схема разрабатываемой микропроцессорной системы

- •3.2 Описание микросхемы бис пзу к541рт2

- •3.3 Подключение озу и пзу к системной шине

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5.3 Режимы работы клавиатуры.

- •4.6 Уточненная схема управляющей микроЭвм

- •5.2 Разработка блок-схемы управляющей системы

- •6 Реализация устройства на базе микропроцессора к1816ве51

- •6.2 Устройство

- •Список использованной литературы

Xseg Пространство внешней памяти;

CSEG Пространство программного кода.

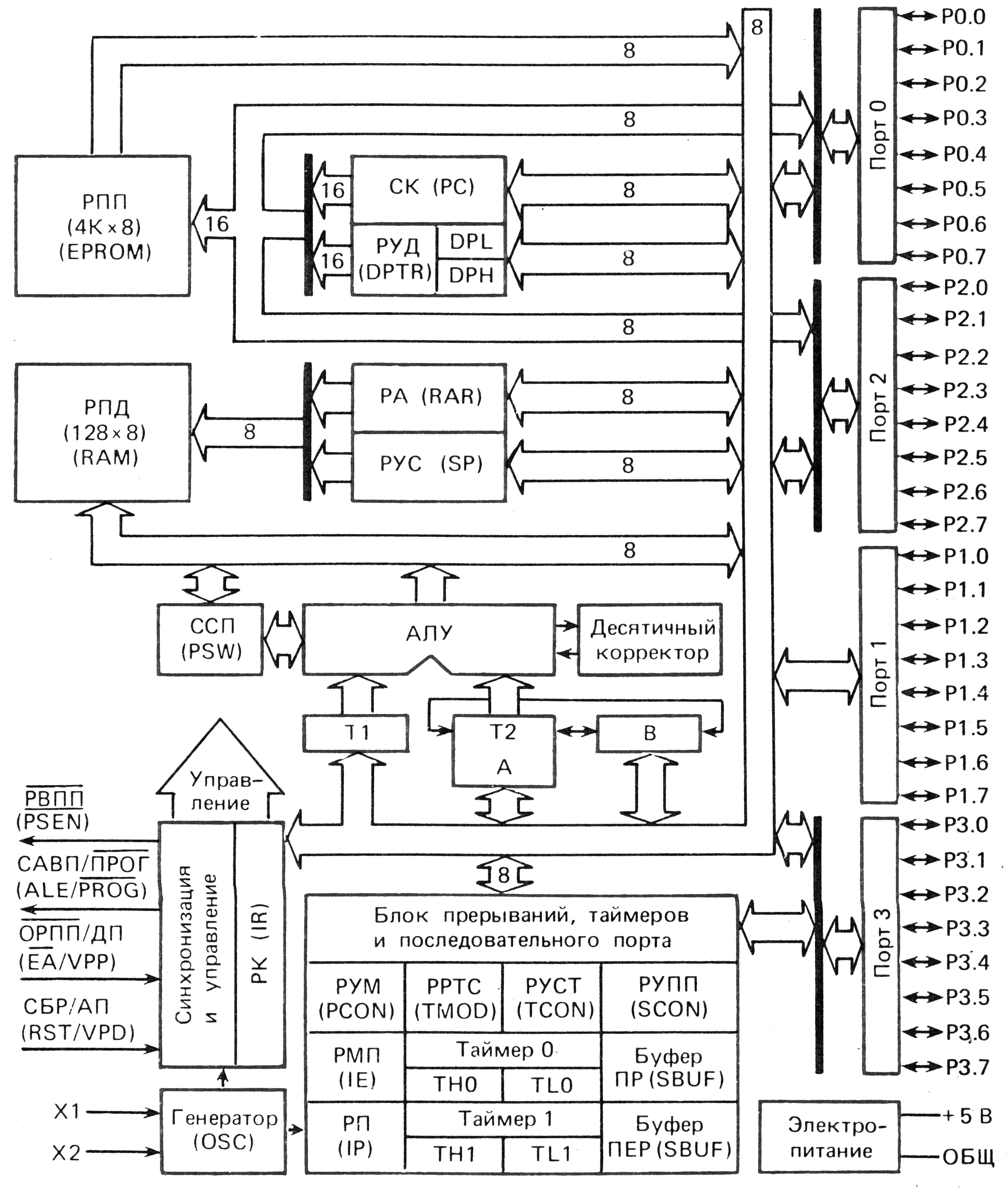

Рисунок 2 – Структурная схема МК51

Однако пространство регистров, за исключением PC, и пространство битов, частично пересекаясь, физически совмещаются с пространством DSEG, образуя единую внутреннюю среду для хранения данных, имеющую достаточно сложную структуру. Это стандартный для однокристальных МС прием, позволяющий одни и те же физические данные рассматривать с разных позиций. В результате выбирается наиболее удобный для конкретного случая способ интерпретации тех или иных данных, в соответствии с которым и организуется доступ к ним.

АЛУ МК51 реализует достаточно мощную систему команд, включащую

команды умножения, деления, вычитания, выполнения операций над битами, команды управления. Большинство команд имеют формат один или два байта и выполняются за один или два машинных цикла длительностью 1 мкс (при тактовой частоте 12 МГц). Память программ и память данных физически и логически разделены. Кроме того, к адресному пространству РПД примыкает адресная область регистров специальных функций, включающая в себя: аккумулятор (АСС), слово состояния программы (PSW), указатель стека (SP), указатель данных (DPTR), порты (Р0 - Р3), регистр приоритетов (IP), регистр маски прерываний (IE), регистр режимов таймеров-счетчиков (TMOD), таймеры-счетчики (Т0, Т1), регистр управления и буфер приемопередатчика (SCON и SBUF) и др. Для побайтового ввода-вывода информации в МК51 могут быть использованы четыре порта (Р0 - Р3). Помимо того, выводы порта Р3 (контакты 10-17) могут быть настроены для реализации альтернативных функций (таблице 1) записью в соответствующие разряды порта логической единицы. В случае применения внешней памяти данных (ВПД) или программ (ВПП) используются выходные буферы портов Р0 и Р2. При этом через порт 0 в режиме мультиплексирования выводится младший байт адреса ВПД или ВПП, а затем осуществляется передача данных. Если разрядность адреса составляет более 8 бит, то через порт Р2 происходит выдача его старших разрядов.

Специальный сброс МК51 осуществляется подачей единицы на вход RST в течение по меньшей мере двух машинных циклов. При этом сбрасывается содержимое счетчика команд и всех регистров специальных функций, в регистр указателя стека записывается число 07Н, а в порты - 0FFH. После снятия сигнала RST запускается программа по адресу 0000H.

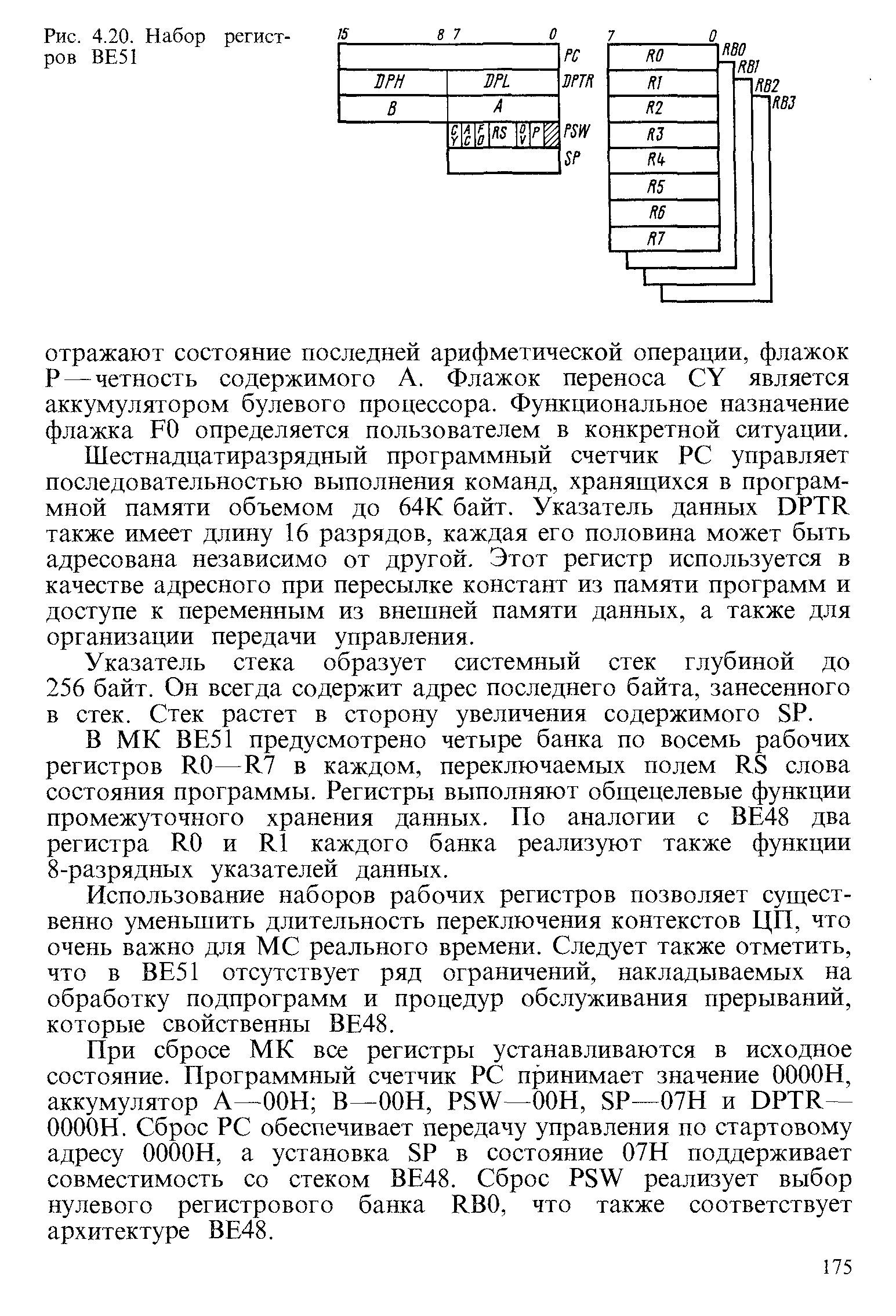

2.1.2 Набор регистров МК51. Набор программно-доступных регистров процессора ВЕ51 приведен на рисунке 3. Архитектура относится к классу аккумуляторных с переключаемыми банками рабочих регистров. Поэтому центральным регистром набора считается 8-разрядный аккумулятор А, выполняющий обычные функции основного арифметического регистра.

Рисунок 3 - Набор регистров МК51

В МК ВЕ51 предусмотрено четыре банка по восемь рабочих регистров

R0 - R7 в каждом, переключаемых полем RS слова состояния программы. Регистры выполняют общецелевые функции промежуточного хранения данных. По аналогии с ВЕ48 два регистра R0 и R1 каждого банка реализуют также функции 8-разрядных указателей данных.

Использование наборов рабочих регистров позволяет существенно уменьшить длительность переключения контекстов ЦП, что очень важно для МС реального времени. Следует также отметить, что в ВЕ51 отсутствует ряд ограничений, накладываемых на обработку подпрограмм и процедур обслуживания прерываний.

При сбросе МК все регистры устанавливаются в исходное состояние. Программный счетчик PC принимает значение 0000Н, аккумулятор А - 00Н; В - 00Н, PSW - 00Н, SP - 07H и DPTR - 0000Н. Сброс PC обеспечивает передачу управления по стартовому адресу 0000Н, а установка SP в состояние 07Н поддерживает совместимость со стеком ВЕ48. Сброс PSW реализует выбор нулевого регистрового банка RB0.

Регистр В служит расширением аккумулятора А, необходимым для осуществления операций умножения и деления, причем он является как источником, так и приемником операндов. Во всех других операциях регистр В выполняет функции, определяемые пользователем.

Регистр слова состояния программы кроме флажков, входящих в PSW МК51:

PSW.7 CY Перенос из старшего разряда АЛУ;

PSW.6 АС Дополнительный перенос из младшей тетрады АЛУ;

PSW.5 F0 Флажок пользователя общего назначения включает также флажки;

PSW.2 OV Признак арифметического переполнения результата PSW.1;

Р Признак четности.

Сюда же входит двухразрядное поле RS (Registers Select) выбора одного из четырех возможных банков рабочих регистров. Флажки признаков результата CY, АС и OV, как правило, отражают состояние последней арифметической операции, флажок Р - четность содержимого А. Флажок переноса CY является аккумулятором булевого процессора. Функциональное назначение флажка F0 определяется пользователем в конкретной ситуации.

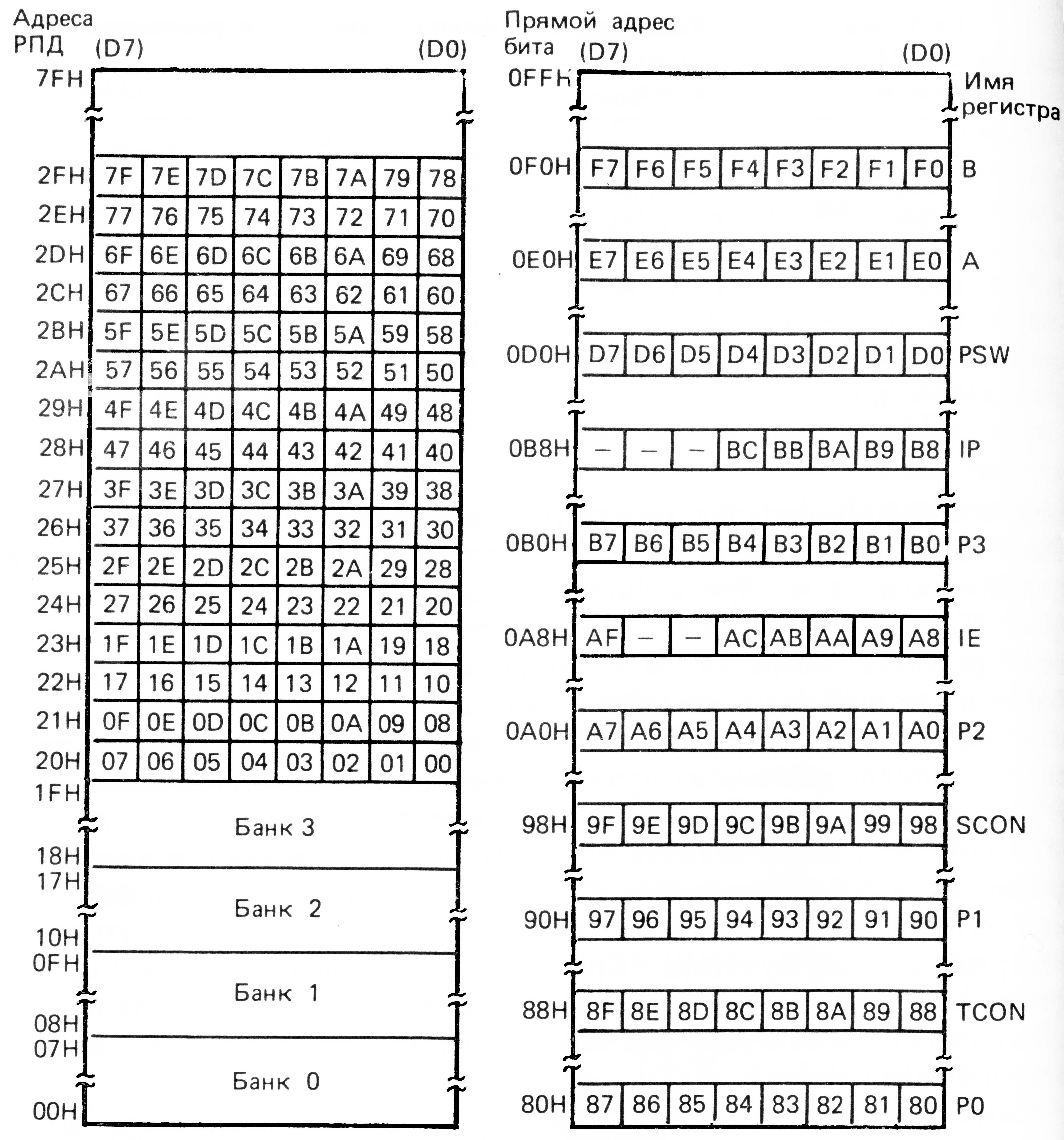

2.1.3 Организация памяти МК51. Пространство внутренней памяти DSEG имеет общий объем 256 байт. Однако организация МК51 предусматривает реализацию только первой его половины (128 байт). Все банки рабочих регистров, а также системный стек в МК ВЕ51 располагаются во внутренней памяти данных и могут рассматриваться как обычные ячейки памяти. Существуют два способа адресации памяти данных МК: прямой и косвенный через регистры R0, R1 выбранного в данный момент одного из банков RB0 - RB3. При прямой адресации доступна только младшая половина адресного пространства внутренней памяти данных (128 байт), при косвенной обеспечивается доступ к любой ее ячейке (256 байт). Введение прямой адресации значительно расширило возможности обработки данных МК, в частности появились средства прямого доступа в соседние регистровые банки и стек системы, интерпретируемые как обычные ячейки памяти. Карты адресов отдельных бит представлены на рисунке 4.

Микроконтроллер BE51 имеет мощную и развитую подсистему ввода-вывода (ВВ) и средства поддержки режима реального времени. Для их управления в МК предусмотрен ряд регистров, которые размещаются во второй половине прямо адресуемого пространства, образующей пространство специальных регистров (128 байт). Сюда же включены порты и основные регистры ЦП.

а) б)

а) – карта адресуемых бит в резидентной памяти данных; б) – карта адресуемых бит в блоке регистров специальных функций

Рисунок 4 - Карты адресов отдельных бит МК BE51

Центральный процессор МК51 содержит специальную логику, предназначенную для выполнения нескольких однобитовых операций, булев или одноразрядный процессор для вычисления булевых выражений. В основу булева процессора положен стандартный аккумуляторный принцип организации. В данном случае роль аккумулятора выполняет флажок переноса CY.

Для хранения булевых данных в архитектуре ВЕ51 предусмотрено специальное одноразрядное линейно упорядоченное пространство BSEG объемом 256 байт, которое физически совмещено с байтовым пространством данных DSEG. При этом одна часть пространства BSEG попадает на обычные ячейки памяти DSEG и может рассматриваться как область общего назначения. Обычно она используется для хранения булевых переменных. Другая часть пространства BSEG попадает на ячейки памяти, совмещенные с регистрами МК, что обеспечивает независимый доступ к их отдельным разрядам. В булевом пространстве определена только прямая адресация bit.

В МК ВЕ51 имеется возможность совмещения внешней части CSEG с пространством XSEG. Такое совмещение поможет распространить на область CSEG операции и способы доступа к XSEG, в частности станет осуществимой операция записи, что может быть использовано при загрузке программ из внешней памяти.

2.1.4 Порты ввода-вывода. Подсистема ввода-вывода (ВВ) МК ВЕ51 размещается непосредственно на кристалле. Для ВВ данных и управления процессом их передачи в состав МК введен ряд портов данных и регистров управления/состояния, совокупность которых образует набор специальных регистров (рисунок 5).

Рисунок 5 - Специальные регистры МК BE51

Физическая система ВВ микроконтроллера ВЕ51 состоит из четырех двунаправленных 8-разрядных портов Р0 - РЗ. Все порты ВВ отображены в пространстве внутренней памяти DSEG по адресам 80Н, 90Н, ОАОН, ОВОН и ничем не отличаются от обычных ячеек памяти.

Каждый из портов содержит фиксатор и буфер. Фиксатор представляет собой 8-ми разрядный регистр, имеющий байтовую и битовую адресацию для установки (сброса) разрядов с помощью программного обеспечения. Физические адреса фиксаторов Р0, Р1, Р2, Р3 составляют для:

Р0 - 80Н, при битовой адресации 80Н-87Н;

P1 - 90H, при битовой адресации 90Н-97Н;

P2 - A0H, при битовой адресации А0Н-А7Н;

P3 - B0H, при битовой адресации В0Н-В7Н.

Порты Р1, Р2, Р3 в установившемся состоянии имеют внутреннее сопротивление, обеспечивающее ток нагрузки в диапазоне от 800 мкА до 80 мА при входном напряжении от 0,45 В до 2,4 В.

При переключении входной информации на порт с низкого уровня на

высокий на время, равное одному состоянию (2 периода), подключается форсирующий транзистор, уменьшающий внутреннее сопротивление буфера, в результате чего уменьшается длительность фронта и задержка выходного сигнала.

Порт Р0 отличается от остальных отсутствием внутреннего сопротивления.

Расширение пространства ВВ может быть выполнено за счет области XSEG или другими средствами с помощью самих портов Р0 - РЗ и SBUF.

2.1.5 Последовательный канал связи. В состав ВЕ51 входит дуплексный канал последовательной связи с буферизацией, который может быть запрограммирован для работы в одном из четырех режимов:

режим 0 - синхронный последовательный ВВ со скоростью OSC/12;

режим 1- асинхронный с 10-битовым кадром и переменной скоростью передачи;

режим 2 - асинхронный с 11-битовым кадром и фиксированной скоростью передачи OSC/32 или OSC/64;

режим 3 - асинхронный с 11-битовым кадром и переменной скоростью передачи.

Входные и выходные данные хранятся в буферном регистре SBUF с адресом 99Н. Управление работой приемопередатчиков осуществляется через слово управления и состояния SCON, расположенное в регистре по адресу 98Н.

2.1.6 Таймеры/счетчики. Предназначены для подсчета внешних событий, для получения программно управляемых временных задержек, выполнения времязадающих функций ОМЭВМ.

В состав блока входят:

- два 16-ти разрядных регистра Т/С 0, Т/С 1;

- 8-ми разрядный регистр режимов Т/С (ТМ0D);

- 8-ми разрядный регистр управления (ТСОN);

- схема инкремента;

- схема фиксации INT0, INT1, Т0, Т1;

- схема управления флагами;

- логика управления Т/С.

Два 16-разрядных регистра Т/С 0 и Т/С 1 выполняют функцию хранения содержимого счета. Каждый из них состоит из пары 8-ми разрядных регистров, соответственно ТH0, ТL0 и ТH1, ТL1. Причем регистры ТН0, ТH1 - старшие, регистры ТL0, ТL1 - младшие 8 разрядов. Каждый из 8-ми разрядных регистров может быть использован, как РОН, если Т/С не используются (бит TR0 для Т/С 0 и бит TR1 для Т/С 1 в регистре управления TCON равен "0").

Регистр режимов Т/С (TMOD) предназначен для приема и хранения кода, определяющего:

- один из 4-х возможных режимов работы каждого Т/С;

- работу в качестве таймеров или счетчиков;

- управление Т/С от внешнего вывода.