- •Введение

- •1 Расшифровка и анализ задания

- •Регистр флагов f

- •2.2 Сравнение z80 с аналогами

- •2.3 Разработка упрощенной структурной схемы микропроцессорной

- •3.2 Описание микросхемы бис пзу к541ре1

- •4.2 Выбор генератора тактовых импульсов

- •4.3 Выбор системного контроллера и шинного формирователя

- •4.4 Интервальный таймер кр580ви53

- •4.5 Программируемый блок приоритетного прерывания кр580вн59

- •4.6 Аналого-цифровой преобразователь к572пв3

- •4.7 Выбор цап

- •4.8 Выбор дешифратора

- •4.9 Контроллер прямого доступа к памяти кр580вт57

- •4.10 Уточненная структурная схема микропроцессорной системы

- •5 Разработка алгоритма управляющей программы

- •Заключение

- •Список литературы

Введение

В настоящее время практически невозможно указать какую-то отрасль науки и производства, в которой бы не использовались микропроцессоры (МП) и микро ЭВМ. Применение МП привело к замене физического схемного метода реализации заданных функций математическим программным методом, представляющим большие возможности, снимается ряд физических ограничений при реализации различных функций, обеспечивается независимость характеристик от физических условий применения. Важным свойством микропроцессорной техники является её высокая гибкость, возможность быстрой перенастройки при изменении алгоритмов управления, перенастройка осуществляется программным способом. Микропроцессорная техника позволяет реализовать системы, функциональные возможности которых могут наращиваться по мере необходимости или по мере появления новых технических средств, тем самым обеспечивается соответствие технического уровня микропроцессорных систем управления самым современным требованиям в течении длительного времени.

Микропроцессорные средства позволяют создавать разнообразные по сложности выполняемых функций устройства управления – от простейших микроконтроллеров несложных приборов и механизмов до сложнейших специализированных и универсальных систем распределенного управления в реальном времени. Благодаря различию комплектаций, производительности и объема оборудования модулей они создают аппаратурную основу для разработки систем, ориентированных на различные области применения, и инструментальных комплексов для отладки их программ.

Целью курсового проекта является разработка управляющей микропроцессорной системы, реализующая заданные взаимодействия с объектом управления (ОУ) и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

1 Расшифровка и анализ задания

Управляющая микро ЭВМ проектируется на базе однокристальной микро ЭВМ и включает в себя следующие основные устройства:

-

процессорный модуль;

-

память, состоящую из ОЗУ и ПЗУ;

-

устройства параллельного ввода/вывода для связи с ОУ;

-

блок последовательного канала для связи с ЭВМ верхнего уровня;

-

программируемый системный таймер;

-

контроллер прерываний;

-

контроллер прямого доступа в память;

-

пульт управления.

Базовый микропроцессор (микро ЭВМ), на основе которого требуется построить управляющую микро ЭВМ – Z80.

Тип БИС, на которой должен быть реализован блок оперативного запоминающего устройства (ОЗУ) – К537РУ8.

Тип БИС, на которой должен быть реализован блок постоянного запоминающего устройства (ПЗУ) – К541РЕ1.

Обработка информации от цифровых датчиков и выдача управляющего воздействия y1 производится путем ввода значений х1, х2, х3, х4 и вычисления значения булевой функции f1(х1, х2, х3, х4).

При единичном значении f1 вырабатывается управляющий сигнал y1=1 длительностью t1. Это значит, что через t1 после выдачи y1 = 1 необходимо выработать y1=0.

При обработке информации с аналоговых датчиков ПМ принимает коды NU1, NU2 с выходов АЦП и код константы К с регистра пульта управления. Далее вычисляется значение функции NU=f2 (NU1, NU2, К) и сравнивается с константой Q, хранящейся в ПЗУ. В зависимости от результатов сравнения вырабатывается (аналогично у1) один из двух двоичных управляющих сигналов у2 или у3 заданной длительности по следующему правилу: если NU < Q, то выдать у2 длительностью t2, иначе выдать у3 длительностью t3.

Далее формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3 и производится вычисление по формуле:

Y4=A0+AlNU3.

Значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

Все двоичные переменные и константы, участвующие в вычислениях: NU1, NU2, NU3, К, Q, Ао, A1, Y4 рассматриваются как целые без знака.

После выдачи всех управляющих воздействий проверяется состояние тумблера "СТОП" на пульте управления. Если СТОП=0, цикл управления начинается с начала, иначе выполняется процедура останова системы, включающая следующие действия: формируется сигнал установки системы в исходное состояние путем подачи на линию начальной установки интерфейса двух прямоугольных импульсов длительностью 30 мкс интервалом 30 мкс; выполняется команда процессора СТОП.

Алгоритм управления, заданный видом функцией:

Управляющее

воздействие

, длительность управляющих сигналов t1

= 20 c;

, длительность управляющих сигналов t1

= 20 c;

NU = min(NU1; NU2+K), длительность управляющих сигналов t2=70 c, t3=150 c.

В системе необходимо предусмотреть следующие линии запроса на внешние прерывания:

INT0 - отказ источника питания;

INT1 - сигнал ха аварийного датчика ОУ;

INT2 - запрос от пульта управления (прерывание оператора);

INT3 - запрос от микро ЭВМ верхнего уровня.

Запросы на прерывания приведены в порядке убывания приоритетов (INT0 - высший приоритет). Система должна реагировать на запросы следующим образом:

INT0 - вырабатывается сигнал установки системы в исходное состояние; выполняется команда СТОП.

INT1 - на пульте управления включается аварийная сигнализация (световая с частотой 2Гц или звуковая с частотой 500Гц); на индикацию пульта выдается состояние двоичных датчиков х1, х2, х3, х4 и цифровой код NU1; выполняется команда СТОП.

INT2 - выдается на индикацию значения следующих булевых переменных: функция fl, результат сравнения NU<=Q, значение выражения xl&х2&х3&х4, значение выражения xlvx2vx3vx4; выдается на индикацию значение сохраняемой в ПЗУ константы Q; организуется выход из прерывания на начало цикла управления.

INT3 - выдать в последовательный канал следующую информацию:

-

код символа '!' ("Внимание!");

-

двухзначный номер абонента (номер студента в списке группы) ;

-

максимальное значение Y4, вычисленное за период от предыдущего сеанса связи до текущего цикла управления;

-

минимальное значение Y4 за тот же период;

-

код символа '#' ("Конец передачи").

Кроме перечисленных, в системе могут использоваться прерывания от внешних устройств, обеспечивающих связь с ОУ, системного таймера и канала последовательного обмена.

2 РАЗРАБОТКА ПРОЦЕССОРНОГО МОДУЛЯ, ИНТЕРФЕЙСА,

УПРОЩЕННОЙ СТРУКТУРНОЙ СХЕМЫ

2.1 Разработка процессорного модуля и интерфейса

Микропроцессор Z80 был разработан фирмой Zilog в 1976 году и стал, вероятно, наиболее мощным из 8-разрядных микропроцессоров. Его популярности способствовало сохранение полной совместимости “снизу вверх” на уровне системы команд с микропроцессором 8080 фирмы Intel (советский аналог – КР580ВМ80А), к тому времени ставшим де-факто мировым стандартом на 8-разрядный микропроцессор.

В нашей стране Z-80 известен прежде всего по игровым компьютером Sinclair Spectrum, чрезвычайно популярным во второй половине 1980-х годов. Однако спектр применения этого микропроцессора был намного шире. В частности, именно он является “мозгом” французских противокорабельных ракет “Exocet” (в 1982 году такой ракетой аргентинский истребитель “Мираж” потопил английский эскадренный миноносец “Шеффилд” – один из наиболее современных на тот момент боевых кораблей).

2.1.1 Основные характеристики микропроцессора Z80. Z80 является однокристальным микропроцессором третьего поколения, оперирующим 8-разрядными данными и 16-разрядными адресами. Максимальный объём прямо адресуемой памяти и прямо адресуемого пространства ввода вывода – по 64 Кбайта (пространство ввода-вывода микропроцессора 8080 составляет 256 байт).

Система команд микропроцессора Z80 включает 158 инструкций, из которых 78 полностью аналогичны командам микропроцессора 8080, хотя и имеют другие мнемоники. Помимо традиционных для 8-разрядных микропроцессоров арифметико-логических команд, у Z80 имеются инструкции,

работавшие с отдельными битами, а также облегчающие обработку смвольной информации. Выпускались микропроцессоры с различными рабочими тактовыми частотами от 2,5 до 8 МГц (у 8080A – 2,5 МГц), что обеспечивало очень высокое по тем временам быстродействие (команда сложения типа “регистр–регистр” выполнялась за 4 такта, что на частоте 8 МГц составляло 2 млн. операций в секунду). Советский аналог Z80 – микропроцессор КР1858ВМ1 – работает на тактовой частоте 4 МГц.

Микропроцессор содержит два идентичных набора регистров общего назначения по сравнению с единственным набором процессора 8080. Благодаря наличию двух наборов регистров обеспечивается быстрое переключение контекста при обработке прерываний. Кроме того, по сравнению с прототипом были добавлены два 16-разрядных индексных регистра, что позволило расширить набор методов адресации операндов в памяти.

Z80 поддерживает три схемы организации обработки прерываний, в том числе режим совместимости с микропроцессором 8080. Правда, для согласования микропроцессора Z80 с контроллером прерываний 8259 фирмы Intel требуются дополнительные схемы, т.е. режим совместимости оказался не совсем “совместимым”.

Наконец, на самом кристалле микропроцессора реализован счётчик регенерации динамической памяти, что позволяет резко сократить количество деталей в простых микрокомпьютерах по сравнению с 8080.

2.1.2 Структурная схема и ее описание. Микропроцессор Z80 выпускался в 40-выводном DIP-корпусе, наиболее распространённом для восьмиразрядных микропроцессоров. В отличие от микропроцессора 8080 фирмы Intel, Z80 для своей работы не требует специфических дополнительных схем (двухфазного тактового генератора и системного контроллера), что значительно упрощает конструкцию процессорного модуля. Кроме того, для работы Z80 требует единственное напряжение питания +5 В вместо трёх напряжений для 8080 (+5, –5 и +12 В).

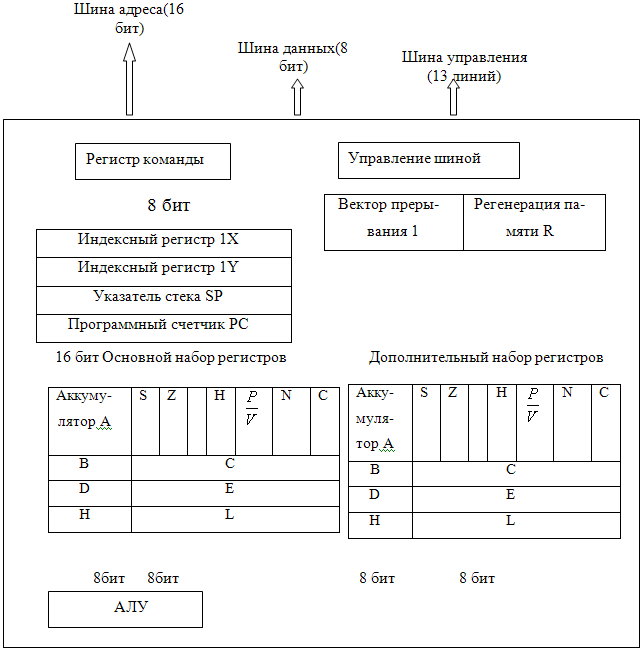

Организация МП Z80 отмечена следующими основными особенностями:

- трехшинной структурой с шинами адреса, данных и управления;

- наличием регистровой памяти, образованной программно доступными общими и специализированными регистрами, а также регистрами временного хранения;

- наличием двух (главного и вспомогательного) аккумуляторов, флаговых регистров и наборов РОН;

- магистральным принципом связей, реализованным в виде связывающей основные узлы МП двунаправленной шины данных, имеющей ширину, равную длине слов, обрабатываемых микропроцессором (8 разрядов);

- наличием 16-разрядной шины адреса обеспечивающей возможность прямой адресации любого байта в памяти емкостью 64 Кбайт; Z80 имеет два набора восьмиразрядных регистров (А - L) и столько же флаговых регистров (F). В каждый момент активен и программно доступен только один набор. Переключаются они программным путем, при этом содержимое регистров сохраняется.

Кроме того, Z80 имеет 16-разрядные регистры: счетчик команд (PC) и указатель стека (SP). Обычно ЭВМ имеет различные адресные пространства памяти и регистров МП, а иногда -отдельные адресные пространства регистров устройств ввода-вывода и внутренней памяти.

Кроме того, память хранит как данные, так и команды. Поэтому для ЭВМ разработано множество способов обращения к памяти, называемых режимами адресации. Режим адресации памяти - это процедура или схема преобразования адресной информация об операнде в его исполнительный адрес. Все способы адресации памяти можно разделить на:

-

прямой, когда исполнительный адрес берется непосредственно из команды или вычисляется с использованием значения, указанного в команде, и содержимого какого-либо регистра (прямая адресация, регистровая, базовая, индексная и т.д.);

-

косвенный, который предполагает, что в команде содержится значение косвенного адреса, т.е. адреса ячейки памяти, в которой находится окончательный исполнительный адрес (косвенная адресация). Z80 применялся в машинах Sinclair ZX, Sinclair Spectrum, Tandy TRS80.

В состав Z80 входят: устройство управления, регистр команд, программный счетчик, 24 регистра пользователя и арифметико-логическое устройство.

- Устройство управления. В Z80 управляющее устройство выдаёт огромное число внутренних управляющих сигналов, а также обеспечивает формирование внешних управляющих сигналов.

- Регистр команд. Термин "регистр" используется для описания простой ячейки памяти внутри Z80. Регистр содержит 8 бит (1 байт). В Z80 имеется большой блок регистров, и пересылка байтов данных к регистрам и от них является простейшей и наиболее важной чертой программирования в машинных кодах.

Рисунок 1 – Микропроцессор Z80 фирмы Zilog

- Программный счетчик

Программный счетчик - это пара регистров, которые используются совместно, поэтому программный счетчик содержит 16-ти битные значения.

Когда инструкции выбираются, управляющее устройство использует информацию в программном счетчике как адрес ячейки памяти, содержащей команду, которая должна выполняться следующей. После выполнения команды значение в программном счетчике увеличивается.

Действие программного счетчика очень похоже на переменную РРС интерпретатора Бэйсик, которая содержит номер текущей строки Бэйсик и также наращивается.

- Регистры пользователя. Микропроцессор Z80 содержит две идентичные группы (банка) из восьми 8-разрядных регистров в каждой. Эти регистры для краткости именуются регистрами общего назначения, что, однако, не совсем верно.

Каждый банк состоит из следующих регистров:

– аккумулятора A;

– регистра флагов F;

– регистров общего назначения B, C, D, E, H и L.

Регистры второго банка принято обозначать с помощью знака апострофа: A', B' и т.д. Функционально регистры обеих групп совершенно идентичны.

Подавляющее число инструкций микропроцессора оперирует с содержимым регистров первого (основного) банка. Имеются две инструкции (EX AF,AF' и EXX), которые позволяют обменять местами содержимое банков. Суммарное время выполнения этих двух команд составляет 8 тактов; время, необходимое для сохранения тех же самых регистров в стеке с помощью команд PUSH (как это традиционно делается в обработчиках прерывания для процессора 8080), составляет 44 такта; для восстановления содержимого регистров из стека командами POP требуется 40 тактов.

-

Аккумулятор A

Используется во всех основных арифметико-логических операций и содержит один из операндов, а также результат операции.

-

Регистры общего назначения

Используются вместе с аккумулятором в байтовых арифметико-логических операциях, храня второй операнд. Кроме того, имеются инструкции инкремента и декремента содержимого этих регистров. Регистр B, помимо всего прочего, используется в качестве счётчика в инструкции организации циклов DJNZ.

Регистры общего назначения могут логически объединяться в три пары BC, DE и HL, применяющиеся для хранения и обработки 16-разрядных адресов и операндов (старший байт находится соответственно в регистре B, D и H, а младший – в C, E и L). Особенно часто это свойство используется для регистровой пары HL, поскольку система команд включает полный набор арифметико-логических операций между содержимым аккумулятора и ячейкой памяти, адрес которой находится в этой регистровой паре (в системе команд микропроцессора 8080 для обозначения такого операнда использовался “псевдорегистр” M). Правда, арифметико-логические операции возможны и над операндами, адреса которых хранятся в индексных регистрах, но коды этих команд занимают 3 байта памяти вместо одного, а для их выполнения требуется 19 тактов вместо семи.

Адрес в регистровой паре BC может применяться в командах пересылки 8-разрядных операндов, а также в операциях ввода-вывода. Кроме того, содержимое регистровой пары BC используется в качестве счётчика в инструкциях обработки блоков данных. Адрес в регистровой паре DE используется в командах пересылки 8-разрядных операндов и обработки блоков данных.