Технические параметры системы

Тактовая частота процессора, МГц, 2

Объем, Кбайт

ОЗУ, 8

РПЗУ 4

Объем информации на кассете, Мбайт 9

Скорость движения МЛ, см/с 4,75

Плотность записи информации на МЛ, бит/мм 126

Надежность записи, бит 10-8

Динамический диапазон, дБ 96

Число разрядов АЦП, бит 12

Потребляемая мощность, Вт:

при заполнении буфера 6

при работе магнитофона 1,5

Время записи буфера, с 0,5

Число входных каналов, не более

Последовательная одновременная запись По 4 каналам

3 Обоснование выбора микропроцессора

Система для сбора, обработки и регистрации информации на кассетной МЛ выполнена на базе микропроцессорного комплекта (МПК) КР580, позволяющий создавать эффективные вычислительные устройства, ориентированные на реализацию вычислительных задач и устройств управления. Основу МПК составляет центральный процессорный элемент КР580ИК80А, являющийся функционально-законченным однокристальным параллельным 8-разрядным микропроцессором с фиксированной системой команд. В МП отсутствуют возможности аппаратного наращивания разрядности обрабатываемых данных.

Микропроцессорный комплект БИС серии КР580 предназначен для создания широкого класса средств вычислительной техники и обработки информации. На основе комплекта строятся микроЭВМ контрольно-измерительных систем, микроЭВМ для управления технологическими процессами, контроллеры периферийных устройств, бытовых приборов и игровых автоматов.

Выбор между различными микропроцессорами должен выполняться на основе анализа особенностей их применения, требования точности, разрядности и т.д.

Аналогом процессора КР580ИК80А является 8-разрядный параллельный однокристальный микропроцессор типа 8080 фирмы Intel, серийно выпускаемый с 1974 г. Сравнительный анализ данных микропроцессоров приведен в таблице 3.

При сравнении МП КР580ИК80А и 8080 видно, что они обладаю почти одинаковыми характеристиками. Так же известно, что выбранный МП КР580ИК80А обладает меньшим быстродействием и отсутствием возможности наращивания разрядности.

Однако, несмотря на недостатки, МП КР580ИК80А отличается простотой архитектуры и дешевизной, что является важным условием при построении простых устройств, которые не требуют высокой точности и высокого быстродействия, а значит, нет необходимости в дополнительной сложности и затратах.

Таблица 1 – Характеристики МП КР580ИК80А и 8080

|

Микропроцессор |

КР580ИК80А |

8080 |

|

Разрядность слова данных/команд, бит |

8 |

8 |

|

Технология изготовления |

n-МОП |

n-МОП |

|

Емкость непосредственно адресуемого ЗУ, байт |

64К |

64К |

|

Число основных команд |

246 |

78 |

|

Максимальная тактовая частота, МГц |

2,5 |

4,77 |

|

Время выполнения команды наим./наиб., мкс |

1/3,2 |

1,5/3,75 |

|

Число уровней прерываний |

2 |

1 |

|

Число регистров общего назначения |

6 |

8 |

|

Число выводов корпуса |

40 |

40 |

|

Напряжение питания, В |

5,12 |

5,12 |

Таким образом, в дефектоскопе «Сирена-1» предпочтительнее использование МП КР580ИК80А, который благодаря своей архитектуре и фиксированному набору команд является наиболее подходящим для применения в подобных устройствах

ОПИСАНИЕ МИКРОПРОЦЕССОРА КР580ИК80А

4.1 Структура микропроцессора КР580ИК80А

Микропроцессор К580 представляет собой изготовленную по n-МОП технологии БИС, содержащую около 5 тыс. транзисторов. БИС микропроцессора реализована на кремниевом кристалле размером около 30 мм2, заключенном в корпус с 40 выводами. Длина слова микропроцессора — 8 разрядов. Тактовая частота МП — 2 МГц. Уровни напряжения питания +5, —5, + 12 В.

Микропроцессор К580 предназначен для работы с памятью (постоянной и оперативной) с общей емкостью до 64 Кбайт. Память имеет байтовую структуру — возможна адресация в памяти любого байта. Ширина выборки из памяти — 1 байт. При обращении к памяти используются 16-разрядные (двухбайтные). адреса.

При создании малоразрядных микропроцессоров (в МП К580 слово имеет всего 8 разрядов) возникают трудности с выбором структуры и формата команд. Достижение высокого быстродействия МП облегчается, если формат команды совпадает с длиной слова МП. Однако в коротком 8-разрядном слове невозможно разместить всю командную информацию, необходимую для реализации достаточно гибкой системы команд (МП К580 выполняет 70 различных команд, не считая их модификаций), при довольно большом размере адресного пространства памяти (в МП К580 — 64 К адресов). С другой стороны, использование многословных (многобайтных) форматов команд связано со снижением быстродействия МП. В более общем плане следует отметить, что имеются трудности при ограниченных аппаратурных ресурсах МП для создания прибора, обладающего широкими вычислительными и логическими возможностями.

Указанные затруднения преодолеваются с помощью эффективных технологических, структурных и схемотехнических решений, а также специальных приемов кодирования команд и адресации операндов.

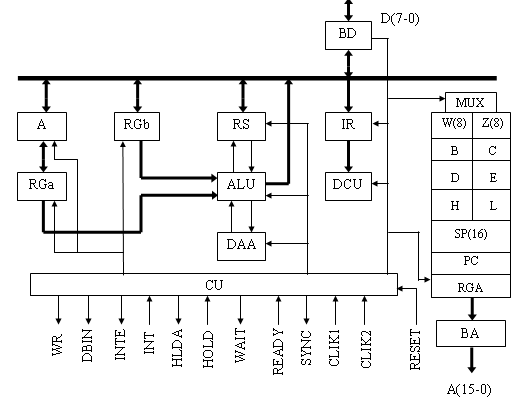

Структурная схема микропроцессора приведена на рисунке 2.

Рисунок 2 – Структурная схема микропроцессора КР580ИК80А

Организация МП К580 отмечена следующими основными особенностями:

трехшинной структурой с шинами данных, адреса и управления;

магистральным принципом связей, реализованным в виде связывающей основные узлы МП двунаправленной шины данных, имеющей ширину (8 разрядов), равную длине слов, обрабатываемых микропроцессором;

наличием регистровой памяти, образованной программно-доступными общими и специализированными регистрами (счетчик команд, указатель стека, указатель данных), а также регистрами временного хранения;

наличием средств организации стековой памяти (регистр — указатель стека, схемы выполнения операций инкрементации — декрементации, специальных команд стековых операций);

наличием 16-разрядной шины адреса, обеспечивающей возможность прямой адресации любого байта в памяти емкостью 64 Кбайт;

наличием операций над двухбайтными словами (16-разрядными числами, адресами), что обеспечивается специальными командами, тандемными (двух- или трехбайтными) передачами;

использованием трех форматов команд (однобайтного, двухбайтного и трехбайтного) и разнообразных способов адресации (подразумеваемой, прямой, регистровой, косвенной, непосредственной, стековой), позволивших при коротком 8-разрядном слове иметь достаточно гибкую систему команд;

возможностью реализации векторного многоуровневого приоритетного прерывания путем подключения к МП специальной дополнительной БИС (контроллера прерываний);

возможностью реализации в МП режима прямого доступа к памяти путем подключения специальной дополнительной БИС (контроллера прямого доступа);

наличием эффективных средств работы с подпрограммами и обработки запросов прерываний (стековая память, специальные команды вызова подпрограмм и возврата из подпрограмм, в том числе условного).

Отмеченные особенности организация микропроцессора разъясняются при дальнейшем изложении.

МП имеет три шины: 8-разрядную двунаправленную внутреннюю шину данных (ШД), 16-разрядную адресную шину (ША) и шину управления (ШУ).

Внутренняя шина данных является магистралью, по которой могут обмениваться данными все подключенные к ней блоки (узлы) МП. Одновременно по шине данных осуществляется обмен только между двумя узлами МП. Таким образом, узлы МП, подсоединенные к шине данных, разделяют эту шину во времени.

Шина управления содержит линии для передачи управляющих сигналов, признаков состояния процессора и периферийных устройств, в том числе линии: синхронизации передачи и идентификации информации, передаваемой по шине данных; сигналов, информирующих МП о готовности, периферийных устройств; сигнала запроса прерывания от периферийных устройств и сигнала разрешения прерывания и др.

При рассмотрении структуры МП можно выделить следующие ее части: блок регистров, арифметическо-логическое устройство (АЛУ), буферные схемы, управляющее устройство.

4.1.1. Блок регистров

Микропроцессор К580 содержит программно-доступные 8-разрядные регистры: регистр-аккумулятор; общие регистры (регистры общего назначения РОН) В, С, D, Е; регистр признаков F и 16-разрядные специализированные регистры: счетчик команд СК; регистр-указатель стека УС; сдвоенный регистр косвенного адреса HL (Н — регистр старшего полуадреса, L — регистр младшего полуадреса). Кроме того, имеются непосредственно недоступные программе регистры; 8-разрядные регистры временного хранения T,W, Z; 8-разрядний регистр команды; 16-разрядный регистр адреса РА. Имеется возможность использования содержимого пар регистров В и С, D и Е, Н и L как составных слов двойной длины.

Общие регистры используются для хранения операндов, промежуточных и конечных результатов, а также "адресов и индексов при косвенной и индексной адресациях.

Блок регистров имеет в своем составе особый регистр-аккумулятор. Аккумулятор используется в качестве источника одного из операндов и места, где фиксируется результат операции. В команде аккумулятор в явном виде не адресуется. На использование аккумулятора в операции указывает код операции команды. Иначе говоря, в отношении аккумулятора применяется подразумеваемая адресация, что позволяет применять одноадресные команды, имеющие сравнительно короткий формат.

Для того, чтобы аккумулятор мог одновременно являться регистром операнда и регистром результата операции, он строится на основе двухступенчатых триггеров. (Следует отметить, что некоторые МП для повышения производительности имеют несколько аккумуляторов.)

По отношению к другим программно-доступным регистрам применяется или подразумеваемая, или укороченная (регистровая) адресация, задаваемая коротким номером регистра .

Использование аккумулятора и общих регистров позволяет при выполнении команд уменьшить количество обращений к памяти и тем самым повысить быстродействие МП.

Наличие в блоке регистров специализированного регистра косвенного адреса HL позволяет иметь команды с Подразумеваемой косвенной адресацией, т.е. без указания в команде номера регистра, хранящего исполнительный адрес .

Особенностью блока регистров МП является наличие в его составе схемы инкрементора / декрементора, которая производит над содержимым регистров (без привлечения АЛУ) операцию прибавления / вычитания 1. Схема инкрементора / декрементора позволяет реализовать процедуры автоматического задания приращений при операциях с адресами не только в регистре-указателе стека, но и в счетчике команд.

При выполнении операций в МП возникает потребность в кратковременном хранении некоторых операндов и результатов выполнения операций. Для этой цели служат регистры временного хранения данных Т, W и Z. Использование регистров временного хранения позволяет МП за один цикл выполнения команды реализовать, например, такую операцию, как обмен содержимым двух регистров.

Буферные регистры временного хранения данных построены по простейшему принципу динамического хранения переменных на емкостях затворов МОП-транзисторов. Они позволяют простейшими аппаратными средствами выполнять довольно сложные операции «перетасовки» данных не только между общими регистрами, но и между регистрами, аккумулятором и памятью.

Для повышения эффективности операций со словами двойной длины и операций формирования и пересылок двухбайтных адресов имеется возможность оперировать с содержимым пар регистров В и С, D и Е, Н и L как с составными словами двойной длины, т. е. в МП автоматически выполняется операция конкатенации над содержимым пары регистров. При этом реализуются так называемые тандемные пересылки, состоящие в передаче в цикле выполнения команды последовательно друг за другом 2 байт информации.

В состав блока регистров входит регистр-защелка адреса памяти РА. Собственно регистр адреса недоступен программисту. Однако любая пара регистров (ВС, DE, HL) может быть использована для задания адресов команд и данных в программе. Этот адрес под воздействием соответствующих команд не только может быть загружен в регистр-защелку адреса, но и модифицирован (посредством схемы инкрементор / декрементор) в процессе загрузки. Регистр-защелка адреса передает адрес в буферную схему и далее в шину адреса.

4.1.2. Арифметическо-логическое устройство

Восьмиразрядная комбинированная схема АЛУ выполняет арифметические и логические операции над 8-разрядными числами в процессе межрегистровых пересылок. К одному из входов схемы АЛУ всегда подключен аккумулятор, к другому через регистр Т может быть подключен любой из общих регистров.

Арифметическо-логическое устройство имеет собственный регистр временного хранения Т. Он позволяет избежать возникновения «гонок», когда какой-либо из общих регистров используется в одной операции и в качестве регистра-операнда, и в качестве регистра-результата.

Арифметическо-логическое устройство непосредственно связано с регистром признаков, в соответствующих разрядах которого фиксируются особенности выполнения каждой операции: нулевой результат в аккумуляторе — Z, перенос из старшего разряда — CY, знак результата — S, паритет — Р и вспомогательный перенос из младшего полубайта — АС. Наличие в МП регистра признаков упрощает осуществление программных переходов в зависимости от состояния одного или более триггеров признаков. Арифметическо-логическое устройство позволяете процессе межрегистровых «пересылок с перекосом» выполнять операции сдвига на один разряд вправо или влево. Многократный сдвиг реализуется последовательностью одноразрядных сдвигов, т.е. последовательно расположенными в программе командами сдвига.

В состав АЛУ входит комбинационная схема десятичного корректора ДК, назначение которого состоит в том, чтобы под воздействием специальной команды интерпретировать результат выполнения двоичной операции как результат операции десятичной арифметики. Для этого к старшей тетраде в схеме ДК прибавляется число 6, кроме тех случаев когда либо не возникал перенос ни из одной тетрады и содержимое старшей и младшей тетрад находится в пределах 0—9 и 0—9 (или 0—8 и А—F) соответственно, либо не было переноса из старшей тетрады, содержащей число 0—9 и был перенос из младшей. К младшей тетраде одновременно также прибавляется число 6, кроме случая отсутствия переноса из младшей тетрады, содержащей число 0—9. Межтетрадные связи при этом не разрываются.

Арифметическо-логическое устройство реализует простейшие арифметические и логические операции (сложение, вычитание, сдвиги, сравнение, логическое умножение и т. п.). Все более сложные операции (умножение, деление, вычисление элементарных функций и др.) выполняются по подпрограммам.

4.1.3. Стековая память

В МП К580 организуется стековая память, реализующая безадресное задание операндов. В общем случае стек представляет собой группу последовательно пронумерованных регистров или ячеек памяти, снабженных указателем стека, в котором автоматически при записи и считывании устанавливается номер (адрес) последней занятой ячейки стека (вершины стека). При операции занесения в стек слово помещается в следующую по порядку свободную ячейку стека, а при считывании из стека — извлекается последнее поступившее в него слово. Таким образом в стеке реализуется дисциплина обслуживания «последний пришел — первый ушел». Эта дисциплина при обращении к стеку реализуется автоматически. Поэтому при операциях со стеком возможно безадресное задание операнда—команда не содержит адреса ячейки стека, но содержит адрес (или он подразумевается) ячейки памяти или регистра, откуда слово передается в стек или куда загружается из стека.

В рассматриваемом МП используется «перевернутый» стек, т. е. при передаче в стек слова значение УС (адрес вершины стека) уменьшается, а при извлечении слова из стека — увеличивается.

Непосредственно в МП К580 из оборудования стековой памяти содержится только регистр-указатель стека и соответствующие цепи управления. Сам стек реализуется в виде группы последовательных ячеек оперативной памяти.

Стековая адресация широко используется при работе с подпрограммами и в процедурах прерывания.

4.1.4. Буферные схемы

Двунаправленный буфер шины данных предназначен для логического и электрического разделения внутрипроцессорной шины данных и внешней, системной шины ШД. Буфер состоит из регистра-защелки и выходной схемы с тремя состояниями, т.е. схемы, обеспечивающей на выходе состояния 0, 1 и полное электрическое отключение от нагрузки (высокоимпедансное состояние). Схемы подобных буферов будут рассмотрены далее. Здесь отметим только, что наличие в МП буферных схем, отключающихся от общей системной шины, обеспечивает реализацию магистрального принципа межмодульных связей в МП-системе.

В режиме ввода информации внутренняя шина данных подсоединяется к регистру-защелке буфера, загрузку которого из внешней шины производит буферная схема под управлением команды.

В режиме вывода информации буферная схема передает в шину данных содержимое буферного регистра-защелки, на вход которого по внутренней шине с одного из регистров (чаще всего из аккумулятора) загружен код, подлежащий выдаче.

Во время выполнения операций в МП, не связанных с процедурами обмена с внешними по отношению к МП устройствами системы, буферная схема отключается от шины ШД, т, е. переходит в высокоимпедансное состояние «не нуль, не один», которое принято называть «плавающим» состоянием.

Буферная схема шины адреса БА — однонаправленная, обеспечивает передачу адресов команд и данных, а также номеров периферийных устройств от МП в систему. Выход буфера адреса, точно так же как и буфера данных, может переходить в отключенное состояние. Подобный режим необходимо иметь в МП-системе, в которой к памяти могут обращаться по системной шине адреса не только МП, но и некоторые из периферийных устройств (например, пульт оператора, контроллер прямого доступа к памяти и др.).

Прежде чем перейти к рассмотрению способа реализации программного управления в МП, целесообразно ознакомиться с системой команд микропроцессора.

4.2 Основные временные параметры микропроцессора КР580ИК80А

Время выполнения команды микропроцессора зависит от типа команды и составляет от одного до пяти машинных циклов (М). Длительность машинного цикла может составлять от трех до пяти машинных тактов (Ti). Длительность машинного такта равна периоду тактовой частоты, задаваемой частотой фаз СLK1, СLK2 генератора тактов.

Операции, выполняемые микропроцессором в машинном цикле, определяются 8-разрядной информацией, характеризующей состояние внутренних узлов микропроцессора. Этот байт состояния называется также словом состояния процессора и выдается на шину данных микропроцессора в такте Т2 каждого машинного цикла.

Для

фиксации слова-состояния процессора

можно использовать внешний 8-разрядный

регистр. На рисунке 5 приведена временная

диаграмма и схема записи слова состояния

в многорежимный буферный регистр

К589ИР12. Запись осуществляется сигналом

CLK1 в такте Т2 с использованием сигнала

SYNC.

Рисунок 3 – Временная диаграмма и схема записи слова состояния в многорежимный буферный регистр К589ИР12

Наименование и назначение сигналов состояния, а также соответствующие им разряды шины данных микропроцессора указаны в таблице 5.

Таблица 2 – Сигналы состояния микропроцессора

|

Обозначение сигнала |

Разряд шины данных |

Назначение сигнала |

|

INTA

WO

STACK

HLTA

OUT

M1

INT

MEMR |

D0

D1

D2

D3

D4

D5

D6

D7 |

Подтверждение прерывания; используется для стробирования приема команды RST в МП из схемы прерывания Запись; L – уровень сигнала указывает на запись данных в ЗУ или ВУ; H – уровень сигнала – запись в микропроцессор Стек; Н – уровень сигнала указывает, что на шине адреса установлено содержимое SP Подтверждение останова; Н – уровень сигнала указывает на переход МП в состояние останова Ввод; Н – уровень сигнала указывает, что на шине адреса установлен код ВУ и можно осуществить ввод данных в МП по сигналу DBIN=1 Н – уровень сигнала указывает, что МП принимает первый байт команды Ввод; Н –уровень сигнала указывает, что на шине адреса установлен код ВУ и можно осуществить ввод данных в МП по сигналу DBIN=1 Чтение; Н – уровень сигнала указывает, что осуществляется чтение содержимого ЗУ по адресу, установленному на шине адреса |

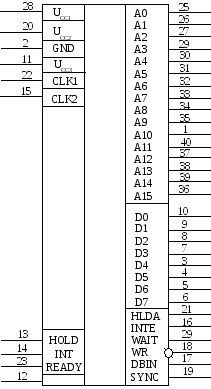

4.3 Цоколевка микросхемы КР580ИК80А

Цоколевка микросхемы КР580ИК80А представлена на рисунке 4.

R

Рисунок 4 - цоколевка микросхемы КР580ИК80А

Назначение выводов :

А(15 - 0) – трехстабильная 16-разрядная шина адреса;

D(7 – 0) – двунаправленная трехстабильная 8-разрядная шина данных;

WR – выход сигнала «выдача» - напряжение L-уровня указывает на выдачу байта информации на шину D(7 – 0)для записи в ЗУ или УВВ;

DBIN – выход сигнала «прием» - напряжение Н-уровня указывает на прием с шины D(7 – 0) байта информации, выданного ЗУ или УВВ;

INTE – выход сигнала «разрешение прерывания»;

INT – вход сигнала «запрос на прерывание»;

HLDA – выход сигнала «подтверждение захвата» - напряжение Н-уровня указывает на перевод шин адреса и данных МП в высокоимпедансное состояние;

HOLD – вход сигнала «захват» - напряжение Н-уровня указывает на запрос другими устройствами системы на управление шинами системы;

WAIT – выход сигнала «ожидание» - напряжение Н-уровня указывает на

состояние ожидания МП;

READY – вход сигнала «готовность» - напряжение Н-уровня указывает на готовность данных на шине D(7 – 0) к вводу в МП или на готовность внешних устройств к приему информации, служит для синхронизации микропроцессоров с ЗУ или УВВ;

SYNC – выход сигнала «синхро» - напряжение Н-уровня идентифицирует начало каждого машинного цикла;

CLK1, CLK2 – тактовые сигналы, определяют тактовую частоту работы МП БИС;

R – вход установки 0 – установка счетчика команд в нуль, сброс триггеров разрешения прерывания и захвата шин;

UCC1 – напряжение питания (+5 В);

UСC2 – напряжение питания (+12 В);

UСС3 – напряжение питания (-5 В);

GND – общий вход (напряжение питания 0 В).