- •Содержание:

- •Состав микропроцессорного комплекта бис серии к1810………..…4

- •Сегментация памяти и вычисление адресов в мп к1810вм86…………………………………………………………….4

- •11. Микроконтроллеры…………………………………………………..47

- •Состав микропроцессорного комплекта бис серии к1810

- •1. Сегментация памяти и вычисление адресов в микропроцессоре к1810вм86

- •2. Микропроцессор к1810вм86 или intel 8086

- •2.1. Особенности защищенного режима мп Intel 8086

- •2.2. Структура мп Intel 8086

- •2.3. Система прерываний в мп Intel 8086

- •2.4. Примеры конфигураций мпс на базе центрального процессора (вм86) и сопроцессора ввода/вывода (вм89)

- •2.5. Адресация к памяти цп

- •2.7. Функциональная схема подключения центрального процессора и сопроцессора

- •2.8. Принцип построения мп на базе к1810вм86, включенного в максимальном режиме

- •2.9. Адресное пространство мп

- •2.10. Особенности мп к1810вм88 или Intel 8088

- •3. Микроконтроллеры

- •Восьмиразрядные мк

- •3.1. Микроконтроллер кр1816ве51 или Intel 8051ан

- •11.2. Характеристика основных компонентов мк51

- •Блок регистров специальных функций

- •Формат слова состояния программы (ссп)

- •Альтернативные функции порта 3

- •3.3. Последовательный интерфейс

- •3.4. Таймер/счетчик

- •Регистр режима работы таймера/счетчика

- •Регистр управления/статуса таймера

- •3.5. Система прерываний мк51

- •Регистр масок прерывания (рмп)

- •Регистр приоритетов прерываний

- •3.6. Совмещение адресного пространства мк51

- •3.7. Особенности поведения мк при подаче сигнала сброса

- •3.8. Доступ к внешней памяти

- •3.9. Программирование мк

- •3.10. Запись бита защиты

- •3.11. Режим пониженного энергопотребления

- •3.12. Согласование последовательного порта мк с интерфейсом rs-232с

- •3.13. Система команд в мк51

- •Группа команд передачи данных

- •3.14. Схема подключения мк к клавиатуре и дисплею с использованием контроллера клавиатуры и дисплея

- •3.15. Расширители, подключаемые к микроконтроллеру

- •Основная литература

- •Дополнительная литература

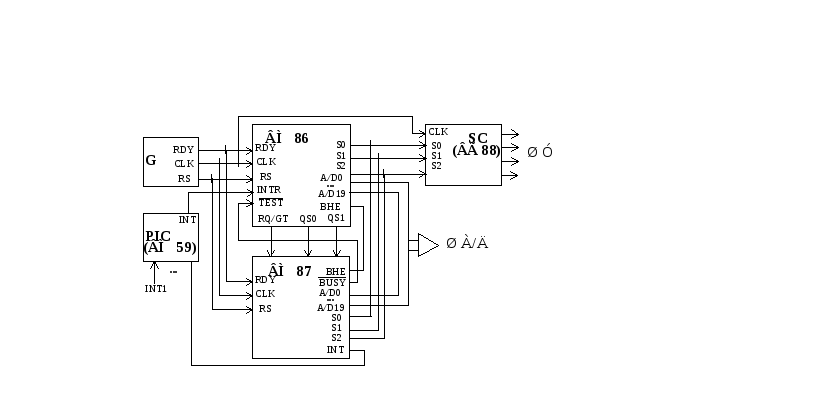

2.7. Функциональная схема подключения центрального процессора и сопроцессора

Функциональная схема подключения центрального процессора и сопроцессора представлена на рисунке 35.

Рис. 35

Находясь в состоянии ожидания, центральный процессор реагирует на запросы на прерывания и может их обслуживать. Для совместного использования ША/Д процессоры снабжены специальными аппаратными средствами, которые формируют сигналы доступа и ответа в системной шине.

RQ/GT – сигнал запроса на предоставление шины. Если ЦП захватил шину, то он указывает это соответствующим сигналом по линии запроса. Если сопроцессор работает с системной шиной, то он формирует сигнал занятости, который поступает на ТЕSТ.

После освобождения шины сопроцессором сигнал BUSY сбрасывается.

Сигналы цикла шины S0, S1, S2 характеризуют вид выполняемого цикла шины для системного контроллера. По анализу этой информации он формирует необходимые сигналы управления.

Для обработки исключительных ситуаций (потеря точности при округлении) сопроцессор формирует сигнал запроса, который поступает на контроллер прерываний.

Сигнал запроса, инициируемый сопроцессором, часто предполагает вмешательство ЦП. Далее осуществляется стандартное выполнение прерывающей подпрограммы, которая удаляет внештатную ситуацию.

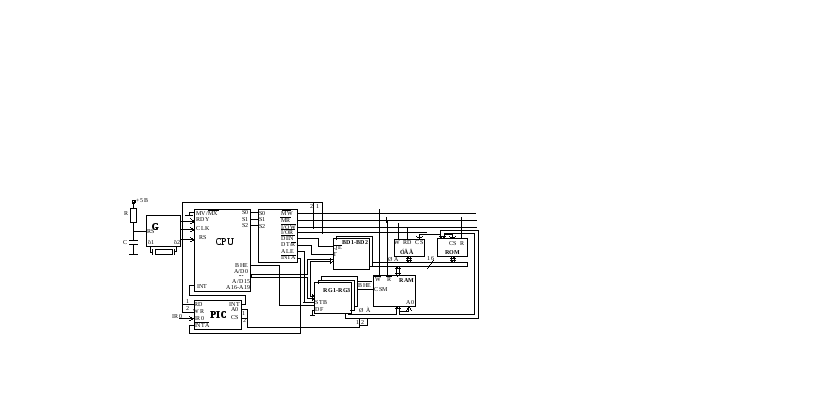

2.8. Принцип построения мп на базе к1810вм86, включенного в максимальном режиме

Схема построения МП на базе К1810ВМ86, включенного в максимальном режиме представлена на рисунке 36.

В максимальном режиме МП не вырабатывает самостоятельно часть сигналов управления, возлагая эти функции на системный контроллер, который по анализу сигналов состояния S0 – S2 формирует соответствующие сигналы для определения цикла шины.

Рис. 36

В данной схеме для ША используются три буферных регистра. Для передачи данных – два шинных формирователя, на выходе которых реализована СШД (16-разрядная).

В указанной системе имеется контроллер прерываний, который формирует сигнал запроса INT, поступающий на маскируемый вход МП.

Табл.7 Соответствие вида прерываний и числа тактов

|

Тип прерывания |

Число тактов |

|

INT3, INT0, INTn |

52 |

|

Пошаговый режим |

51 |

|

NMI (немаскируемые прерывания) |

50 |

|

INT (INTR) |

61 |

2.9. Адресное пространство мп

Память представляется массивами с 20-разрядным адресом. Диапазон равен 00000 – FFFFF.

Полная информация для определения физического адреса находится в двухбайтном пространстве, т.е. адрес объекта – сегмент смещения. Максимальный объем сегмента 64 кбайт.

2.10. Особенности мп к1810вм88 или Intel 8088

Данный МП имеет 8-разрядную шину данных и позволяет перевести аппаратные средства серии 580 на программную среду серии 1810 для повышения производительности.

Микропроцессоры ВМ86 и ВМ88 имеют одинаковую архитектуру и систему команд, одинаковую нумерацию выводов, но линия А8-А15 используется только для выдачи адреса у МП ВМ88. Линия ВНЕ заменена на SSО (линия состояния).

Длина очереди команд – 4 байта для ВМ88 и 6 байт для ВМ86.

Наиболее простая система строится на базе ВМ88, когда применяется программируемый параллельный интерфейс (86), ПЗУ и ОЗУ (80).