- •Содержание:

- •Состав микропроцессорного комплекта бис серии к1810………..…4

- •Сегментация памяти и вычисление адресов в мп к1810вм86…………………………………………………………….4

- •11. Микроконтроллеры…………………………………………………..47

- •Состав микропроцессорного комплекта бис серии к1810

- •1. Сегментация памяти и вычисление адресов в микропроцессоре к1810вм86

- •2. Микропроцессор к1810вм86 или intel 8086

- •2.1. Особенности защищенного режима мп Intel 8086

- •2.2. Структура мп Intel 8086

- •2.3. Система прерываний в мп Intel 8086

- •2.4. Примеры конфигураций мпс на базе центрального процессора (вм86) и сопроцессора ввода/вывода (вм89)

- •2.5. Адресация к памяти цп

- •2.7. Функциональная схема подключения центрального процессора и сопроцессора

- •2.8. Принцип построения мп на базе к1810вм86, включенного в максимальном режиме

- •2.9. Адресное пространство мп

- •2.10. Особенности мп к1810вм88 или Intel 8088

- •3. Микроконтроллеры

- •Восьмиразрядные мк

- •3.1. Микроконтроллер кр1816ве51 или Intel 8051ан

- •11.2. Характеристика основных компонентов мк51

- •Блок регистров специальных функций

- •Формат слова состояния программы (ссп)

- •Альтернативные функции порта 3

- •3.3. Последовательный интерфейс

- •3.4. Таймер/счетчик

- •Регистр режима работы таймера/счетчика

- •Регистр управления/статуса таймера

- •3.5. Система прерываний мк51

- •Регистр масок прерывания (рмп)

- •Регистр приоритетов прерываний

- •3.6. Совмещение адресного пространства мк51

- •3.7. Особенности поведения мк при подаче сигнала сброса

- •3.8. Доступ к внешней памяти

- •3.9. Программирование мк

- •3.10. Запись бита защиты

- •3.11. Режим пониженного энергопотребления

- •3.12. Согласование последовательного порта мк с интерфейсом rs-232с

- •3.13. Система команд в мк51

- •Группа команд передачи данных

- •3.14. Схема подключения мк к клавиатуре и дисплею с использованием контроллера клавиатуры и дисплея

- •3.15. Расширители, подключаемые к микроконтроллеру

- •Основная литература

- •Дополнительная литература

2.4. Примеры конфигураций мпс на базе центрального процессора (вм86) и сопроцессора ввода/вывода (вм89)

Сопроцессор и процессор могут разделять общую шину и обращаться к памяти и устройствам ввода/вывода по этой шине. Возможно также раздельное использование шин с целью увеличения быстродействия.

Рис. 31

Рис. 31

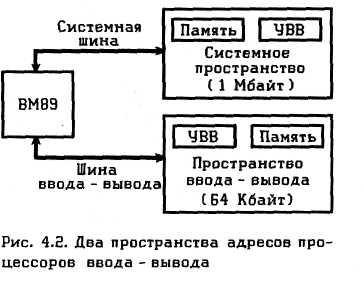

МП может обращаться в системное пространство адресов емкостью 1 Мбайт, либо в пространство ввода/вывода емкостью 64 кбайта. Реально МП располагает только одной физической шиной данных, но удобно считать, что в системное пространство он обращается по системной шине данных, а в пространство ввода/вывода – по шине ввода/вывода.

Отличие между шинами в формируемых управляющих сигналах.

Часть устройств ввода/вывода могут иметь адреса, размещенные в системном пространстве, поэтому говорят, что эти устройства ввода/вывода отображены на память, т.е. данные устройства ввода/вывода реагируют на 20-битные адреса, закрепленные за ними, и управляются сигналами МRD, MWR.

Аналогично, часть памяти может быть размещена в пространстве ввода/вывода, т.е. память оказывается отображенной на пространство ввода/вывода, т.е. данные ячейки могут реагировать на 16-битные адреса и команды для устройства ввода/вывода.

Указанные шины функционируют по-разному, в зависимости от конфигурации системы, где есть и сопроцессоры.

Различают две конфигурации:

-

местная;

-

удаленная.

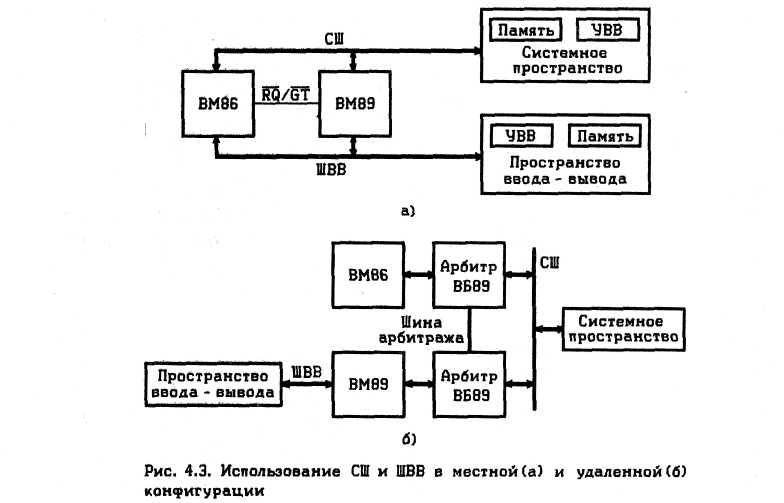

В местной конфигурации сопроцессор и центральный процессор совместно

Рис. 32

В местной конфигурации ЦП и СП совместно используют шины.

Арбитраж осуществляется по линии запроса, причем наиболее приоритетным является центральный процессор.

Если подключены два сопроцессора, то при одновременном запросе ВМ87 и ВМ89 предпочтение отдается ВМ89, но если в момент запроса шина используется ВМ87, то запрос не будет подтверждаться до окончания счета ВМ87.

Недостаток конфигурации – ограничение возможности параллельной работы ЦП и сопроцессора. Параллельная обработка возможна лишь тогда, когда ЦП не использует шину, выполняя команды из очереди.

При удаленной конфигурации общей является системная шина (СШ), но обращение к ней происходит под управлением арбитра шин. Шина ввода/вывода (ШВВ) является локальной. Ей безраздельно пользуется сопроцессор. Эта шина физически отделена от системной шины, поэтому в данной конфигурации сопроцессор может обращаться к устройствам ввода/вывода и памяти по локальной шине, не отвлекая от работы центральный процессор.

Наибольшая производительность системы достигается при размещении программ канала в локальной памяти, подключенной к локальной шине. Поэтому при извлечении команд программ канала сопроцессор не отвлекает от работы центральный процессор.

2.5. Адресация к памяти цп

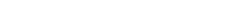

Структурно память микропроцессора делится на два блока: с четными и нечетными адресами, как это показано на рисунке 33.

Рис. 33

Табл. 6 Варианты пересылок по шине данных

|

ВНЕ |

А0 |

|

|

0 |

0 |

пересылается слово |

|

1 |

0 |

пересылается только младший байт |

|

0 |

1 |

пересылается только старший байт |

|

1 |

1 |

устройство не выбрано |

При обмене двухбайтной информацией адресом этой величины служит адрес младшего байта, т.е. если младший байт размещен в блоке с четными адресами и при поступлении на блок четного адреса А0=0 и одновременно ВНЕ – выбираются оба блока. Таким образом, передача двухбайтной величины производится за одно обращение к памяти.

2.6. КЭШ – память и ее особенности

КЭШ – память – быстродействующая память небольшой емкости между

центральным устройством и оперативной памятью, что показано на рисунке 34.

Рис. 34

Особенностью этой памяти является ее прозрачность адресуемой области памяти для программ КЭШ – память не добавляют. КЭШ – память – дополнительное хранилище копий информации из оперативной памяти. Вероятность обращения к данной информации велика и тогда КЭШ позволяет увеличить быстродействие системы. Таким образом, МП формирует адресный сигнал для КЭШ, с помощью которого можно выбрать необходимую информацию и осуществить считывание записи.

«hit» наличие адреса – совпадение КЭШа.

«miss» отсутствие адреса – промах КЭШа.

При «miss» работа программы останавливается и происходит обмен между оперативной памятью и КЭШ.

КЭП – коэффициент эффективного поиска. Он характеризует эффективность КЭШа.

Кэп = Nп / N,

где N – общее количество обращений к КЭШу.

КЭП>95% считается критерием эффективности КЭШа.

Объем КЭШа равен нескольким процентам от оперативной памяти.

В зависимости от способа обращения различают архитектуру:

1) Look aside – обращение к основной памяти начинается одновременно с обращением к КЭШу.

2) Look through – обращение к КЭШу, если промах, то идет обращение к оперативной памяти.

Уровни КЭШа:

-

внутренний КЭШ – 8÷32 кбайт;

-

внешний КЭШ – до 1 Мбайт.