- •Содержание:

- •Состав микропроцессорного комплекта бис серии к1810………..…4

- •Сегментация памяти и вычисление адресов в мп к1810вм86…………………………………………………………….4

- •11. Микроконтроллеры…………………………………………………..47

- •Состав микропроцессорного комплекта бис серии к1810

- •1. Сегментация памяти и вычисление адресов в микропроцессоре к1810вм86

- •2. Микропроцессор к1810вм86 или intel 8086

- •2.1. Особенности защищенного режима мп Intel 8086

- •2.2. Структура мп Intel 8086

- •2.3. Система прерываний в мп Intel 8086

- •2.4. Примеры конфигураций мпс на базе центрального процессора (вм86) и сопроцессора ввода/вывода (вм89)

- •2.5. Адресация к памяти цп

- •2.7. Функциональная схема подключения центрального процессора и сопроцессора

- •2.8. Принцип построения мп на базе к1810вм86, включенного в максимальном режиме

- •2.9. Адресное пространство мп

- •2.10. Особенности мп к1810вм88 или Intel 8088

- •3. Микроконтроллеры

- •Восьмиразрядные мк

- •3.1. Микроконтроллер кр1816ве51 или Intel 8051ан

- •11.2. Характеристика основных компонентов мк51

- •Блок регистров специальных функций

- •Формат слова состояния программы (ссп)

- •Альтернативные функции порта 3

- •3.3. Последовательный интерфейс

- •3.4. Таймер/счетчик

- •Регистр режима работы таймера/счетчика

- •Регистр управления/статуса таймера

- •3.5. Система прерываний мк51

- •Регистр масок прерывания (рмп)

- •Регистр приоритетов прерываний

- •3.6. Совмещение адресного пространства мк51

- •3.7. Особенности поведения мк при подаче сигнала сброса

- •3.8. Доступ к внешней памяти

- •3.9. Программирование мк

- •3.10. Запись бита защиты

- •3.11. Режим пониженного энергопотребления

- •3.12. Согласование последовательного порта мк с интерфейсом rs-232с

- •3.13. Система команд в мк51

- •Группа команд передачи данных

- •3.14. Схема подключения мк к клавиатуре и дисплею с использованием контроллера клавиатуры и дисплея

- •3.15. Расширители, подключаемые к микроконтроллеру

- •Основная литература

- •Дополнительная литература

2.2. Структура мп Intel 8086

Микропроцессор состоит из трех частей:

-

операционное устройство;

-

устройство сопряжения с шиной;

-

устройство управления.

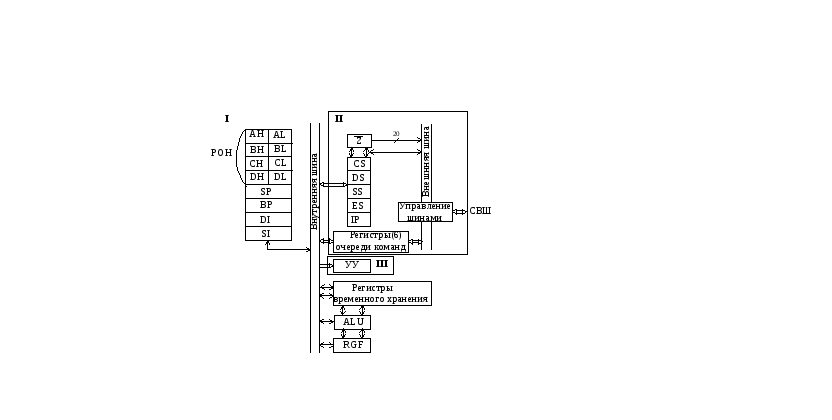

Структура МП Intel 8086 представлена на рисунке 28.

Рис. 28

На рисунке 28 I обозначено операционное устройство, которое предполагает набор регистров:

SР – указатель стека;

ВР – регистр указателя базы стека;

DI, SI – индексные регистры приемника/источника соответственно;

RGi – регистры временного хранения;

RGF – регистр флагов;

РОН – регистры общего назначения предназначены для временного хранения;

SР, ВР, DI, SI – для хранения адресной информации и выполнения специальных функций;

АН, АL – выполняют функцию аккумулятора;

ВН, ВL – регистр указателя базы данных;

СН, СL – счетчик циклов;

DН, DL – хранение данных.

Устройство сопряжения с шиной обозначено II, а устройство управления – III.

Структура регистра признаков

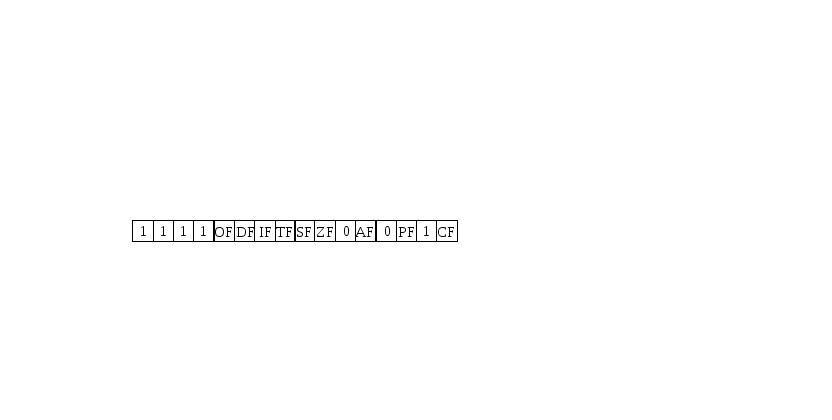

Структура регистра признаков представлена на рисунке 29.

Рис. 29

Из 16 бит задействованы 9. Регистр признаков определяет состояние МП.

Нулевой бит – СF – флаг переноса;

Первый бит – 1 – фиксированный, не используется;

Второй бит – РF – флаг паритета (четности);

Третий бит – 0 – фиксированный, не используется;

Четвертый бит – АF – дополнительный перенос;

Пятый бит – 0 – фиксированный, не используется;

Шестой бит – ZF – флаг нуля;

Седьмой бит – SF – флаг знака;

Восьмой бит – ТF – флаг трассировки (флаг пошагового режима). При установке этого флага МП переходит в пошаговый режим (для отладки программы);

Девятый бит – IF – флаг разрешения прерывания;

Десятый бит – DF – флаг направления. Указывает направление обработки строк данных, определяет порядок обработки цепочек выполнения команд. Если DF=0, то идет обработка от меньших адресов к большим, если DF=1 – наоборот;

Одиннадцатый бит – ОF – флаг переполнения. Устанавливается при переполнении арифметико-логического устройства и т.д.

Старшие 4 бита – 1 – фиксированы, не используются.

2.3. Система прерываний в мп Intel 8086

Данный МП имеет более гибкую и разветвленную систему прерываний. Он способен реагировать на внешние прерывания (немаскируемый/маскируемый входы). В системе прерываний заложены программные прерывания, которые инициируются специальным кодом. Также имеются внутренние прерывания, возникающие при некорректной работе МП.

Указанный МП содержит векторную систему прерываний. Каждому типу прерываний соответствует свой вектор.

Часть векторов по умолчанию имеют строгое назначение, часть назначается программистом. Имеется 256 векторов прерываний.

Схема возможных источников прерываний представлена на рисунке 30.

Внешние прерывания

Внешние прерывания бывают маскированные и немаскированные. Если прерывание маскированное, то запрос может быть от контроллера прерываний или внешнего устройства.

Запрос на немаскируемое прерывание обычно используется для прерывания МП в критических режимах. Сигналом запроса на прерывание является сигнал аварии. Прерыванию присваивается фиксированный код (тип 2). Он автоматически формируется внутри процессора. При обслуживании прерывания цикл шины подтверждения прерывания не формируется, чем ускоряется реакция МП на поступивший запрос.

Внешние прерывания могут поступить в любой момент времени.

Программные прерывания

Данные прерывания осуществляются по 2-байтной команде INTn или по однобайтной команде INT3. Для двухбайтной команды тип прерывания указывается во втором байте. Однобайтное прерывание INT3 определено как прерывание в контрольной точке (точке разрыва). Такой точкой может быть любое место в программе, где необходимо прервать выполнение программы и выполнить какие-то действия.

Внутренние прерывания

Внутренние прерывания характеризуются типом, который либо предопределен, либо содержится в коде команды.

Данные прерывания не могут быть запрещены, за исключением работы МП в пошаговом режиме. Эти прерывания имеют более высокий приоритет по отношению к внешним.

Если МП переведен в пошаговый режим, то он реагирует на внешние и внутренние прерывания.

Таким образом, на поступающий запрос на прерывание INTR МП реагирует выполнением последовательно двух машинных циклов:

-

в первом машинном цикле МП указывает контроллеру прерываний, что запрос был воспринят и требуется обслуживание;

-

во втором машинном цикле контроллер прерываний выдает на шину данных байт данных, который содержит тип прерывания (0÷255).

Если МП работает в максимальном режиме, то на его выходе LOCK формируется сигнал занятости магистрали для сопроцессоров.

Таким образом, всего 256 типов прерывания. Каждый вектор занимает четыре ячейки памяти: два младших адреса – для записи смещения в сегменте, два старших – для записи начального смещения (базовый адрес сегмента).

Табл. 5

|

003FF 003FС

|

Тип 255 |

|

|

|

|

|

|

|

|

|

|

00008 |

|

|

00004 |

Тип 1 |

|

00000 |

Тип 0 |