6. Триггеры

6.1. Общие сведения. Триггерами, или спусковыми устройствами, называют устройства, имеющие два состояния устойчивого равновесия. Каждое из этих состояний может сохраняться сколь угодно длительное время. Переход из одного состояния устойчивого равновесия в другое осуществляется скачком под воздействием внешнего управляющего напряжения.

Перепады выходного напряжения или устойчивые состояния триггера можно принять в качестве логической информации «0» и «1». Поэтому триггер можно использовать в качестве запоминающего устройства, которое хранит один разряд числа, представленного в двоичном коде.

Триггеры подразделяются на две группы — статические и динамические. Статическими называют триггеры, у которых каждое состояние характеризуется неизменным уровнем (потенциалом) выходного напряжения. Статические триггеры называют также потенциальными. В динамических триггерах одно из состояний (обычно единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определенной частоты, а другое (нулевое) — отсутствием импульсов.

Статический триггер реализуется на двухкаскадном усилителе с положительной ОС. Каждый усилитель образует одно плечо триггера. Если оба плеча обладают симметрией по схемотехнике и по параметрам входящих в них элементов, то такой триггер называют симметричным. Если симметрия отсутствует, то триггер называется несимметричным.

Интегральные триггеры используются как самостоятельные устройства и, кроме того, входят в состав различных функциональных устройств: счетчиков, регистров, запоминающих устройств и т.п. Современные интегральные триггеры часто строятся на основе нескольких логических элементов, объединенных в одну микросхему. Они могут иметь несколько входов и различаться способами ввода входной информации.

На схемах входы триггера обозначают буквами латинского алфавита в соответствии с табл. 6.1. По названиям информационных входов называют и триггеры: RS-триггер, D-триггер, JK-триггер и др.

В зависимости от схемы управляющего устройства триггеры делятся на синхронные и асинхронные. Асинхронные триггеры имеют только информационные (логические) входы, и в них запись информации осуществляется в момент ее поступления. В синхронных триггерах запись информации, поступившей на информационные входы, происходит только при поступлении на синхронизирующий (тактирующий) вход дополнительного командного импульса. Синхронные триггеры могут иметь и асинхронные входы, которые обычно служат для установки триггера в нужное исходное состояние.

Асинхронные триггеры используются в качестве коммутаторов, ключей, счетчиков импульсов, делителей частоты повторения импульсов и т.п. Синхронные триггеры применяются в вычислительной и цифровой технике.

Таблица 6.1. Функциональное назначение входов триггера

|

Условное обозначение |

Назначение |

|

S R J K T D

V C |

Информационные входы

Вход для раздельной установки триггера в состояние 1 Вход для раздельной установки триггера в состояние 0 Вход для установки в состояние 1 JK-триггера Вход для установки в состояние 0 JK-триггера Счетный вход триггера Вход для установки триггера в состояния 0 или 1

Управляющие входы

Подготовительный вход для разрешения приема информации Подготовительный вход для осуществления приема информации. Вход синхронизации |

Триггеры, переключающиеся по уровню входных сигналов, называют триггерами со статическим управлением, а по фронтам и срезам — триггерами с динамическим управлением.

Рис. 6.1. Условные обозначения триггеров

На схемах триггер изображают прямоугольником, разделенным вертикальной линией на две части (рис. 6.1.): правая часть — основное поле, левая — дополнительное. В основном поле помещается буква Т, а в дополнительном у каждого входа пишется буква (метка), указывающая на его функциональное назначение в соответствии с табл. 6.1. Статические прямые входы и выходы отображают прямыми линиями без каких-либо индикаторов, а инверсные имеют дополнительный индикатор в виде маленького кружка на стороне прямоугольника (рис. 6.1, а). Динамические входы обозначают небольшими треугольниками. У прямых динамических входов, вызывающих «опрокидывание» триггера при изменении уровня сигнала от 0 к 1, острие треугольника направлено внутрь поля (рис. 6.1, б), а у инверсных, вызывающих опрокидывание триггера при изменении уровня сигнала от 1 до 0, — наружу (рис. 6.1, в).

У триггера может быть несколько информационных входов, связанных в группы операциями И либо ИЛИ. Группа входов, связанная операцией И, в дополнительном поле помечается символом логического умножения. Группа входов, связанная операцией логического сложения ИЛИ, дополнительных символов в условном обозначении не имеет (рис. 6.1, г).

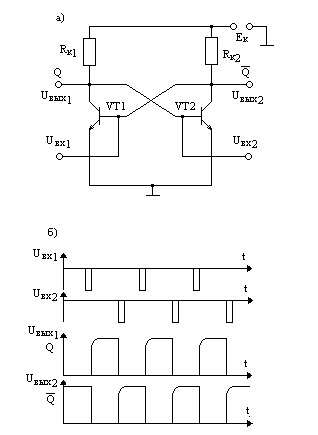

6.2. Симметричный

триггер на биполярных транзисторах.

Упрощенная

принципиальная схема симметричного

транзисторного триггера приведена на

рис. 6.2, а,

а его временные

диаграммы — на рис. 6.2, б.

Если допустить, что после подачи

напряжения источника

![]() на триггер оба транзистора VТ1

и VТ2

оказались открытыми, то вследствие даже

незначительного отличия параметров

элементов первого и второго плеч появятся

различия в коллекторных токах и

напряжениях, которые благодаря действию

положительной ОС будут увеличиваться

до тех пор, пока один из транзисторов

не закроется, а другой не перейдет в

режим насыщения.

на триггер оба транзистора VТ1

и VТ2

оказались открытыми, то вследствие даже

незначительного отличия параметров

элементов первого и второго плеч появятся

различия в коллекторных токах и

напряжениях, которые благодаря действию

положительной ОС будут увеличиваться

до тех пор, пока один из транзисторов

не закроется, а другой не перейдет в

режим насыщения.

Рис.6.2. Схема симметричного триггера (а) и графики напряжений на его входах и выходах

Если после подачи

напряжения

![]() транзистор VТ1

оказался в режиме насыщения, а транзистор

VТ2

— в режиме отсечки, то первый отрицательный

импульс, поступивший на базу VТ1,

вызывает уменьшение тока

транзистор VТ1

оказался в режиме насыщения, а транзистор

VТ2

— в режиме отсечки, то первый отрицательный

импульс, поступивший на базу VТ1,

вызывает уменьшение тока

![]() и увеличение напряжения

и увеличение напряжения

![]() .

Скачок напряжения

.

Скачок напряжения

![]() поступает на базу транзистора VТ2.

поступает на базу транзистора VТ2.

Это приводит к

увеличению тока

![]() и уменьшению напряжения

и уменьшению напряжения

![]() ,

которое передается на базу VТ1.

,

которое передается на базу VТ1.

В результате

действия положительной ОС транзистор

VТ1

запирается, а транзистор VТ2

отпирается и переходит в режим насыщения.

Такое состояние триггера сохраняется

до прихода отрицательного импульса на

базу транзистора VТ2

(второй вход). Уменьшение напряжения

![]() вызывает уменьшение тока

вызывает уменьшение тока

![]() и увеличение напряжения

и увеличение напряжения

![]() .

Создаются условия для нового срабатывания

триггера.

.

Создаются условия для нового срабатывания

триггера.

Транзистор VТ1 открывается и переходит в режим насыщения, а транзистор VТ2 запирается. В таком состоянии триггер будет находиться до поступления на первый вход следующего отрицательного импульса, который вызовет его «опрокидывание» в первое устойчивое состояние, и т. д.

Напряжения на

коллекторах транзисторов служат

выходными сигналами триггера. Из

приведенных графиков и принципа работы

следует, что уровни сигналов на выходах

являются взаимно инверсными и по

состоянию одного выхода можно судить

о состоянии другого. Один из выходов

называют прямым

и обозначают буквой

![]() .

Другой выход — инверсный

— обозначается

.

Другой выход — инверсный

— обозначается

![]() .

В силу симметрии схемы прямым или

инверсным может быть назначен любой

выход триггера.

.

В силу симметрии схемы прямым или

инверсным может быть назначен любой

выход триггера.

Состояние триггера

называют единичным,

если на прямом выходе имеется уровень

напряжения, соответствующий логической

единице, а на инверсном — логическому

нулю, т.е. при

![]() ,

,

![]() .

.

Вход, на который

подается сигнал, устанавливающий триггер

в состояние 1, обозначают буквой S.

Вход, на который поступает сигнал,

устанавливающий триггер в состояние 0

(![]() ,

,

![]() ),

обозначают R

(от англ. set

— установка и reset

— сброс). Такой триггер с раздельным

запуском получил название RS-триггера.

),

обозначают R

(от англ. set

— установка и reset

— сброс). Такой триггер с раздельным

запуском получил название RS-триггера.

6.3. RS-триггеры на логических элементах. Асинхронные RS-триггеры являются простейшими и выполняются на двух двухвходовых логических элементах типа И — НЕ либо ИЛИ — НЕ.

Асинхронные

RS-триггеры

на ЛЭ ИЛИ — НЕ.

Асинхронный RS-триггер

на двух логических элементах ИЛИ — НЕ

(рис. 6.3, а) содержит два информационных

входа

![]() и

и

![]() ,

на которых возможны четыре комбинации

логических сигналов:

,

на которых возможны четыре комбинации

логических сигналов:

![]() ;

;

![]() ;

;

![]() и

и

![]() .

.

Рис.6.3. Схема (а) и условное обозначение (б) асинхронного RS-триггера

на ЛЭ ИЛИ - НЕ с прямым управлением

Этим комбинациям

соответствуют определенные сигналы на

выходах триггера

![]() и

и

![]() ,

что отображается таблицей состояний

триггера (табл. 6.2). В ней приняты следующие

обозначения:

,

что отображается таблицей состояний

триггера (табл. 6.2). В ней приняты следующие

обозначения:

![]() и

и

![]() - моменты времени до и после срабатывания

триггера;

- моменты времени до и после срабатывания

триггера;

![]() и

и

![]() - сигналы на информационных входах в

момент

- сигналы на информационных входах в

момент

![]() ;

;

![]() и

и

![]() - сигналы на прямом выходе в моменты

времени

- сигналы на прямом выходе в моменты

времени

![]() и

и

![]() .

.

На основании таблицы состояний и карты Карно можно получить выражение для логической (переключательной) функции для RS-триггера с прямым входом, которая имеет вид:

![]() (6.1)

(6.1)

Таблица 6.2.

Состояния

![]() -триггера

с прямым управлением

-триггера

с прямым управлением

|

|

|

|

|

|

|

|

|

0 |

0 |

|

|

1 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

x |

Из таблицы состояний

и выражения (6.1) видно, что первая

комбинация входных сигналов

![]() не вызывает изменения состояния триггера.

Действительно, если к моменту времени

не вызывает изменения состояния триггера.

Действительно, если к моменту времени

![]() состояние триггера характеризовалось

сигналами

состояние триггера характеризовалось

сигналами

![]() ,

,

![]() ,

то в момент

,

то в момент

![]() на входах верхнего ЛЭ будут действовать

нулевые сигналы, и на его выходе

на входах верхнего ЛЭ будут действовать

нулевые сигналы, и на его выходе

![]() будет логическая 1 (

будет логическая 1 (![]() ).

В это же время на верхнем входе нижнего

ЛЭ будет логическая 1, на нижнем входе

).

В это же время на верхнем входе нижнего

ЛЭ будет логическая 1, на нижнем входе

![]() — логический 0, в результате чего на его

выходе

— логический 0, в результате чего на его

выходе

![]() будет поддерживаться логический 0 (

будет поддерживаться логический 0 (![]() ).

Аналогично можно показать, что при

данной комбинации входных сигналов

состояние триггера, соответствующее

выходным сигналам

).

Аналогично можно показать, что при

данной комбинации входных сигналов

состояние триггера, соответствующее

выходным сигналам

![]() ,

и

,

и

![]() ,

также не изменится. По этой причине

комбинацию входных сигналов

,

также не изменится. По этой причине

комбинацию входных сигналов

![]() называют режимом

памяти.

называют режимом

памяти.

Комбинация входных

сигналов

![]() переводит RS-триггер

в единичное состояние:

переводит RS-триггер

в единичное состояние:

![]() ,

,

![]() ,

если он перед этим находился в нулевом

состоянии (

,

если он перед этим находился в нулевом

состоянии (![]() ,

,

![]() ).

Если же RS-триггер

в момент времени

).

Если же RS-триггер

в момент времени

![]() находился в единичном состоянии (

находился в единичном состоянии (![]() ,

,![]() ),

то данная комбинация подтверждает это

состояние (

),

то данная комбинация подтверждает это

состояние (![]() ,

,

![]() ).

Поэтому вход

).

Поэтому вход

![]() называют единичным

входом.

называют единичным

входом.

Комбинация входных

сигналов

![]() обеспечивает нулевое состояние триггера.

Действительно, если

обеспечивает нулевое состояние триггера.

Действительно, если

![]() ,

,

![]() ,

то при поступлении сигналов

,

то при поступлении сигналов

![]() и

и

![]() на одном входе верхнего ЛЭ появится

логическая 1. Это вызовет появление на

его выходе логического 0 (

на одном входе верхнего ЛЭ появится

логическая 1. Это вызовет появление на

его выходе логического 0 (![]() ),

и на обоих входах нижнего ЛЭ будут

логические нули, а на его выходе

),

и на обоих входах нижнего ЛЭ будут

логические нули, а на его выходе

![]() — логическая единица. Если же триггер

находился в нулевом состоянии (

— логическая единица. Если же триггер

находился в нулевом состоянии (![]() ,

,

![]() ),

то комбинация входных сигналов

),

то комбинация входных сигналов

![]() состояние триггера не изменит, так как

на обоих входах верхнего ЛЭ будут

логические единицы, а нижнего ЛЭ —

логические нули, подтверждающие выходные

сигналы

состояние триггера не изменит, так как

на обоих входах верхнего ЛЭ будут

логические единицы, а нижнего ЛЭ —

логические нули, подтверждающие выходные

сигналы

![]() ,

,

![]() .

По этой причине вход

.

По этой причине вход

![]() называют нулевым

входом.

называют нулевым

входом.

При комбинации

входных сигналов

![]() на обоих выходах триггера появятся

логические нули (

на обоих выходах триггера появятся

логические нули (![]() ,

,

![]() ).

Если вслед за этим последует нейтральная

комбинация входных сигналов (

).

Если вслед за этим последует нейтральная

комбинация входных сигналов (![]() ),

то триггер с равной вероятностью примет

единичное или нулевое состояние. Поэтому

комбинацию входных сигналов

),

то триггер с равной вероятностью примет

единичное или нулевое состояние. Поэтому

комбинацию входных сигналов

![]() для рассматриваемого RS-триггера

называют запрещенной

и в таблице состояний отображают буквой

х.

для рассматриваемого RS-триггера

называют запрещенной

и в таблице состояний отображают буквой

х.

В рассмотренном триггере переключение состояний осуществляется единичными сигналами. Такой триггер называют триггером с прямым управлением и обозначают так, как показано на рис. 6.3, б.

Асинхронные RS-триггеры на ЛЭ И — НЕ. Асинхронный RS-триггер можно выполнить и на двух двухвходовых ЛЭ И —НЕ (рис. 6.4, а).

Рис. 6.4. Схема (а) и условное обозначение (б) асинхронного RS-триггера на логических элементах И — НЕ с инверсным управлением

В отличие от

RS-триггера

на ЛЭ ИЛИ — НЕ переключения данного

триггера осуществляются сигналами

логического 0. Такой триггер называют

триггером с

инверсным управлением

(![]() -триггер).

На функциональных схемах переключающие

входы

-триггер).

На функциональных схемах переключающие

входы

![]() -триггера

снабжаются индикаторами инверсии, а к

буквенным обозначениям входов добавляются

знаки отрицания (рис. 6.4, б). Состояния

триггера в зависимости от комбинаций

входных сигналов приведены в табл.6.3, а

его логическая (переключательная)

функция имеет вид:

-триггера

снабжаются индикаторами инверсии, а к

буквенным обозначениям входов добавляются

знаки отрицания (рис. 6.4, б). Состояния

триггера в зависимости от комбинаций

входных сигналов приведены в табл.6.3, а

его логическая (переключательная)

функция имеет вид:

![]() (6.2)

(6.2)

Таблица 6.3.

Состояния

![]() -триггера

с инверсным управлением

-триггера

с инверсным управлением

|

|

|

|

|

|

|

|

|

0 |

0 |

x |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

|

Из таблицы состояний

(6.3) и выражения (6.2) следует, что комбинация

входных сигналов

![]() является нейтральной,

а

является нейтральной,

а

![]() — запрещенной.

— запрещенной.

Если ко входам

![]() -триггера

добавить два инвертора (рис. 6.4, в), то

получится

-триггера

добавить два инвертора (рис. 6.4, в), то

получится

![]() -триггер,

подобный триггеру на элементах ИЛИ —

НЕ. Асинхронные

-триггер,

подобный триггеру на элементах ИЛИ —

НЕ. Асинхронные

![]() -триггеры

используются в качестве ячеек памяти

в оперативных запоминающих устройствах

(ОЗУ) статического типа (например, ИМС

К155РУ1).

-триггеры

используются в качестве ячеек памяти

в оперативных запоминающих устройствах

(ОЗУ) статического типа (например, ИМС

К155РУ1).

Синхронные

![]() -триггеры

на ЛЭ И — НЕ.

На рис. 6.5, а приведена структурная схема

синхронного

-триггеры

на ЛЭ И — НЕ.

На рис. 6.5, а приведена структурная схема

синхронного

![]() -триггера

со статическим управлением на ЛЭ И —

НЕ. Собственно триггер выполнен на

элементах

-триггера

со статическим управлением на ЛЭ И —

НЕ. Собственно триггер выполнен на

элементах

![]() и

и

![]() ,

а элементы

,

а элементы

![]() и

и

![]() образуют устройство управления. Кроме

информационных входов

образуют устройство управления. Кроме

информационных входов

![]() и

и

![]() ,

устройство управления имеет

синхронизирующий, или тактовый, вход

,

устройство управления имеет

синхронизирующий, или тактовый, вход

![]() ,

связанный с входами

,

связанный с входами

![]() и

и

![]() операциями И — НЕ. Поэтому информация

с входов

операциями И — НЕ. Поэтому информация

с входов

![]() и

и

![]() передается на собственно триггер только

при

передается на собственно триггер только

при

![]() .

.

Рис. 6.5. Схема (а) и условные обозначения

(б, в) синхронного

![]() -триггера

на логических элементах И -НЕ

-триггера

на логических элементах И -НЕ

Собственно триггер

управляется внутренними сигналами

![]() и

и

![]() .

Переключения осуществляются нулевыми

уровнями этих сигналов так же, как в

триггере на рис. 6.4, а. Так как ЛЭ

.

Переключения осуществляются нулевыми

уровнями этих сигналов так же, как в

триггере на рис. 6.4, а. Так как ЛЭ

![]() и

и

![]() осуществляют инверсию входных сигналов

осуществляют инверсию входных сигналов

![]() и

и

![]() ,

то нулевым уровням сигналов

,

то нулевым уровням сигналов

![]() и

и

![]() должны соответствовать единичные уровни

внешних информационных сигналов

должны соответствовать единичные уровни

внешних информационных сигналов

![]() и

и

![]() .

Работа триггера определяется таблицей

состояний (6.4) и его логической

(переключательной) функцией:

.

Работа триггера определяется таблицей

состояний (6.4) и его логической

(переключательной) функцией:

![]() (6.3)

(6.3)

Рассмотрим работу

синхронного

![]() -триггера,

приняв

-триггера,

приняв

![]() .

Если

.

Если

![]() ,

то ЛЭ

,

то ЛЭ

![]() и

и

![]() закрыты и

закрыты и

![]() .

Такая комбинация внутренних сигналов

.

Такая комбинация внутренних сигналов

![]() и

и

![]() является нейтральной для собственно

триггера, и он сохраняет свое состояние

является нейтральной для собственно

триггера, и он сохраняет свое состояние

![]() .

Это состояние не изменяется при любых

значениях информационных сигналов

.

Это состояние не изменяется при любых

значениях информационных сигналов

![]() и

и

![]() .

С приходом синхронизирующего импульса

(

.

С приходом синхронизирующего импульса

(![]() )

на входах ЛЭ

)

на входах ЛЭ

![]() будет действовать логическая 1, вследствие

чего

будет действовать логическая 1, вследствие

чего

![]() и

и

![]() . Так как

. Так как

![]() (поскольку

(поскольку

![]() и

и

![]() ),

то на входы ЛЭ

),

то на входы ЛЭ

![]() поступят сигналы

поступят сигналы

![]() и

и

![]() и на его выходе будет сигнал

и на его выходе будет сигнал

![]() .

Такое состояние будет сохраняться и

после прекращения действия синхронизирующего

импульса, так как при

.

Такое состояние будет сохраняться и

после прекращения действия синхронизирующего

импульса, так как при

![]() для собственно триггера опять возникнет

нейтральная комбинация

для собственно триггера опять возникнет

нейтральная комбинация

![]() .

.

Обратный переброс

триггера в состояние

![]() произойдет в момент действия следующего

синхронизирующего импульса при наличии

на информационных входах сигналов

произойдет в момент действия следующего

синхронизирующего импульса при наличии

на информационных входах сигналов

![]() .

Комбинация входных сигналов

.

Комбинация входных сигналов

![]() для рассмотренного триггера является

недопустимой, так как при

для рассмотренного триггера является

недопустимой, так как при

![]() возникнет недопустимая комбинация

возникнет недопустимая комбинация

![]() ,

создающая неопределенное состояние на

выходах триггера:

,

создающая неопределенное состояние на

выходах триггера:

![]() .

.

Условное обозначение

рассмотренного синхронного

![]() -триггера

с двумя информационными и одним

синхронизирующим входами дано на рис.

6.5, б.

-триггера

с двумя информационными и одним

синхронизирующим входами дано на рис.

6.5, б.