11. Сумматоры

Сумматором называется электронное устройство, выполняющее арифметическое суммирование кодов чисел.

Обычно сумматоры представляют собой комбинацию одноразрядных суммирующих схем. При сложении двух чисел, независимо от системы счисления, в каждом разряде производится сложение трех цифр:

-

цифры данного разряда первого слагаемого,

-

цифры данного разряда второго слагаемого,

-

цифры переноса из соседнего младшего разряда (1 или 0).

В результате сложения для каждого разряда получаются цифры суммы для этого разряда и цифра (1 или 0) переноса в следующий старший разряд. В таблице 11.1 показаны восемь возможных вариантов, возникающих при сложении двух двоичных чисел в одном разряде.

Таблица 11.1

-

Перенос из младшего разряда

X1

X2

S

Перенос в старший разряд

0

0

0

0

0

0

1

0

1

0

0

0

1

1

0

0

1

1

0

1

1

0

0

1

0

1

1

0

0

1

1

0

1

0

1

1

1

1

1

1

В параллельном сумматоре достигается более высокое быстродействие. В нем суммируемые коды поступают одновременно на все разряды.

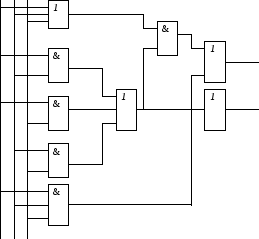

На рис. 11.1 приведена схема параллельного комбинационного сумматора.

Si

–1

Si

Si+

1

Si

–1

Si

Si+

1

Pi -1 Pi Pi+ 1 Pi+ 2

Xi –1 Yi –1 Xi Yi Xi + 1 Yi + 1

Рис.11.1 Схема параллельного комбинационного сумматора

В этом сумматоре, в каждом разряде одновременно формируется сумма. Хотя, если быть точным, то не совсем одновременно. На значение суммы влияет перенос, а он происходит последовательно и вносит некоторую задержку. При этом, до формирования окончательного результата на входах должны присутствовать входные сигналы Xi и Yi . Иногда суммирование разбивают на две операции:

-

суммирование двух слагаемых,

-

суммирование полученного результата с переносом из соседнего младшего разряда.

Каждая из этих операций выполняется полусумматором. На рис.11.2 приведена функциональная схема полусумматора и его условное обозначение.

Xi

Yi

Xi

Yi

Si

Pi + 1

Функциональная схема полусумматора

Xi

Si

Xi

Si

Yi Pi + 1

Условное обозначение полусумматора

Рис. 11.2 Полусумматор

В таблице 11.2 приведена карта состояний полусумматора.

Таблица 11.2

-

Xi

Yi

Si

Pi + 1

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Здесь Xi и Yi – входные данные (слагаемые),

Si – сумма,

Pi + 1 – единица переноса в старший разряд при переполнении младшего разряда.

На рис. 11.3 приведена функциональная схема и условное обозначение одноразрядного сумматора, а в таблице 11.3 представлена карта состояний.

Xi

Yi

Pi

Xi

Yi

Pi

Si

Pi + 1

Функциональная схема

Xi Si

Yi

Pi Pi + 1

Условное обозначение

Рис. 11.3 Одноразрядный сумматор

Таблица 11.3

-

Xi

Yi

Pi

Si

Pi + 1

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

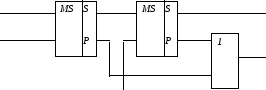

Сумматор можно реализовать и с помощью двух полусумматоров и логического элемента ИЛИ (Рис.11.4).

Xi

Si

Xi

Si

Yi

Pi + 1

Pi

Рис. 11.4 Функциональная схема сумматора

Суммирование многоразрядных кодов осуществляется с помощью одноразрядных сумматоров. При этом, в зависимости от способа ввода – вывода кодов и организации переносов, многоразрядные сумматоры бывают:

-

последовательного и

-

параллельного

принципа действия.

В последовательном сумматоре происходит поразрядное сложение кодов, начиная с младшего разряда, с помощью комбинационного сумматора на три входа. При этом перенос в старший разряд производится с задержкой до момента поступления следующего разряда слагаемых. Такой сумматор прост в реализации, но недостаточно быстродействующий.