- •Введение.

- •Цифровые устройства.

- •1. Комбинационные цифровые устройства.

- •1.1. Сумматор.

- •1.2.Шифраторы.

- •1.3.Дешифраторы.

- •1.4. Кодопреобразователь.

- •1.5. Коммутационные схемы.

- •1.5.1. Мультиплексоры.

- •1.5.2. Демультиплексор.

- •1.5.3. Мультиплексор-демультиплексор (универсальный коммутатор).

- •2. Конечные автоматы (последовательностные устройства).

- •2.1. Триггеры.

- •2.1.2. Асинхронный rs-триггер.

- •2.1.3.Синхронный rs-триггер.

- •2.2. Счетчики.

- •2.3. Регистры.

- •Литература.

- •1. Комбинационные цифровые устройства. 4

- •2. Конечные автоматы (последовательностные устройства). 16

-

2.3. Регистры.

Регистры – конечные автоматы, служащие для хранения или для сдвига информации. Сдвиг информации производится на последовательных регистрах, хранение записанной информации производится в параллельных регистрах. Основа построения регистров – D-триггеры.

Последовательные регистры.

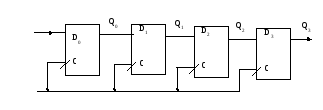

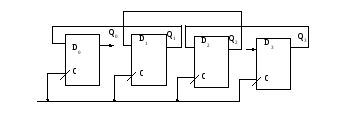

В регистрах данного типа производится преобразование информации, поэтому необходимо построение обратных связей между триггерами. Сдвиг информации может производиться как влево (с увеличением результата), так и вправо (с уменьшением результата). Таблицы состояний для трехразрядных регистров представлены табл.2.10 и табл 2.11. Соответственно, формулы обратных связей для регистров сдвига влево Di=Qi-1 и для сдвига вправо Di=Qi+1 . На рис. 2.24(а, б) показаны схемы трехразрядных регистров сдвига влево и вправо.

|

n |

D |

Q3 |

Q2 |

Q1 |

Q0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

0 |

0 |

|

4 |

0 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

0 |

0 |

1 |

Табл.2.10

|

n |

D |

Q3 |

Q2 |

Q1 |

Q0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

|

2 |

0 |

0 |

1 |

0 |

0 |

|

3 |

0 |

0 |

0 |

1 |

0 |

|

4 |

0 |

0 |

0 |

0 |

1 |

|

5 |

1 |

1 |

0 |

0 |

0 |

Табл.2.11

а)

б)

Рис.2.24 (а – регистр сдвига влево, б – регистр сдвига вправо).

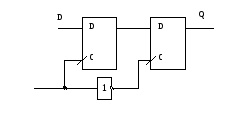

При сопоставимых по времени длительности синхроимпульса и задержке триггера информация может переписаться по одному такту синхронизации в несколько ячеек подряд. Для исключения таких сбоев между триггерами ставятся линии задержки или триггеры строятся по двухтактной схеме (рис.2.25).

Рис.2.25.

Параллельные регистры.

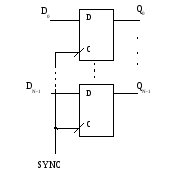

Такие регистры используются для временного хранения записанной информации, а также для разделения информационных шин. Обратных связей между триггерами не требуется. Существуют регистры-защелки (рис.2.26) и буферные регистры (рис.2.27). В защелку по фронту синхроимпульса записывается состояние шины D0 Dn-1. В отсутствии синхроимпульса все изменения состояния шины D0 Dn-1 не влияют на состояния выходов (шина Q0 Qn-1). Таким образом, с помощью защелки возможно разделение шин.

Рис.2.26

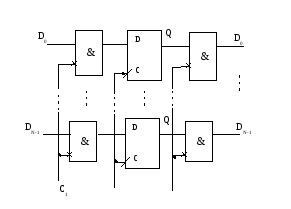

Буферные регистры используются в системах, содержащих большое количество регистров, где в каждый момент времени необходимо совершать обмен только между определенным источником и приемником. Примером может служить любая микропроцессорная система или отдельный процессор. В качестве буферов служат трехстабильные элементы. При подаче управления на такой элемент он выполняет функции конъюнктора, а при снятии управления разрывает цепь, и на выходе образуется высокий уровень при отсутствии токов. Такое состояние элемента называют третьим или высокоимпедансным. Из схемы двухбуферного регистра, рис.2.27 следует, что запись в буферный регистр возможна при C1=1 и подаче синхроимпульса, а считывание при C2=1 в любое время.

Рис.2.27.

По способу записи и считывания регистры классифицируются как последовательные, параллельные, параллельно-последовательные и последовательно-параллельные. В последовательно-параллельных регистрах запись происходит последовательным способом и, при заполнении регистра, включается параллельный буфер чтения. В параллельно-последовательных регистрах запись происходит параллельным способом через буфер записи, который в дальнейшем отключается, и включаются обратные связи последовательного регистра. Считывание производится последовательным способом.