- •Введение.

- •Цифровые устройства.

- •1. Комбинационные цифровые устройства.

- •1.1. Сумматор.

- •1.2.Шифраторы.

- •1.3.Дешифраторы.

- •1.4. Кодопреобразователь.

- •1.5. Коммутационные схемы.

- •1.5.1. Мультиплексоры.

- •1.5.2. Демультиплексор.

- •1.5.3. Мультиплексор-демультиплексор (универсальный коммутатор).

- •2. Конечные автоматы (последовательностные устройства).

- •2.1. Триггеры.

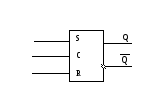

- •2.1.2. Асинхронный rs-триггер.

- •2.1.3.Синхронный rs-триггер.

- •2.2. Счетчики.

- •2.3. Регистры.

- •Литература.

- •1. Комбинационные цифровые устройства. 4

- •2. Конечные автоматы (последовательностные устройства). 16

-

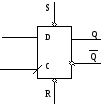

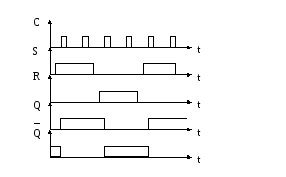

2.1.3.Синхронный rs-триггер.

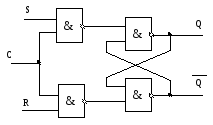

В синхронном RS-триггере изменение информации возможно лишь в тот интервал времени, когда активен синхровход C (рис.2.8).

Рис.2.8.

Таким образом, таблица переключений выглядит следующим образом (табл.2.3).

|

C n |

R n |

S n |

Q n-1 |

Q n |

Q |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

- |

- |

|

1 |

1 |

1 |

1 |

- |

- |

Табл.2.3.

Отсюда Qn=CnQn-1CnRn(SnQn-1); (2.6.)

Qn=CnQn-1CnSn(RnQn-1).

Схема такого триггера на элементах 2И-НЕ (рис.2.9).

Рис.2.9.

Действительно, при подаче «0» на вход C, состояние триггера определяется только обратными связями, т.е. сохраняется предыдущее состояние.

Схемы RS-триггеров служат основой для построения D-триггеров и JK-триггеров.

-

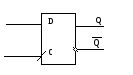

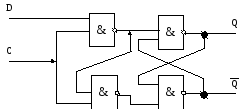

2.1.4.D-триггер.

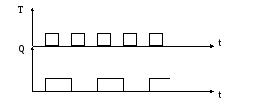

D-триггер(рис.2.10) служит для записи и хранения информации.

Рис.2.10.

Информация, поступающая на вход D, записывается в триггер в тот момент времени, когда на входе C появляется положительный перепад уровня (рис.2.10.1 ) .

Рис.2.10.1

Таблица переключений

|

|

C n |

D n |

Q n-1 |

Q n |

Q n |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

1 |

0 |

|

3 |

0 |

1 |

0 |

0 |

1 |

|

4 |

0 |

1 |

1 |

1 |

0 |

|

5 |

1 |

0 |

0 |

0 |

1 |

|

6 |

1 |

0 |

1 |

0 |

1 |

|

7 |

1 |

1 |

0 |

1 |

0 |

|

8 |

1 |

1 |

1 |

1 |

0 |

Табл.2.4.

Запрещенная комбинация отсутствует, поэтому записываем выражение для Qn

Qn=CnQn-1CnDn (2.7.)

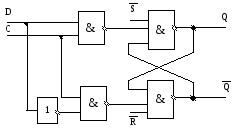

Если сравнить это выражение с аналогичным для синхронного RS-триггера, очевидно, что D-вход получен из комбинации входов R и S, включенных инверсно (рис.2.11).

Рис.2.11.

Установка сигнала в такой схеме происходит с задержкой на инверторе, отсюда и название триггера - D, от слова delay – задержка. Для возможности принудительной установки или сброса в триггере вводятся асинхронные RS-входы, активизируемые нулевым уровнем (рис.2.12а, б). Состояние входа D не должно изменяться во время действия синхроимпульса. Существует структура с динамическим синхровходом (рис.2.12в). В этом случае состояние выходов может измениться только при изменении состояния синхровхода с «0» на «1», благодаря применению бистабильных ячеек 1-2 и 3-4.

а)

б)

в)

Рис.2.12 D-триггер (а - структура; б – условное обозначение; в – динамический синхровход).

-

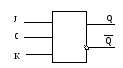

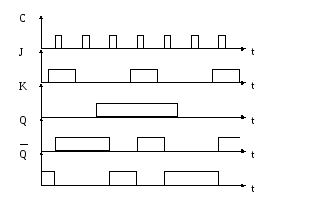

2.1.5. JK-триггер.

Рис.2.13.

Этот триггер (рис.2.13.) универсален. Он сочетает переключательные свойства T-триггера и возможности установки состояния RS-триггера. Перезапись в триггере возможна только во время подачи на вход C единичного перепада.

Подобно RS-триггеру JK-триггер имеет два входа установок: J - установка «1», K – установка «0». Входы активны при подаче «1». Эти входы являются информационными. В отсутствии активного уровня на входах триггер хранит предыдущее состояние. Управление по обоим входам, J и K, приводит к переключению триггера. Таблица переключений (табл.2.5.).

|

С n |

K n |

J n |

Q n-1 |

Q n |

Q n |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

0 |

1 |

Табл.2.5.

Триггер не имеет неопределенных состояний, поэтому запишем выражение только для Qn

Qn=CnQn-1Cn(KnQn-1JnQn-1) (2.8.)

Упрощенная таблица переключений для JK-входов (табл.2.6.).

|

K n |

J n |

Q n |

|

0 |

0 |

Q n-1 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

Q |

Табл.2.6.

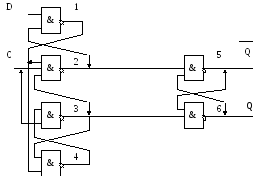

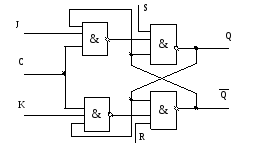

Схема JK-триггера, рис.2.14.

Рис.2.14.

В отличие от D-триггера, в JK-триггере обратными связями охвачены также входные элементы И-НЕ. Это и создает возможность функционирования этого триггера в режиме T-триггера при J=K=1. Триггер имеет асинхронные установочные входы R и S. Состояние информационных входов J и K во время действия синхроимпульса изменяться не должно.

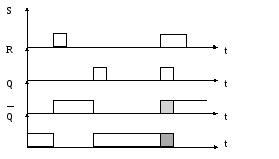

Диаграммы работы триггеров (рис.2.15.)

n

n

n-1

n-1