- •Мультиметр

- •Генератор слов

- •Логический анализатор

- •Логический преобразователь

- •Осциллограф.

- •Разработка схем цифровых устройств

- •5.1. Вывод элементов схем на рабочую поверхность

- •Монтаж схем

- •Синхронные символьно-ориентированные и бит-ориентированные протоколы

- •Передача с установлением соединения и без установления соединения

- •Максимальная производительность сети Ethernet

- •Форматы кадров технологии Ethernet

- •Глобальные связи на основе сетей с коммутацией каналов

- •Типы адресов стека tcp/ip

- •Источники и типы записей в таблице маршрутизации:

- •Фрагментация ip-пакетов

- •5.9. Приклад обробки пеpеpивань в захищеному режимi

- •5.9.1. Опис програми p_int

- •Времянезависимые способы защиты от копирования Инженерные дорожки

- •Нестандартная длина сектора

- •Способы защиты, опирающиеся на временные параметры

- •Проверка чередования секторов на дорожке

- •Монолитные системы

- •Многоуровневые системы

- •Модель клиент-сервер и микроядра

- •Технические характеристики системной платы

- •Пятие цветовой гармонии :

- •Транзакции и целостность баз данных

- •Журнализация изменений бд

-

ЛОГІЧНІ ЕЛЕМЕНТИ ТТЛ/ТТЛШ: БАЗОВИЙ ЛОГІЧНИЙ ЕЛЕМЕНТ. АНАЛІЗ АМПЛІТУДНО-ПЕРЕДАТОЧНОЇ (АМПЛІТУДНОЇ АБО СТАТИЧНОЇ) ХАРАКТЕРИСТИКИ. СТАТИЧНІ ТА ДИНАМІЧНІ ПАРАМЕТРИ.

Логический элемент (вентиль) — это электронная схема, выполняющая некоторую простейшую логическую операцию. На рисунке приведены примеры условных графических обозначений некоторых логических элементов.

Логический элемент может быть реализован в виде отдельной интегральной схемы. Часто интегральная схема содержит несколько логических элементов.

Логические элементы используются в устройствах цифровой электроники для выполнения простого преобразования логических сигналов.

Наиболее широко используются следующие классы логических элементов: ТТЛ(транзисторно-транзисторная логика), ТТЛШ (транзисторно-транзисторная логика с диодами Шоттки), КМОП, ЭСЛ.

Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, и сложный инвертор (рис. слева). Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ.

Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами Шоттки (транзисторы Шоттки).

|

Базовый логический элемент ТТЛШ. В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29,а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29,6. Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. Транзистор VT4 — обычный биполярный транзистор.

|

|

Е сли

оба входных напряжения Uвх1

и Uвх2

имеют высокий уровень, то диоды VD3 и

VD4 закрыты, транзисторы VT1, VT5 открыты и

на выходе имеет место напряжение низкого

уровня. Если хотя бы на одном входе

имеется напряжение низкого уровня, то

транзисторы VT1 и VT5 закрыты, а транзисторы

VT3 и VT4 открыты, и на входе имеет место

напряжение низкого уровня. Полезно

отметить, что транзисторы VT3 и VT4

образуют так называемый составной

транзистор (схему Дарлингтона).

сли

оба входных напряжения Uвх1

и Uвх2

имеют высокий уровень, то диоды VD3 и

VD4 закрыты, транзисторы VT1, VT5 открыты и

на выходе имеет место напряжение низкого

уровня. Если хотя бы на одном входе

имеется напряжение низкого уровня, то

транзисторы VT1 и VT5 закрыты, а транзисторы

VT3 и VT4 открыты, и на входе имеет место

напряжение низкого уровня. Полезно

отметить, что транзисторы VT3 и VT4

образуют так называемый составной

транзистор (схему Дарлингтона).

Амплітудно-передаточна характеристика.

При нулевом напряжении на входе элемента ТТЛ выходное напряжение соответствует высокому логическому уровню U1вых (точка А).

Увеличение входного напряжения до величины 1,1 В соответствует закрытому состоянию сложного инвертора и практически не изменяет напряжение на выходе элемента. При напряжении на входе более 1,1 В (точка В) начинает открываться транзистор VT2, а транзисторVT4 остается закрытым, т.к. его переход база-эмиттер шунтируется резистором R3. Увеличение тока через транзистор VT2 вызывает увеличение падения напряжения на резисторах R2 и R3. Выходное напряжение эмиттерного повторителя VT3 (т.е. выходное напряжение ТТЛ элемента) уменьшается с ростом падения напряжения на R2 (участок В-С).

Увеличение

падения напряжения на R3 до 0,5..0,6 В приводит

к открыванию транзистора VT4 (см. точку

С). Все транзисторы переходят в активный

режим. Малые изменения входного напряжения

(![]() Uвх)

вызывают значительное уменьшение

выходного напряжения (

Uвх)

вызывают значительное уменьшение

выходного напряжения (![]() Uвых).

На участке C-F логический элемент

работает как аналоговый усилитель с

коэффициентом усиления по напряжению:

Ku =

Uвых).

На участке C-F логический элемент

работает как аналоговый усилитель с

коэффициентом усиления по напряжению:

Ku =

![]() Uвых

/

Uвых

/

![]() Uвх.

Uвх.

Большинство реальных ТТЛ элементов имеют коэффициент усиления Ku в пределах от 5 до 20.

Правее точки F, когда увеличение входного напряжения приводит к насыщению транзисторов VT2 и VT4, дальнейшее изменение выходного напряжения происходить не может. Этот уровень выходного напряжения называется логическим нулем ТТЛ элементов и составляет : U0вых = 0,1...0,4 В. Точка D, лежащая на пересечении передаточной характеристики с биссектрисой первого квадранта (т.е. с прямой, на которой : Uвых = Uвх), определяет пороговый уровень напряжения Uпор (примерно 1,3..1,4 Вольта), разделяющий низкий и высокий логические уровни. Расстояния между низким логическим уровнем ТТЛ (U0 = 0,4 В) и пороговым напряжением (Uпор = 1,3 В), а также между высоким логическим уровнем ТТЛ (U1 > 3 В) и пороговым напряжением называются ЗАПАСОМ ПОМЕХОУСТОЙЧИВОСТИ. Этот запас определяет максимальное напряжение помехи на входе элемента, не изменяющее логическое состояние выхода.

Для ТТЛШ элементов характеристика имеет аналогичный характер за исключением того, что выходное напряжение логического нуля U0вых = 0,4..0,6 В, что является недостатком (следствие, уменьшенный на 0,2 Вольта запас помехоустойчивости).

Рассмотрим наиболее важные из параметров.

Б ыстродействие

характеризуют временем задержки

распространения сигнала tзр и максимальной

рабочей частотой Fмакс. Обратимся к

идеализированным временным диаграммам,

соответствующим элементу НЕ (инвертору)

(рис. 3.24). Через Uвх1 и Uвых1 обозначены

уровни входного и выходного напряжений,

соответствующие логической единице, а

через Uвх0 и Uвых0 — соответствующие

логическому нулю. Различают время

задержки tзр10 распространения при

переключении из состояния 1 в состояние

0 и при переключении из состояния 0 в

состояние 1 — tзр01,

а

также среднее

время задержки распространения tзр,

причем

ыстродействие

характеризуют временем задержки

распространения сигнала tзр и максимальной

рабочей частотой Fмакс. Обратимся к

идеализированным временным диаграммам,

соответствующим элементу НЕ (инвертору)

(рис. 3.24). Через Uвх1 и Uвых1 обозначены

уровни входного и выходного напряжений,

соответствующие логической единице, а

через Uвх0 и Uвых0 — соответствующие

логическому нулю. Различают время

задержки tзр10 распространения при

переключении из состояния 1 в состояние

0 и при переключении из состояния 0 в

состояние 1 — tзр01,

а

также среднее

время задержки распространения tзр,

причем

![]() Время

задержки принято определять по перепадам

уровней 0,5Uвх

и 0,5Uвых.

Максимальная рабочая

частота Fмакс

— это частота, при которой сохраняется

работоспособность схемы. Нагрузочная

способность характеризуется коэффициентом

объединения по входу Коб

и коэффициентом разветвления

по выходу Краз

(иногда используют термин «коэффициент

объединения по выходу»). Величина Коб

— это число

логических входов, величина Краз

— максимальное число

однотипных логических элементов, которые

могут быть подключены к выходу данного

логического элемента.

Типичные значения их таковы: Коб

= 2...8, Краз

= 4...10. Для

элементов с повышенной нагрузочной

способностью Краз

= 20...30.

Время

задержки принято определять по перепадам

уровней 0,5Uвх

и 0,5Uвых.

Максимальная рабочая

частота Fмакс

— это частота, при которой сохраняется

работоспособность схемы. Нагрузочная

способность характеризуется коэффициентом

объединения по входу Коб

и коэффициентом разветвления

по выходу Краз

(иногда используют термин «коэффициент

объединения по выходу»). Величина Коб

— это число

логических входов, величина Краз

— максимальное число

однотипных логических элементов, которые

могут быть подключены к выходу данного

логического элемента.

Типичные значения их таковы: Коб

= 2...8, Краз

= 4...10. Для

элементов с повышенной нагрузочной

способностью Краз

= 20...30.

Помехоустойчивость в статическом режиме характеризуют напряжением Uист, которое называют статической помехоустойчивостью. Это такое максимально допустимое напряжение статической помехи на входе, при котором еще не происходит изменение выходных уровней логического элемента.

Важным параметром является мощность, потребляемая микросхемой от источника питания. Если эта мощность различна для двух логических состояний, то часто указывают среднюю потребляемую мощность для этих состояний.

Важными являются также следующие параметры:

напряжение питания;

входные пороговые напряжения высокого и низкого уровня Uвх 1порог и Uвх 0порог, соответствующие изменению состояния логического элемента;

выходные напряжения высокого и низкого уровней Uвых1 и Uвых0

1.2 ЛОГІЧНІ ЕЛЕМЕНТИ З ТРЬОМА СТАНАМИ ВИХОДУ. ПРИНЦИП ДІЇ. ВПОРЯДКУВАННЯ РОБОТИ ДЕКІЛЬКОХ ЕЛЕМЕНТІВ НА ОДНУ СПІЛЬНУ ЛІНІЮ ІНТЕРФЕЙСУ (МАГІСТРАЛЬНІ ІНТЕРФЕЙСИ)

Ч асто

возникает необходимость подключения

выходов нескольких

цифровых микросхем к одной нагрузке.

Одним из

способов объединения выходов является

использование в

выходных каскадах микросхем транзисторов,

один из выводов

которых (коллектор, эмиттер, сток, исток)

никуда

не подключен. Такой вывод называют

открытым.

асто

возникает необходимость подключения

выходов нескольких

цифровых микросхем к одной нагрузке.

Одним из

способов объединения выходов является

использование в

выходных каскадах микросхем транзисторов,

один из выводов

которых (коллектор, эмиттер, сток, исток)

никуда

не подключен. Такой вывод называют

открытым.

Покажем схематически (рис. 3.25), как объединяются выходы микросхем с открытым коллектором. Такую схему называют «монтажным (проводным) ИЛИ».

Если

открытым является коллектор транзистора

п-р-п-типа,

эмиттер транзистора

р-п-р-типа,

сток транзистора

с каналом n-типа,

исток транзистора с каналом р-типа,

то вывод обозначают символом![]() .

Если открытым

является коллектор транзистора

p-n-р-типа,

эмиттер транзистора

n-р-n-типа,

сток транзистора с каналом р-типа,

исток транзистора с каналом n-типа,

вывод обозначают

символом

.

Если открытым

является коллектор транзистора

p-n-р-типа,

эмиттер транзистора

n-р-n-типа,

сток транзистора с каналом р-типа,

исток транзистора с каналом n-типа,

вывод обозначают

символом![]() .

.

Выходные

каскады некоторых микросхем могут

работать в таком

режиме, когда микросхема оказывается

фактически

отключенной от нагрузки. Это так

называемое третье

(высокоимпедансное) состояние микросхемы.

Использование третьего состояния

является еще одним способом

объединения выходов микросхем, который

широко

используется в вычислительной технике,

при подключении к

общей шине многих устройств. Приведем

фрагмент

схемы, поясняющей возникновение третьего

состояния

(рис. 3.26). Если оба транзистора закрыты,

то микросхема и

нагрузка фактически являются

разъединенными. Наличие третьего

состояния обозначают символом

![]()

П ри

использовании в едином цифровом

устройстве микросхем

различных серий, и в особенности различных

логик, может возникнуть

проблема согласования уровней входных

и выходных напряжений. Для указанных

целей производятся

специальные микросхемы, которые называют

преобразователями уровня сигналов.

ри

использовании в едином цифровом

устройстве микросхем

различных серий, и в особенности различных

логик, может возникнуть

проблема согласования уровней входных

и выходных напряжений. Для указанных

целей производятся

специальные микросхемы, которые называют

преобразователями уровня сигналов.

1.3 ЛОГІЧНІ ЕЛЕМЕНТИ МОП/КМОП: БАЗОВИЙ ЛОГІЧНИЙ ЕЛЕМЕНТ. АНАЛІЗ АМПЛІТУДНО-ПЕРЕДАТОЧНОЇ (АМПЛІТУДНОЇ АБО СТАТИЧНОЇ) ХАРАКТЕРИСТИКИ. СТАТИЧНІ ТА ДИНАМІЧНІ ПАРАМЕТРИ.

В микросхемах n-МОП и р-МОП используются ключи на МОП-транзисторах с n-каналом и динамической нагрузкой и на МОП-транзисторах с p-каналом.

Р ассмотрим

базовый элемент логики п-МОП,

реализующий функцию ИЛИ-НЕ (рис. 3.31). Он

состоит

из нагрузочного транзистора Т3

и двух управляющих

транзисторов Т1

и

Т2.

Если оба транзистора T1

и Т2

закрыты,

то на выходе устанавливается высокий

уровень напряжения.

Если одно или оба напряжения и1

и и2

имеют

высокий уровень, то открывается один

или оба транзистора

Т1

и

Т2

и на входе устанавливается низкий

уровень

напряжения, т. е. реализуется функция

ассмотрим

базовый элемент логики п-МОП,

реализующий функцию ИЛИ-НЕ (рис. 3.31). Он

состоит

из нагрузочного транзистора Т3

и двух управляющих

транзисторов Т1

и

Т2.

Если оба транзистора T1

и Т2

закрыты,

то на выходе устанавливается высокий

уровень напряжения.

Если одно или оба напряжения и1

и и2

имеют

высокий уровень, то открывается один

или оба транзистора

Т1

и

Т2

и на входе устанавливается низкий

уровень

напряжения, т. е. реализуется функция

![]()

Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).

Р ассмотрим

КМОП — логический элемент, реализующий

функцию ИЛИ-НЕ (рис. 3.32), Если входные

напряжения

имеют низкие уровни (и1

и

и2

меньше

порогового напряжения

«-МОП-транзистора Uзи

порогn),

то транзисторы

Т1

и

Т2

закрыты, транзисторы Т3

и Т4

открыты и выходное

напряжение имеет высокий уровень. Если

одно или

оба входных напряжения и1

и

и2

имеют

высокий уровень,

превышающий Uзи

порогn

,

то

открывается один или оба транзистора

Тх

и Т2,

а между истоком и затвором одного или

обоих транзисторов Т3

и Т4

устанавливается низкое напряжение,

что приводит к запиранию одного или

обоих

транзисторов Т3

и Т4,

а следовательно, на выходе устанавливается

низкое напряжение. Таким образом, этот

элемент

реализует функцию

ассмотрим

КМОП — логический элемент, реализующий

функцию ИЛИ-НЕ (рис. 3.32), Если входные

напряжения

имеют низкие уровни (и1

и

и2

меньше

порогового напряжения

«-МОП-транзистора Uзи

порогn),

то транзисторы

Т1

и

Т2

закрыты, транзисторы Т3

и Т4

открыты и выходное

напряжение имеет высокий уровень. Если

одно или

оба входных напряжения и1

и

и2

имеют

высокий уровень,

превышающий Uзи

порогn

,

то

открывается один или оба транзистора

Тх

и Т2,

а между истоком и затвором одного или

обоих транзисторов Т3

и Т4

устанавливается низкое напряжение,

что приводит к запиранию одного или

обоих

транзисторов Т3

и Т4,

а следовательно, на выходе устанавливается

низкое напряжение. Таким образом, этот

элемент

реализует функцию

![]() и

потребляет мощность

от источника питания лишь в короткие

промежутки

времени, когда происходит его переключение.

и

потребляет мощность

от источника питания лишь в короткие

промежутки

времени, когда происходит его переключение.

|

|

|

|

n-МОП |

КМОП |

При нулевом входном напряжении (Uвх = 0) канал имеет очень большое сопротивление и на выход ключа подается напряжение питания через резистор R. Выходное напряжение логической единицы (U1вых) равно напряжению питания +Е. При увеличении входного напряжения выше U' сопротивление канала постепенно уменьшается и на выход подается часть напряженияисточника питания с делителя, образованного сопротивлением канала и резистором R (участок А-В на рис. слева). Сопротивление канала не может уменьшится до нуля. При входном напряжении выше U" сопротивление канала достигает минимальной величины и дальнейшее увеличение входного напряжения не влияет на сопротивление канала.

При входном напряжении выше U" выходное напряжение логического нуля (U0вых) определяется соотношением : U0вых = Е * Rк мин / (R + Rк мин). Где : Rк – минимальное сопротивление канала.

Величины U', U" и Rк мин - определяются технологическими параметрами: степень легирования канала, степень шероховатости поверхности канала, геометрические размеры канала; а также напряжением питания электронного ключа.

На

участке А-В, т.е. при входном напряжении

от U' до U" электронный ключ работает

как аналоговый усилитель с коэффициентом

усиления Ku =

![]() Uвых

/

Uвых

/

![]() Uвх

.

Uвх

.

Точка пересечения передаточной характеристики с биссектрисой первого квадранта (точка С на рис. слева) определяет пороговое напряжение Uпор электронного ключа.

Переходная характеристика КМОП ключа приведена на рис. справа. При нулевом входном напряжении транзистор с n-каналом VT1 закрыт (сопротивление канала очень велико), а транзистор с р-каналом VT2 открыт (сопротивление канала – Rк мин ), т.к. к его затвору относительно истока приложено напряжение источника питания.

Поэтому

на выходе ключа напряжение логической

единицы : U1вых = +Е. При увеличении

входного напряжения выше U' (точка А

на рис. справа) начинает уменьшаться

сопротивление канала транзистора VT1,

а сопротивление канала VT2 - увеличивается.

Выходное напряжение постепенно

уменьшается и в конце участка А-В

практически доходит до нуля (U0вых = 0)

при полном закрывании транзистора VT2 и

уменьшении сопротивления канала

транзистора VT1 до величины Rк мин На

участке А-В оба транзистора работают в

активном режиме усиления аналогового

сигнала с коэффициентом усиления по

напряжению: Ku =

![]() Uвых

/

Uвых

/

![]() Uвх

.

Uвх

.

При этом оба канала имеют конечное сопротивление и через два транзистора течет сквозной ток от источника питания. С увеличением входного напряжения выше U" канал транзистора VT2 закрывается и ток через КМОП ключ от источника питания не потребляется. Таким образом, при входном напряжении ниже U' а также выше U" ток через КМОП ключ от источника питания практически не течет. Статическая потребляемая мошность близка к нулю. Пороговое напряжение Uпор определяется как точка пересечения передаточной характеристики с биссектрисой первого квадранта (точка С). Пороговое напряжение почти равно половине напряжения источника питания. Участок с напряжением U'- U" примерно равен 10..20% от напряжения источника питания, но имеет технологический разброс относительно середины напряжения источника питания. Поэтому входное напряжение низкого логического уровня U0вх должно быть менее 1/3 напряжения источника питания, а входное напряжение высокого логического уровня U1вх должно быть более 2/3 напряжения питания. Абсолютное значение напряжения источника питания +Е может изменяться в широких пределах от 3 до 15 Вольт. Это позволяет питать КМОП логические схемы от нестабилизированного источника питания, что значительно упрощает и удешевляет источник питания.

Характеристики рассмотренных элементов логики:

|

Диапазон напряжений питания, В |

3..15 |

|

Диапазон рабочих температур |

-40..+85 |

|

Входное напряжение (U1вх/ U0вх) |

>3,15/ < 0,9 |

|

Выходное напряжение (U1вых/ U0вых) |

Eп / 0,1 |

|

Входной ток, мкА (I1вх/I0вх) |

< 0,3/< 0,3 |

|

Выходной ток, мА (I1вых/I0вых) |

0,5/0,5 |

|

Максимальн.частота переключения, МГц |

до 150 МГц |

1.4 ТРИГЕРИ: КЛАСИФІКАЦІЯ ТА КОРОТКА ХАРАКТЕРИСТИКА РІЗНИХ ТИПІВ ТРИГЕРІВ. ОСОБЛИВОСТІ СХЕМОТЕХНІЧНОЇ РЕАЛІЗАЦІЇ ТА ФУНКЦІОНУВАННЯ.

Триггеры -это устройства предназначенные для хранения одного разряда информации. Триггеры имеют два устойчивых состояния: состояние "0" и состояние "1" .

RS Вход R - это вход установки триггера в состояние логического 0, вход S - это вход установки триггера в состояние логической 1. Асинхронным - называется такой триггер, который меняет свое состояние в момент подачи входного сигнала на входы S и R. Активным сигналом для этой схемы является логическая 1. Работа триггера определяется таблицей переходов.

|

|

|

|

|

||||||||||||||||||||

|

Асинх. RS. |

Асинх. RS. УГО |

Таблица переходов |

Временные хар-ки |

Кроме вышеприведенного асинхр. RS триггера с прямыми входами применяются также асинхр. RS триггера с инверсными входами и синхронные RS триггеры.

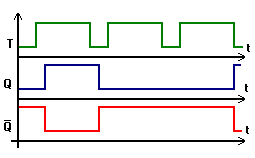

T-тригер

|

|

|

|

|||||||||

|

T-тригер |

Таблица переходов |

Временные хар-ки |

Это устройство с двумя устойчивыми состояниями и одним информационным входом Т ,такой триггер называется асинхронный Т-триггер. Т-триггер работает по заднему фронту информационного сигнала. С приходом 1 на вход Т, триггер меняет свое состояние на противоположное.

D-тригер

|

|

|

|

|

||||||||||||||||

|

T-тригер |

T-тригер УГО |

Таблица переходов |

Временные хар-ки |

D -триггер

(триггер задержки) - это устройство

с двумя устойчивыми состояниями, и одним

информационным входом.

-триггер

(триггер задержки) - это устройство

с двумя устойчивыми состояниями, и одним

информационным входом.

JK-тригер

При подаче переднего фронта импульса на вход С, начинает работать первый синхронный RS-триггер,

который построен на элементах 1,2,3,4. Значение на выходе RS-триггера определяется значением на входе Jи K. Второй RS-триггер находится в режиме хранения. При подаче на вход С заднего фронта синхроимпульса, первый RS-триггер переходит в режим хранения. Его значение на выходе поступает на второй RS-триггер.

|

|

|

|

1.5 РЕГІСТРИ: ПРИЗНАЧЕННЯ ТА КЛАСИФІКАЦІЯ. ПАРАЛЕЛЬНІ ТА ПОСЛІДОВНІ РЕГІСТРИ. ОСОБЛИВОСТІ СХЕМОТЕХНІЧНОЇ РЕАЛІЗАЦІЇ ТА ФУНКЦІОНУВАННЯ.

Назначение регистров – прием, хранение и выдача двоично-кодированной информации (двоичных чисел, слов). Они используются в качестве безадресных запоминающих устройств, преобразователей и генераторов кодов, устройств временной задержки цифровой информации, делителей частоты и др.

Классификация:

Различают параллельные регистры, последовательные, последовательно-параллельные и параллельно-последовательные. Регистры бывают парафазные и однофазные (Однофазные - поступает код числа. Парафазные - вместе с кодом числа поступает и его инверсия)

ПАРАЛЛЕЛЬНЫЕ РЕГИСТРЫ применяются для хранения информации, представленной в виде двоичного кода. Такие регистры должны по тактовому разрешающему сигналу (это может быть короткий импульс или фронт импульса) принимать параллельный код входной информации и хранить его до прихода следующего разрешающего сигнала. Для построения параллельных регистров наиболее удобны однотактные или двухтактные D-триггеры. На рис. показан пример параллельного регистра на однотактных D-триггерах, управляемых потенциалом. В момент подачи на синхровходы С1, С2 коротких положительных импульсов двоичный код со входов D1...D4 защелкивается в триггеры и может быть прочитана на выходах Q1...Q4.

D1│ D2│ D3│ D4│

│ ┌─┬───┐ │ ┌─┬───┐ │ ┌─┬───┐ │ ┌─┬───┐

└─┤D│ T1├──┐ └─┤D│ T2├──┐ └─┤D│ T3├──┐ └─┤D│ T4├──┐

│ │ │ │ │ │ │ │ │ │ │ │ │ │ │ │

┌─┤C│ o │ ┌─┤C│ o │ ┌─┤C│ o │ ┌─┤C│ o │

С1│ └─┴───┘ │ │ └─┴───┘ │ С2│ └─┴───┘ │ │ └─┴───┘ │

──┴──────────│────┘ │ ──┴──────────│────┘ │

│Q1 │Q2 │Q3 │Q4

Параллельный регистр на однотактных D-триггерах

ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ (или регистры сдвига) широко применяются в цифровой вычислительной технике для преобразования последовательного кода в параллельный, или параллельного в последовательный.

Последовательные регистры можно реализовать ТОЛЬКО на двухтактных триггерах, управляемых фронтом. На рис. приведена схема сдвигающего регистра на последовательно соединенных D-триггерах.

D1 ┌─┬───┐Q1│ ┌─┬───┐Q2│ ┌─┬───┐Q3│ ┌─┬───┐ Qn

────┤D│ T1├──┴─┤D│ T2├──┴─┤D│ T3├──┴─∙∙∙─┤D│ Tn├────

│ │ │ │ │ │ │ │ │ │ │ │

┌─/C│ o ┌─/C│ o ┌─/C│ o ┌─/C│ o

C │ └─┴───┘ │ └─┴───┘ │ └─┴───┘ │ └─┴───┘

───┴──────────┴──────────┴──────────∙∙∙─┘

Вход D1 первого триггера служит для приема в регистр информации в виде последовательного кода.

По восходящему фронту на входе "С" информация со входа D1 запишется в первый триггер, а логический уровень, который был на выходе Q1 до начала восходящего фронта тактового импульса, запишется во второй триггер. И так каждый последующий триггер устанавливается в состояние, в котором до этого находился предыдущий, осуществляя тем самым сдвиг информации на один разряд вправо.

1.6 ЛІЧИЛЬНИКИ: ПРИЗНАЧЕННЯ ТА КЛАСИФІКАЦІЯ. АСИНХРОННІ ЛІЧИЛЬНИКИ. ОСОБЛИВОСТІ СХЕМОТЕХНІЧНОЇ РЕАЛІЗАЦІЇ ТА ФУНКЦІОНУВАННЯ.

Счетчики - это устройства предназначенные для подсчета числа сигналов, поступающих на его вход и фиксация этого числа в виде кода хранящегося в триггерах. Количество разрядов счетчика определяется наибольшим числом, которое должно быть получено в каждом конкретном случае. Для подсчета и выдачи результата счетчики имеют один вход и n выходов, где n -количество разрядов. В общем случае счетчик имеет 2ⁿ устойчивых состояния, включая и 0 -е. Количество устойчивых состояний называется коэффициентом пересчета счетчика (М= 2ⁿ).

По назначению счетчики подразделяются на: простые и реверсивные.

Простые счетчики- счетчики, работающие только на сложение или вычитание.

Реверсивный счетчик может работать и на сложение и на вычитание.

Суммирующий счетчик предназначен для выполнения счета в прямом направление, т.е. с приходом очередного сигнала показатель счетчика увеличивается на 1. Вычитающий счетчик предназначен для счета в обратном направлении, т.е. с приходом новогосигнала счетчик уменьшается на 1 .

По способу организации счета счетчики бывают: асинхронные или синхронные.

По способу организации цепей переноса между разрядами счетчика счетчики бывают: последовательные, параллельные и частичнопараллельные.

Видно, что триггер младшего разряда переключается каждым счетным импульсом, т.е. входом счетчика служит вход этого триггера. Состояния второго и третьего триггеров меняются соответственно каждым вторым и четвертым импульсом. Это обеспечивается последовательным соединением триггеров.

Из правила прибавления к двоичному числу единицы также известно, что изменение значения i-го разряда происходит тогда, когда до прибавления очередной единицы все предыдущие разряды были единицами. Отсюда следует правило: если триггеры имеют прямой счетный вход, то он подключается к инверсному выходу предыдущего триггера; если имеет инверсный вход, то он подключается к прямому выходу.

Иллюстрирующий пример трехразрядного суммирующего счетчика с временными диаграммами работы и условным изображением приведен на рис. 13.27. Счетчик может принимать 8 различных состояний, которые повторяются через каждые 8 входных импульсов (Kn=8). С наибольшей частотой переключается триггер младшего разряда, следовательно, разрешающая способность счетчика определяется временем задержки переключение триггера (Тст=Ттг). Это положение распространяется на все типы двоичных счетчиков.

При подаче на вход вычитающего счетчика одного счетного импульса ранее записанное в нем число уменьшается на единицу.

Принципы построения вычитающих счетчиков основаны на правилах вычитания двоичных чисел и отличаются от принципов построения суммирующих счетчиков лишь тем, что если триггеры имеют прямой вход +1, то его подключают к прямому выходу предыдущего триггера, если вход инверсный, то подключают к инверсному выходу.

На рис. 13.28 приведен пример, аналогичный рис. 13.27. Здесь дополнительный вход S позволяет предварительно устанавливать все триггеры в единичное состояние.

1.7. СИНХРОННІ ЛІЧИЛЬНИКИ: ОСОБЛИВОСТІ СХЕМОТЕХНІЧНОЇ РЕАЛІЗАЦІЇ ТА ФУНКЦІОНУВАННЯ.

У синхронных счетчиков все разрядные триггеры синхронизируются параллельно одними и теми же синхроимпульсами, поступающими из источника этих импульсов. синхронные счетчики иногда - параллельными.

Синхронные счетчики, в свою очередь, подразделяются на параллельно-синхронные и последовательно-синхронные. Параллельные счетчики имеют более высокую скорость счета, чем асинхронные.

Синхронный последовательный счетчик. По способу подачи синхроимпульсов такие счетчики параллельные, т.е. синхроимпульсы поступают на все триггеры счетчика параллельно, а по способу управления (подачи управляющих импульсов) - последовательные.

Синхронный последовательный счетчик обладает повышенным быстродействием, однако, за счет последовательного формирования управляющих уровней, на входы “J” и “К” счетных триггеров, быстродействие несколько уменьшается. От этого недостатка лишены параллельные синхронные счетчики, в которых формирование управляющих уровней и их подача на соответствующие входы триггеров счетчика осуществляется одновременно, т.е. параллельно.

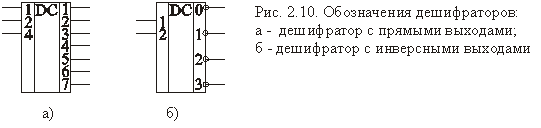

1.8. ДЕШИФРАТОРИ: ВИЗНАЧЕННЯ, КЛАСИФІКАЦІЯ, СПОСОБИ ПОБУДОВИ ТА ФУНКЦІОНУВАННЯ. ЛИНЕЙНЫЙ ИЛИ ОДНОСТУПЕНЧАТЫЙ ДЕШИФРАТОР.

Дешифратор - это комбинационное устройство, предназначенное для преобразования параллельного двоичного кода в унитарный, т.е. позиционный код. Обычно, указанный в схеме номер вывода дешифратора соответствует десятичному эквиваленту двоичного кода, подаваемого на вход дешифратора в качестве входных переменных, вернее сказать, что при подаче на вход устройства параллельного двоичного кода на выходе дешифратора появится сигнал на том выходе, номер которого соответствует десятичному эквиваленту двоичного кода. Отсюда следует то, что в любой момент времени выходной сигнал будет иметь место только на одном выходе дешифратора. В зависимости от типа дешифратора, этот сигнал может иметь как уровень логической единицы (при этом на всех остальных выходах уровень логического 0), так и уровень логического 0 (при этом на всех остальных выходах уровень логической 1). В дешифраторах каждой выходной функции соответствует только один минтерм, а количество функций определяется количеством разрядов двоичного числа. Если дешифратор реализует все минтермы входных переменных, то он называется полным дешифратором (в качестве примера неполного дешифратора можно привести дешифратор двоично-десятичных чисел). Рассмотрим пример синтеза дешифратора (полного) 3 ® 8, следовательно, количество разрядов двоичного числа - 3, количество выходов - 8.( Рис 2.9)

Таблица состояний дешифратора

-

Х3 Х2Х1

Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

1 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0

0 0 1 0 0 0 0 0

0 0 0 1 0 0 0 0

0 0 0 0 1 0 0 0

0 0 0 0 0 1 0 0

0 0 0 0 0 0 1 0

0 0 0 0 0 0 0 1

Как следует из таблицы состояния, каждой функции соответствует только один минтерм.

Из полученных уравнений и схемы дешифратора следует, что для реализации полного дешифратора на m входов (переменных) потребуются n = 2m элементов конъюнкции (количество входов каждого элемента “И” равно m)и m элементов отрицания.

1.9 ШИФРАТОРИ. ВИЗНАЧЕННЯ, ПРИНЦИПИ ПОБУДОВИ ТА ОСОБЛИВОСТІ ФУНКЦІОНУВАННЯ. КЛАВІАТУРНІ, ПРІОРИТЕТНІ ШИФРАТОРИ, КОДОПЕРЕТВОРЮВАЧІ.

Шифратор - это логическое устройство, выполняющее преобразование позиционного кода в n разрядный двоичный код. Таким образом, шифратор - это комбинационное устройство, реализующее обратную дешифратору функцию.

Пример шифратора для трех переменных.

Таблица состояния шифратора:

Схема шифратора семиразрядного позиционного кода в трехразрядный двоичный код приведена на рис. 2.12.

1.10. МУЛЬТИПЛЕКСОРИ: ВИЗНАЧЕННЯ, ПРИНЦИПИ ПОБУДОВИ ТА ФУНКЦІОНУВАННЯ.

Мультиплексор - коммутатор цифровых сигналов. Мультиплексор представляет собой комбинационное устройство с m информационными, n управляющими входами и одним выходом. Функционально мультиплексор состоит из m элементов конъюнкции, выходы которых объединены дизъюнктивно с помощью элемента ИЛИ с m входами. На одни входы всех элементов конъюнкции подаются информационные сигналы, а другие входы этих элементов соединены с соответствующими выходами дешифратора с n входами.

Функциональная схема мультиплексора приведена на рис.2.13.

Из рис. 2.13. следует, что мультиплексор содержит дешифратор на соответствующее число выходов (число выходов дешифратора определяется числом информационных входов мультиплексора), элементы конъюнкции на два или на три входа каждый и элемент дизъюнкции с числом входов, равным количеству информационных линий D0 . . . Dm. Число входов элементов И может быть равным только двум, однако, во многих случаях возникает необходимость стробирования выходного сигнала мультиплексора импульсами независимого источника. В таких случаях в структуре мультиплексора используются элементы И с тремя входами. Одни из входов всех элементов конъюнкции, в последнем случае, объединяются, и по этой линии подается сигнал разрешения работы мультиплексора (стробирующий сигнал). Наличие дополнительного управляющего входа расширяет функциональные возможности мультиплексора и позволяет проще реализовать методы борьбы с гонками.

На рис. 2.14 показано обозначение мультиплексора на принципиальных и функциональных электрических схемах.

Из уравнения мультиплексора видно, что на его выход будет передаваться сигнал только с одного входа, номер которого совпадает с числом, соответствующим кодовой комбинации Х1 и Х2. Если Х1=Х2=0, на выход мультиплексора будет передаваться сигнал с входа D0. Когда на адресных (управляющих) входах Х1=1 и Х2=0, то на выход будет передаваться сигнал с входа D1 и т.д.

На базе мультиплексоров можно построить различные комбинационные устройства с минимальным числом дополнительных элементов логики. Следует отметить, что мультиплексоры хотя, и предназначены для коммутации цифровых сигналов, но с помощью мультиплексоров, изготовленных по КМОП технологии, можно коммутировать и аналоговые сигналы.

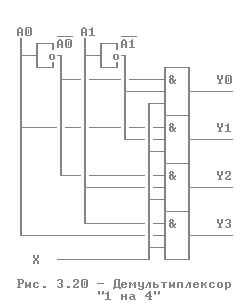

1.11. ДЕМУЛЬТИПЛЕКСОРИ: ВИЗНАЧЕННЯ, ПРИНЦИПИ ПОБУДОВИ ТА ФУНКЦІОНУВАННЯ.

Демультиплексор – єто обратное Мультиплексору (вопрос 1.10)

В цифровых устройствах часто возникает

задача передачи цифровой информации

от "m" различных устройств к "n"

приемникам через канал общего

пользования. Для этого на входе канала

устанавливается устройство, называемое

МУЛЬТИПЛЕКСОРОМ, которое согласно

коду адреса A m подключает к каналу один из источников

информации, а на выходе канала устройство

ДЕМУЛЬТИПЛЕКСОР обеспечивает передачу

информации к приемнику, имеющему

цифровой адрес A n

подключает к каналу один из источников

информации, а на выходе канала устройство

ДЕМУЛЬТИПЛЕКСОР обеспечивает передачу

информации к приемнику, имеющему

цифровой адрес A n

╔═════╦════════╦═══════════════╗

║Вход ║ Адрес ║ Выходы ║

║─────║────────║───────────────║

║ X ║ A1 A0 ║Y3 Y2 Y1 Y0 ║

╠═════╬════════╬═══════════════╣

║ 0 ║ 0 0 ║ 0 0 0 0 ║

║ 1 ║ 0 0 ║ 0 0 0 1 ║

║─────║────────║───────────────║

║ 0 ║ 0 1 ║ 0 0 0 0 ║

║ 1 ║ 0 1 ║ 0 0 1 0 ║

║─────║────────║───────────────║

║ 0 ║ 1 0 ║ 0 0 0 0 ║

║ 1 ║ 1 0 ║ 0 1 0 0 ║

║─────║────────║───────────────║

║ 0 ║ 1 1 ║ 0 0 0 0 ║

║ 1 ║ 1 1 ║ 1 0 0 0 ║

╚═════╩════════╩═══════════════╝

Логика функционирования демультиплексора для случая n = 4 иллюстрируется таблицей 3.6, в которой Y0...Y3 - сигналы, подаваемые на входы приемников информации.

1.12. СУМАТОРИ КОМБІНАЦІЙНОГО ТИПУ: ПРИЗНАЧЕННЯ, КЛАСИФІКАЦІЯ ТА ПРИНЦИПИ ПОБУДОВИ.

Сумматор - это ЛКС (рис. 3.8), формирующая сигналы суммы (S) и переноса (Р) при сложении двух двоичных чисел (А, В) и сигнала переноса соседнего младшего разряда (С) по правилам двоичной арифметики (см. таблицу 3.3).

┌──┬───┬──┐

────┤А │SM │ S├────

────┤В │ │ │

├──┤ │ │

────┤С │ │ P├────

└──┴───┴──┘

Рис. 3.8 - Одноразрядный сумматор

Таблица 3.3 -Таблица состояний одноразрядного сумматора

A │ B │ C ║ P │ S

────┼───┼────╫────┼───

0 │ 0 │ 0 ║ 0 │ 0

0 │ 0 │ 1 ║ 0 │ 1

0 │ 1 │ 0 ║ 0 │ 1

0 │ 1 │ 1 ║ 1 │ 0

1 │ 0 │ 0 ║ 0 │ 1

1 │ 0 │ 1 ║ 1 │ 0

1 │ 1 │ 0 ║ 1 │ 0

1 │ 1 │ 1 ║ 1 │ 1

Принципиальная схема одноразрядного сумматора, реализованная на элементах "И-ИЛИ-НЕ", приведена на рис. 3.10.

Более простая схема сумматора может быть реализована с учетом соотношения : сигнал суммы (S) равен единице, если только один входной сигнал (А, В, С) равен единице и отсутствует перенос (Р) или все три входных сигнала равны единице :

_ _ _

S = A P + B P + C P + A B C (3.7)

Упрощенная схема одноразрядного сумматора, реализующая функцию (3.7), приведена на рис. 3.11. В этой схеме время задержки распространения сигнала суммы (S) больше, чем время задержки сигнала переполнения (Р).

Логический элемент "И-ИЛИ-НЕ" имеется в наборе любой серии ТТЛ и ТТЛШ (см. рис. 2.16). Для КМОП элементов эти схемы сумматоров легко реализуются в базисе "И-НЕ".

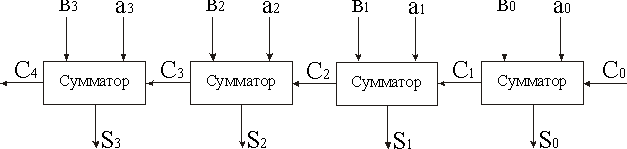

На основе одноразрядного сумматора реализуются схемы многоразрядных сумматоров. На рис. 3.12 приведена схема четырехразрядного сумматора (аналогично можно реализовать сумматор на 8 или 16 разрядов). На входы А1..А4 подается первое слагаемое (младший разряд - А1), на входы В1..В4 - второе. Вход переноса (С) младшего разряда подключен к нулевому логическому уровню (к общей шине).Четыре разряда суммы формируются на выходах S1..S4, пятый разряд суммы - на выходе Р4.

В формировании сигналов S4, P4 участвуют все входные переменные А1..А4, В1..В4. Но ко входам последней логической схемы эти сигналы проходят через разное количество элементов, что вызывает появление на выходах ложных коротких импульсов, образованных эффектом гонок (состязаний).

Многоразрядный сумматор с последовательным переносом. Таким образом, в общем случае для каждого разряда необходима логическая схема с тремя входами ai, bi, Ci и двумя выходами Si, Ci+1. Такая схема и есть полный сумматор. Ее можно реализовать с помощью двух полусумматоров.

|

Входы |

Промежуточные величины |

Выходы |

|||||

|

ai |

bi |

сi |

Pi |

gi |

ri |

Si |

Ci+1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один полный сумматор. Только в младшем разряде можно обойтись полусумматором. На рис. 2.23 приведена схема, предназначенная для сложения двух четырехразрядных чисел А и В. Эта схема выпускается в интегральном исполнении. В ее младшем разряде также используется полный сумматор, чтобы иметь возможность наращивания разрядности схемы.

Рис. 2.23. Сумматор с последовательным переносом

Сумматоры с параллельным переносом. Время выполнения операции в сумматоре с параллельным переносом намного больше времени сложения в одноразрядном сумматоре. Действительно, сигнал переноса С4 только тогда может принять истинное значение, когда будет установлено правильное значение С3. Такой порядок выполнения операций называется последовательным переносом (Ripple Carry).

Чтобы уменьшить время операции сложения многоразрядных чисел можно использовать схемы параллельного переноса (Carry look-ahead). При этом все сигналы переноса вычисляются непосредственно по значениям входных переменных.

Согласно таблице переключений, в общем случае для сигнала переноса любого i-го разряда справедливо соотношение:

![]() . (1)

. (1)

Величины gi, ri вычисляются в качестве промежуточных результатов и в полном сумматоре. Следовательно, их получение не требует дополнительных затрат. Смысл этих величин объясняется совсем просто. Сигнал gi вырабатывается тогда, когда в данном разряде перенос происходит из-за комбинации входных переменных ai,bi. Поэтому его называют функцией генерации переноса. Сигнал Pi показывает, передается ли полученный в младшем разряде сигнал переноса Ci дальше. Поэтому он называется функцией распространения переноса.

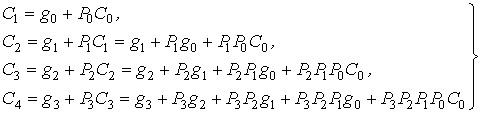

Пользуясь выражением (1), можно вывести следующие формулы для вычисления сигналов переноса:

(2)

(2)

Очевидно, что хотя полученные выражения достаточно сложные, время формирования сигнала переноса в любой разрад с помощью вспомогательных функций определяется только времением здержки распространения сигнала на двух элементах. Эти функции реализуются специальным комбинационным устройством – схемой ускоренного переноса.

Схема сумматора с параллельным переносом приведена на рис. 2.24, а. На рис. 2.24, б изображена схема устройства параллельного переноса в группе из четырех разрядов. Эта схема реализует систему уравнений (2).

Рис. 2.24. Схема сумматора с параллельным переносом

1.13. НАКОПИЧУЮЧІ СУМАТОРИ ТА ОСОБЛИВОСТІ ЇХНЬОГО ФУНКЦІОНУВАННЯ.

Накапливающий сумматор (НС) обычно представляет собой совокупность сумматора комбинационного типа и регистра (который хранит результаты суммирования как текущие, так и окончательные). Работает такой сумматор по формуле Si = Si-1 + A, ( формула 1.1) где

Si –текущая сумма,

Si-1 –предыдущая(на предыдущем цикле суммирования),

А – очередное текущее слагаемое.

Результат замещает старое значение суммы. Очередное прибавление слагаемого тактируется синхроимпульсами. Учитывая такие особенности функцио-нирования накапливающие сумматоры называются иногда аккумуляторами. На схемах сумматоры обозначаются SM. В российских сериях интегральных микросхем(ИМС), соответственно – ИР(например-К155ИМ3). В американских

сериях они отдельно не обозначаются: SN40S08N. Интегральные микросхемы содержат,как правило, четырехразрядные комбинационные сумматоры. Чаще всего применяют четырехразрядные сумматоры комбинационного типа. Помимо выходных разрядов суммы и выхода переноса в сумматорах предусмотрен вход расширения С для обьединения сумматоров с целью повышения разрядности.

Многоразрядные сумматоры можно построить, прибегнув к обьединению синхронизирующих входов, а также соединению соответствующих входов и выходов переноса нескольких базовых сумматоров.

Эти сумматоры являются ядром арифметико-логических устройств(АЛУ) , без которых, в свою очередь, не было бы процессоров. По сути, эти устройства является интегральными микросхемами, без которых не обходится ни один компьютер в целом, ни сколько-нибудь сложное цифровое устройство, где необходимо выполнять арифметичесие операции.

Накапливающие сумматоры применяются также, например, для формирования адреса ОЗУ, в генераторах сигналов произвольной формы.

На основании формулы 1.1, описывающе по сути алгоритм работы НС можно предложить структурную схему, приведенную на рис 1.1. Схема работает следующим образом: Перед началом суммирования регистр устанавливается в нулевое состояние по входу R. После поступления слов в сумматор происходит обработка результата, то есть проверяется перенос и происходит собственно суммирование. С выходов сумматора результат суммы поступает на регистр (РГ), который служит для хранения информации и задержки сигнала на один такт. Естественно, сигналы через него будут проходить в том случае, если открыт вход синхронизации. Затем с выходов регистра сигналы поступают в качестве второго слагаемого(20-ти разрядного) на сумматор. Такой цикл повторяется до тех пор, пока не прекратится подача последовательности кодов либо сумма не превысит разрядность 20 (в этом случае сумматор сбрасывается в 0.

1.14 МОДЕЛЮВАННЯ АНАЛОГОВИХ ТА ЦИФРОВИХ СХЕМ ЗА ДОПОМОГОЮ ПАКЕТІВ EWB і MICRO-CAP: ПОСЛІДОВНІСТЬ ДІЙ ПРИ МОДЕЛЮВАННІ. ОДЕРЖАННЯ ТА ОФОРМЛЕННЯ РЕЗУЛЬТАТІВ.

Программно-прикладной пакет (ППП) EWB (цифровая часть) предназначен для разработки схем цифровых устройств на цифровых элементах и анализа их работы в динамике и статике с возможностью

моделирования различных режимов работы. Пакет позволяет получать

несколько вариантов реализации схемных решений при разработке одного и того же цифрового устройства, что позволяет выбрать оптимальный алгоритм работы.

В программно-прикладном пакете (далее - ППП) «Electronics

WorkBench 3.0E» (далее - EWB) пользователю предоставлена возможность использовать в своей работе 7 приборов (Мультиметр, Генератор Слов, Логический Анализатор, Логический преобразователь).

Краткое описание этих приборов и работа с ними.

Мультиметр

Мультиметр прост в обращении и удобен в эксплуатации. Мультиметр способен измерять любые электрические параметры при постоянном и переменном токе, как то напряжение, ток, сопротивление и децибелы. На панели мультиметра имеются 2 рабочих входа + и - , кнопки переключения режима работы по току и кнопки рода работы.

Генератор слов

Генератор слов (ГС) используется для генерации сигналов, который могут являться входными сигналами схемы. ГС может генерировать 8 слов (16 бит одновременно). Он имеет 8 информационных выводов, при этом номер вывода соответствует номеру слова на экране ГС. ГС также генерирует импульсы синхронизации (вывод CLOCK

«CLK»). ГС имеет один вход TRIGGER - это так называемый вход

внешнего запуска.

Логический анализатор

16-канальный ЛА отображает поступающую на его входы последовательность сигналов в виде последовательности прямоугольных им

пульсов. ЛА также показывает двоичные и шестнадцатеричные значения этих сигналов.

Логический преобразователь

Логический преобразователь (ЛП) - это мощное устройство, которое выполняет различные функции конвертирования. Пользователю

доступны следующие преобразования:

преобразование схемы в таблицу истинности;

-

преобразование таблицы истинности в логическое выражение;

-

упрощение логического выражения;

-

преобразование логического выражения в таблицу истинности;

-

преобразование логического выражения в схему;

-

преобразование логического выражения в схему в базисе И-НЕ.

Осциллограф.

Двухканальный осциллограф показывает изменение амплитуды и частоты электрического сигнала. Он позволяет одновременно следить за одним или двумя сигналами, а также позволяет получать график сравнения двух различных сигналов.

Для того чтобы подсоединить осциллограф к схеме, надо поместить соединитель в точку схемы , откуда вы хотите снимать сигнал. После чего заведите проводник из соединителя на канал осциллографа. Терминал осциллографа “GROUND” необходимо заземлить. Для отслеживания работы электрической схемы достаточно одного осциллографа, изменение точек подключения каналов осциллографа не требует перезапуска и его можно производить непосредственно в работающей схеме.

Разработка схем цифровых устройств

5.1. Вывод элементов схем на рабочую поверхность

Для того, чтобы переместить элемент на рабочую поверхность,

нужно подвести указатель «мыши» к изображению выбранного элемента, нажать клавишу «мышки» и, не отпуская ее, переместить элемент в нужное место схемы.

-

Монтаж схем

Д

нравится как пакет провёл проводник, вы можете самостоятельно переместить проводник на схеме в рабочей области пользователя. При необходимости соединения двух или нескольких проводников в один можно воспользоваться той же технологией что и при соединении элементов схемы, но следует помнить, что при попытке соединить более четырёх проводников в одной точке, связь с каким либо проводником уже подключённым будут утеряны. Что бы этого не случилось, необходимо создать соединение ( Connector ), на каком либо из соединённых проводников

МОДЕЛИРОВАНИЕ РАБОТЫ СХЕМЫ

6.1. Запуск схем

Запуск схемы осуществляется тремя способами:

первый способ заключается в нажатии кнопки запуска схемы

на

исполнение, расположенной в верхнем

правом углу окна;![]()

второй способ заключается в нажатии комбинации «горячих

клавиш» CRL+G;

третий способ состоит в выборе опции Activate пункта меню Analysis;

6.2. Ошибки в исключительных ситуациях

При моделировании работы схемы возможно два вида ошибок, которые определяются автоматически. Это Race Conditions (гонки).

Вторая возможная детектируемая ошибка - это Contradictions, т.е.

некорректное подключение проводов.

6.3. Приостановка и возобновление моделирования

Для временного останова моделирования работы схемы можно использовать два способа:

нажать клавишу F9;

выбрать в меню Analysis опцию Pause.

6.4. Остановка моделирования

Для останова моделирования работы схемы можно использовать

два способа:

нажать комбинацию «горячих клавиш» CTRL+T;

нажать кнопку запуска схемы

на

исполнение, расположенной в верхнем

правом углу окна![]() ;

;

выбрать в меню Analysis опцию Stop.

1.15 ОСОБЛИВОСТІ ТА ПРИНЦИПИ ПОБУДОВИ ПРИСТРОЇВ З ВИКОРИСТАННЯМ «ЖОРСТКОЇ» та «ПРОГРАМОВАНОЇ» ЛОГІКИ.

Существует два принципиально разных подхода к проектированию цифровых устройств: использование принципа схемной логики или использование принципа программируемой логики.

В первом случае в процессе проектирования подбирается некоторый набор цифровых микросхем (обычно малой и средней степени интеграции) и определяется такая схема соединения их выводов, которая обеспечивает требуемое функционирование (т.е. функционирование устройства определяется тем, какие выбраны микросхемы и по какой схеме выполнено соединение их выводов). Устройства, построенные на таком принципе системной логики, способны обеспечивать наивысшее быстродействие при заданном типе технологии элементов. Недостаток этого принципа построения МКУ состоит в невозможности "перестройки" структуры устройств и систем при необходимости изменения или расширения их функциональных возможностей.

Эти обстоятельства заставляют обратиться к другому подходу в проектировании цифровых устройств, основанному на использовании принципа программируемой логики. Этот подход предполагает построение с использованием одной или нескольких БИС некоторого универсального устройства, в котором требуемое функционирование (т.е. их специализация) обеспечивается занесением в память устройства определенной программы (или микропрограммы). В зависимости от введенной программы такое универсальное управляющее устройство способно обеспечивать требуемое управление операционным устройством при решении самых различных задач. В этом случае число типов БИС, необходимых для построения управляющего устройства, небольшое, а потребность в БИС каждого типа высока. Это обеспечивает целесообразность их выпуска промышленностью.

Следует иметь ввиду, что наивысшее быстродействие достигается в процессорах, в которых управляющее устройство строится с использованием системной логики, а операционное устройство выполняется в виде устройства, специализированного для решения конкретной задачи.

Если в устройстве, построенном на принципе системной логики, всякое изменение или расширение выполняемых функций влечет за собой демонтаж устройства и монтаж устройства по новой схеме, то в случае МКУ благодаря использованию принципа программируемой логики такое изменение достигается заменой хранящегося в памяти программы новой программой, соответсвующей новым выполняемым устройством функциям. Такая гибкость применений вместе с другими связанными с использованием БИС достоинствами (низкой стоимостью, малыми габаритами), а также высокая точность помехозащищенность, характерные для цифровых методов, обусловили бурное внедрение МКУ в различные сферы производства, научные исследования и бытовую технику.

Микроконтроллерные и микропроцессорные устройства в свою очередь обеспечили широкое использование цифровых методов в различных технических применениях, и размах внедрения этих новых методов рассматривается как революция в технике.

Дуализм "программные средства - аппаратура"

Проектирование МКС производится на базе определенных ОМК. Разработчикам аппаратуры на основе ОМК недоступен уровень отдельных транзисторов, связей между ними. Микроконтроллер воспринимается как нечто цельное, имеющее различные свойства, заложенные в его архитектуре.

Архитектура микроконтроллера - это его логическая организация, определяемая возможностями МК по аппаратурной или программной реализации функций, возлагаемых на проектируемые МКУ. Архитектура отражает структуру МК, способы представления и форматы данных, набор операций, форматы управляющих слов, способы обращения ко всем доступным для пользователя элементам структуры, реакцию МК на внешние сигналы.

При разработке МКС необходимо определить, какая часть функций при создании конкретных МКС должна быть реализована программным способом, а какая - с помощью дополнительных аппаратных средств. Поэтому при проектировании МКС необходимо:

-

дать описание концептуальной модели функционального поведения МКС и рекомендации по организации вычислительного процесса в микроконтроллерной аппаратуре;

-

определить структуру и особенности построения программных средств;

-

описать характеристики внутренней организации потоков данных и управляющей информации;

4) провести анализ функциональной структуры и особенности физической реализации устройств МКС с позиций сбалансированности программных и аппаратных средств.

При разработке архитектуры МКУ определяют форматы данных, обосновывают требования к интерфейсам. Правильный выбор архитек-туры дает возможность оптимизировать вычислительный процесс реа-лизации алгоритмов функционирования МКУ на выбранных аппаратурных средствах. В МКУ процесс оптимизации начинается с решения компро-миса "программные средства - аппаратура", который заключается в том, что в МКУ любое функциональное преобразование может быть осуществлено как программным путём

1.16 ОСНОВНІ ФУНКЦІЇ АЛГЕБРИ ЛОГІКИ ТА ЛОГІЧНІ ЕЛЕМЕНТИ ДЛЯ ЇХ РЕАЛІЗАЦІЇ. Закони АЛГЕБРИ ЛОГІКИ.

Алгебра логики (АЛ) является основным инструментом синтеза и анализа дискретных автоматов всех уровней. АЛ называют также Булевой алгеброй. АЛ базируется на трёх функциях, определяющих три основные логические операции.

1. Функция отрицания (НЕ). f1 =`X читается, как f1 есть (эквивалентна) НЕ Х. Элемент, реализующий функцию НЕ, называется элементом НЕ (инвертором).

Элемент НЕ имеет два состояния.

2. Функция логического умножения (конъюнкции). Функция логического умножения записывается в виде f2=X1·X2. Символы логического умножения &, L, <×>, ´. Функция конъюнкции читается так: f2 есть (эквивалентна) Х1 и Х2, поскольку функция истинна тогда, когда истинны 1-й и 2-й аргументы (переменные). Конъюнкцию называют функцией И, элемент, реализующий эту функцию, элементом И.

В общем случае функцию логического умножения от n переменных записывают так:

Количество переменных (аргументов), участвующих в одной конъюнкции, соответствует количеству входов элемента И.

3. Логическое сложение (дизъюнкция). Функция логического сложения записывается в виде f3=X1 + X2, и читается так: f3 есть Х1 или Х2, поскольку функция истинна, когда истинна одна или другая переменная (хотя бы одна). Поэтому функцию дизъюнкции часто называют функцией ИЛИ. Символы логического сложения +,V.

В общем случае функция ИЛИ записывается:

Используя операции (функции) И, ИЛИ, НЕ можно описать поведение любого комбинационного устройства, задав сколь угодно сложное булево выражение. Любое булево выражение состоит из булевых констант и переменных, связанных операциями И, ИЛИ, НЕ.

Пример булева выражения:

![]() .

.

Основные законы алгебры логики. Основные законы АЛ позволяют проводить эквивалентные преобразования функций, записанных с помощью операций И, ИЛИ, НЕ, приводить их к удобному для дальнейшего использования виду и упрощать запись.

ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ Таблица 1.1

|

N |

а |

б |

Примечание |

|

1 2 3 4 5 |

X+0=X X+1=1 X+X=X X+

|

X*1=X X*0=0 X*X=X X*

|

Аксиомы (тождества) |

|

6 |

|

|

Закон двойного отрицания |

|

7 |

X+Y=Y+X |

X*Y=Y*X |

Закон коммутативности |

|

8 |

X+X*Y=X |

X

|

Закон поглощения |

|

9 |

|

|

Правило де-Моргана (закон дуальности) |

|

10 |

|

|

Закон ассоциативности |

|

11 |

X+Y*Z=

|

|

Закон дистрибутивности |

Булевой алгебре свойственен принцип двойственности, что наглядно иллюстрирован в табл. 1.1. Как следует из табл. 1.1, только закон двойного отрицания не подчиняется этому принципу.

Используя законы алгебры логики, можно упростить булевы выражения, в частности, правило склеивания позволяет упростить выражение типа

![]() .

.

Действительно, используя законы 2, 5 и 11 можно записать исходное выражение в виде Х2(Х1 +`Х1 ) =Х2. Так как логическая операция Х1 +`Х1 = 1 (см. з-н 5), а Х2×1 = Х2 (см. з-н 2б), полученное выражение истинно.

Элементарные функции алгебры-логики. Среди всех функций алгебры логики особое место занимают функции одной и двух переменных, называемые элементарными. В качестве логических операций над переменными, эти функции позволяют реализовать различные функции от любого числа переменных.

Общее количество функций АЛ от m переменных R=2k, где k=2m. Рассмотрим элементарные функции от двух переменных

|

Переменные и их состояния |

Обозначение функции |

Назначение Функции |

||||

|

X1 X2 |

0 0 |

0 1 |

1 0 |

1 1 |

||

|

f0 |

0 |

0 |

0 |

0 |

f0=0 |

Генератор 0 |

|

f1 |

0 |

0 |

0 |

1 |

f1=X1·X2 |

«И» |

|

f2 |

0 |

0 |

1 |

0 |

f2=X1·

|

|

|

f3 |

0 |

0 |

1 |

1 |

f3=X1 |

|

|

f4 |

0 |

1 |

0 |

0 |

f4=

|

|

|

f5 |

0 |

1 |

0 |

1 |

f5=X2 |

|

|

f6 |

0 |

1 |

1 |

0 |

f6=X1

|

Сумматор по модулю два |

|

f7 |

0 |

1 |

1 |

1 |

f7=X1+X2 |

«ИЛИ» |

|

f8 |

1 |

0 |

0 |

0 |

f8=

|

«ИЛИ-НЕ» |

|

f9 |

1 |

0 |

0 |

1 |

f9=X1~X2 |

Функция равнозначности |

|

f10 |

1 |

0 |

1 |

0 |

f10=

|

«НЕ» Х2 |

|

f11 |

1 |

0 |

1 |

1 |

f11=X1+

|

|

|

f12 |

1 |

1 |

0 |

0 |

f12=

|

«НЕ» Х1 |

|

f13 |

1 |

1 |

0 |

1 |

f13=

|

|

|

14 |

1 |

1 |

1 |

0 |

f14=

|

«И-НЕ» |

|

f15 |

1 |

1 |

1 |

1 |

f15=1 |

Генератор 1 |

1.17 СИНТЕЗ ЛОГІЧНИХ СХЕМ В БАЗИСАХ (І, АБО, НІ), І-НІ, АБО-НІ.

В задачу синтеза комбинационных устройств входит построение схемы устройства по заданным условиям его работы и при заданном базисе элементов. Задание комбинационного устройства сводится к заданию тех функций, которые оно должно реализовать. Число функций определяется числом выходов комбинационного устройства.

Процесс синтеза комбинационных устройств состоит из 2-х этапов.

1. Абстрактный синтез

Абстрактный синтез включает:

-

формирование задачи, словесное описание функций устройства, определение типа устройства;

-

описание устройства на формализованных языках:таблица истинности,карта Карно,аналитическое выражение и т.д.;

-

минимизация булевых функций;

-

построение логической схемы устройства.

2. Схемный синтез

-

переход в требуемый базис;

-

построение принципиальной схемы;

-

разработка монтажной схемы;

-

изготовление устройства и его испытания.

В результате испытаний осуществляются корректировка схемы и подготовка технической документации.

Полная система логических функций. Понятие о базисе

Функционально полная система логических функций представляет собой набор логических функций, с помощью которых можно записать любую, сколь угодно сложную функцию. В этом случае говорят, что этот набор образует базис. Функционально полными являются 3 базиса:

1) "И-ИЛИ-НЕ" (базис конъюнкции, дизъюнкции, инверсии)

2) "И-НЕ" (базис Шеффера)

3) "ИЛИ-НЕ" (базис Пирса или функция Вебба).

Элементы, реализующие операцию "И-НЕ", “ИЛИ-НЕ” и “Исключающее ИЛИ” на принципиальных и структурных схемах изображаются так:

Примеры реализации логических операций в базисах “И-НЕ” и “ИЛИ-НЕ”.

Реализация операции “НЕ”:

Реализация операции “И”:

Реализация операции “ИЛИ”:

Пример реализации комбинационного устройства в базисе "И-НЕ". Пусть задана функция, реализуемая комбинационным устройством, в аналитической форме

![]() .

.

Используя закон де Моргана и с учетом закона двойного инвертирования, запишем эту функцию в виде

![]() .

.

Как следует из полученного аналитического

выражения, логическое устройство должно

содержать три двухвходовых и один

трехвходовой элемент И-НЕ. Функциональная

схема комбинационного устройства,

построенная в базисе И-НЕ, показана на

рис.

1.18 ТИПИ ДАНИХ ТА СТРУКТУРИ КОМАНД В МП INTEL (НА ПРИКЛАДI 486)

Рассмотрим данные, их форматы и представление а памяти, с которыми работает МП 80486. Большинство из содержания данного раздела относится ко всем современным процессорам.

Базовой единицей данных является байт. Физический адрес, выдаваемый процессором на внешнюю шину адреса , является адресом (порядковым номером) байта в адресуемом пространстве памяти. Ширина шины адреса (число линий, число разрядов адреса) n определяет максимальное адресное пространство N=2^n. Адрес байта изменяется от 0 до N-1. МП 80486 имеет адресное пространство: n=32, N=2^32 = 4Gбайта.

При ширине шины данных n=32 за одно обращение к памяти передается до 4 байт. Кроме значения данных длинной в байт используются данные длинной 2 байта - слово и 4 байта- двойное слово. В больших машинах (mainframe) под словом понимается длина разрядов аппаратной реализации основных регистров или ширина шины данных. Применительно к МП 80486 его слово состояло бы из 4 байт. Информация в памяти располагается так: младшие разряды в младшем байте - в байте с меньшим адресом, старшие разряды в последующих байтах - в байтах с большими адресами.

МП 80486 имеет команды, длина которых меняется от 1 байта до 15 байтов. Команды содержат всю необходимую информацию для выполнения требуемой операции с заданными операндами. Операнды могут быть размером в бат, слово или двойное слово.

Необязательная часть Обязательная часть

Префиксы

┌───────────────────────┐ ┌────────────────────────────────────┐

│ Число байт │ │ Число байт │

├─────┬─────┬─────┬─────┤ ├──────┬──────┬──────┬───────┬───────┤

│ 0,1 │ 0,1 │ 0,1 │ 0,1 │ │ 1,2 │ 0,1 │ 0,1 │0,1,2,4│0,1,2.4│

├─────┴─────┴─────┴─────┤ ├──────┴──────┴──────┴───────┴───────┤

│ Назначение │ │ Назначение │

╠═════╦═════╦═════╦═════╣ ╠══════╦══════╦══════╦═══════╦═══════╣

║ Пов-║Раз- ║ Раз-║Заме-║ ║ Код ║ ║ ║Смеще -║Непос- ║

║ тор ║ мер ║ мер ║ на ║ ║опера-║ mod ║ sib ║ние (в ║редств.║

║ ║адре-║опе- ║сег- ║ ║ ции ║ ║ ║коман- ║операнд║

║ ║ са ║ранда║мента║ ║ ║ r/m ║ ║ де ║ ║

║REP ║ OS ║ AS ║ S ║ ║ ║ ║ ║ ║ ║

╚═════╩═════╩═════╩═════╝ ╞══════╪══════╪══════╪═══════╩═══════╝

┌────────────────────────┘ │ │ │

│ ┌─────────┘ └───┬┐ └───────────────┐

├───────────────┬──┬──┼─────┬────────┬─────┤├───┬──────┬──────┤

│ Код операции │d │w │ mod │ reg/kon│ r/m ││SS │index │ base │

└───────────────┴──┴──┴─────┴────────┴─────┘└───┴──────┴──────┘

7 2 1 0 7 6 5 3 2 0 7 6 5 4 3 2 1 0

Поле Длина (бит) Назначение

Префиксы

REP Повторение (REPeate), применяется в цепочечных

командах

OS Operand Size -переключает 16 и 32 разрядные

операнды

AS Address Size -определяет формирование 16- и

32-разрядных адресов

171

S Segment override - указывает конкретный сегмент-

ный регистр

LOCK Префикс блокировки шины, при котором формируется сигнал LOCK

Код операции

w 1 Определяет размер операнда в байтах (w=0) или

нет (w=1)

d 1 Определяет направление передачи данных:

из регистра в регистр/память d=0

из регистра/памяти в регистр d=1

S 1 Расширение 8-битных данных до слова (двоичного)

S=1

В общем случае формат команды содержит обязательную и необязательную часть. Минимальная длина команды содержит обязательное поле-код операции, длиной 1 байт (например, команды сброса флагов CLC,CLD,CLI и др).

Необязательной частью команды являются префиксы.

1.19. АРХІТЕКТУРА СИСТЕМНОГО ІНТЕРФЕЙСУ СУЧАСНИХ ПК. ПРИЗНАЧЕННЯ КОМПОНЕНТ. РЕЖИМИ ПЕРЕДАЧІ ІНФОРМАЦІЇ ПО СИСТЕМНИМ ШИНАМ.

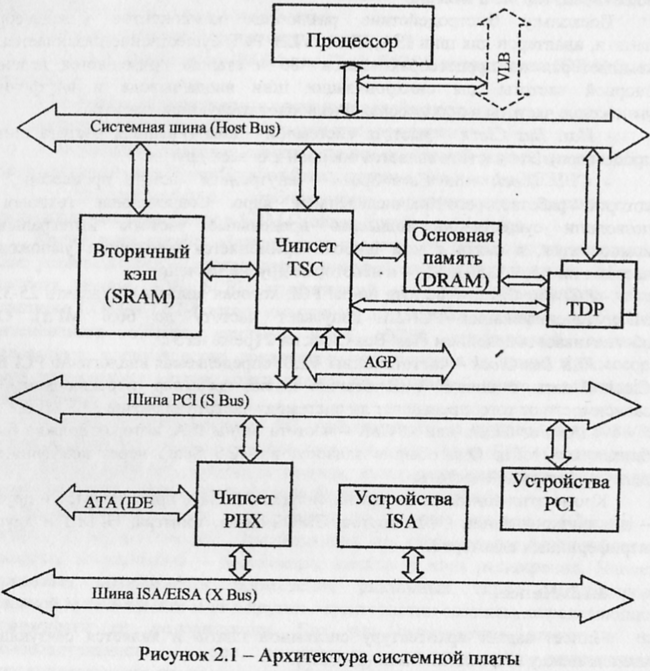

Системная или материнская, плата ПК является основой системного блока, определяющей архитектуру и производительность компьютера. На ней устанавливаются следующие обязательные компоненты: процессор и сопроцессор, память (постоянная ROM или Flash BIOS, оперативная DRAM, кэш SRAM), средства вода/вывода, интерфейсные схемы и разъемы шин расширения, кварцевый генератор синхронизации со схемой формирования сброса системы по сигналу PowerGood от блока питания или кнопки RESET, дополнительные стабилизаторы напряжения питания для низковольтных процессоров VRM.

Современные платы исполняются на основе чипсетов – наборов из нескольких БИС, реализующих все функции связи основных компонентов – процессора, памяти и шин росширения. Чипсет определяет возможности применения различных типов процессоров, основной и кэш-памяти и ряд других характеристик системы, определяющих возможности ее модернизации. Его тип влияет на производительность системы.

Современные чипсеты обеспечивают совместимость установленных на системную плату модулей и позволяют во время выполнения POST выполнять автоматическую идентификацию типов установленных компонент.

Основной тактовый генератор системной платы вырабатывает высокостабильные импульсы опорной частоты, используемой для синхронизации процессора, системной шины и шин ввода/вывода. Поскольку быстродействие различных компонентов существенно различается, в компьютерах на процессорах класса 486 и старше применяется деление опорной частоты для синхронизации шин ввода/вывода и внутреннее умножение частоты в процессорах.

Центральную роль в архитектуре играет процессор. К его локальной шине (Host Bus) подключаются модули вторичного кэша. Основная динамическая память имеет собственную мультиплексированную шину адреса и шину данных, обычно изолированную от локальной шины процессора.

Следующий этаж архитектуры – устройства подключенные к PCI. Эта шина является центральной в современных системных платах, и все интерфейсные адаптеры, а также системные средства ввода/вывода в конечном счете общаются с ядром системы через шину PCI. Кроме плат расширения, устанавливаемых в слоты шины PCI, ее абонентом является и мост PIIX.

О сновная

задача шин – объединить в одну систему

разнообразную номенклатуру модулей,

обеспечив их высокопроизводительную

надежную работу. Под надлежащей работой

следует понимать выполнение условий

открытости, совместимости, однотипности,

гибкости, надежности, ремонтопригодности,

эффективности и др. требований. Суть

этих всех требований можно сформулировать

так: замена одних шин другими не должна

сопровождаться появлением архитектурных

ограничений. Наличие существенных

различий в производительности между

различными модулями привело к

необходимости использовать в современных

ПК систему шин, вместо одной общей.

сновная

задача шин – объединить в одну систему

разнообразную номенклатуру модулей,

обеспечив их высокопроизводительную

надежную работу. Под надлежащей работой

следует понимать выполнение условий

открытости, совместимости, однотипности,

гибкости, надежности, ремонтопригодности,

эффективности и др. требований. Суть

этих всех требований можно сформулировать

так: замена одних шин другими не должна

сопровождаться появлением архитектурных

ограничений. Наличие существенных

различий в производительности между

различными модулями привело к

необходимости использовать в современных

ПК систему шин, вместо одной общей.

У разных шин организация работы разная. Однако при при этом ряд положений используется общий. Общая организация работы шины может быть представлена как совокупность механизмов каждый из которых выполняет вполне определенную функцию передачи информации, например, чтение из памяти или порта запись в них и т.д. Организацию управления работы шины можно представить, как переход от выполнения одного механизма к другому.

В ремя,

занимаемое выполнением отдельного

механизма называется циклом шины.

Продолжительность цикла шины является

случайной величиной, а его начало и

конец являются асинхронными. Для

упрощения управления шиной длина цикла

составляется из временных квантов

одинаковой продолжительности, называемых

тактом шины. Во время любого такта цикла

шины выполняются определенные действия,

которые можно разбить на две группы:

установление состояния шины и выполнение

команд, предписанных реализуемым

механизмом передачи.

ремя,

занимаемое выполнением отдельного

механизма называется циклом шины.

Продолжительность цикла шины является

случайной величиной, а его начало и

конец являются асинхронными. Для

упрощения управления шиной длина цикла

составляется из временных квантов

одинаковой продолжительности, называемых

тактом шины. Во время любого такта цикла

шины выполняются определенные действия,

которые можно разбить на две группы:

установление состояния шины и выполнение

команд, предписанных реализуемым

механизмом передачи.

Пакетный режим передачи. Адрес передается один раз, после чего передается пакет данных с линейно-возрастающими адресами. Количество циклов данных в пакете заранее определено, но перед последним циклом инициатор обмена при введенном сигнале разрешения обмена (IRDY#) снимает специальный сигнал пакетной передачи (FRAME#). После последней фазы данных инициатор снимает сигнал IRDY# и шина переходит в состояние покоя. Это стандартный режим работы шины PCI.

Конвейеризация обращений к памяти. Данный режим используется в высокоскоростных шинах (AGP). При неконвеиризированых обращениях шины во время реакции памяти на запрос шина простаивает. Конвейерный доступ позволяет в это же время передавать следующие запросы, а потом получить полный поток передаваемых данных. Спецификация AGP предусматривает возможность постановки в очередь до256 запросов, при этом поддерживает две пары очередей для операций записи и чтения памяти с высоким и низким приоритетом.

Сдвоенные передачи данных обеспечивают повышение пропускной способности шины в 2 раза без изменения тактовой частоты шины. Суть сдвоенной передачи в том, что блоки данных передаются, как по фронту так и по спаду сигнала синхронизации (в AGP в шине ATA в режиме UltraDMA-33).

1.20. РОЗПОДІЛЕННЯ СИСТЕМНИХ РЕСУРСІВ МІЖ КОМПОНЕНТАМИ ПК. Технологія PnP та її РЕАЛІЗАЦІЯ В ШИНАХ PCI та ISA/EISA.

Наиболее распространенными для подключения карт расширения PC являются шины ISA и PSI. В шину PSI заложены возможности автоматического конфигурирования установленных адаптеров. Спецификация шины ISA требует, чтобы всем картам назначались свои системные ресурсы – области адресов в пространствах памяти и ввода/вывода, линии запросов прерываний и каналы прямого доступа к памяти. При этом по используемым ресурсам платы не должны конфликтовать. Шина ISA не имеет механизмов автоматического конфигурирования и распределения ресурсов, так что все заботы по конфигурированию устанавливаемых адаптеров и разрешению конфликтов ложится на пользователя. Задача конфигурации осложняется и из-за отсутствия общего механизма автоматической передачи установленных параметров прикладному и системному программному обеспечению. После конфигурирования адаптеров, установленные параметры заносятся в какие-либо конфигурационные файлы. При необходимости смены конфигурации всю роботу по конфигурированию приходится проводить повторно.

Некоторое облегчение конфигурирования принесло применение в адаптерах энергонезависимой памяти (NVRAM или ее разновидности - EEPROM), хранящей конфигурации настроек, в том числе и использования системных ресурсов. Конфигурирование этих адаптеров выполняется программно специальной утилитой, а не с помощью джамперов. Во время конфигурирования утилита может проверить выбираемые установки на наличие конфликта. Преимуществом конфигурирования с помощью NVRAM является и то, что программный драйвер, «знающий» данную карту, сумеет прочитать и сделанные установки, так что необходимость в конфигурационных файлах отпадает.

Однако это еще не решение проблемы автоконфигурирования в полном объеме. Ключевым моментом в автоконфигурировании является возможность на начальном этапе конфигурирования изоляции каждой карты от всех остальных. Тогда программные средства конфигурирования смогут вести с картой корректный диалог, на который не влияет присутствие других карт. Кроме того необходимо обеспечить единый метод двустороннего обмена конфигурационной информацией между картой и программным обеспечением. Возможность изоляции карт при конфигурировании заложена в шины MCA, PCI и EISA. В EISA для каждого слота возможно программное селективное управление сигналом AEN, запрещающим дешифрацию адресов портов ввода/вывода. Кроме того, в системе с шиной EISA имеется дополнительная энергонезависимая память конфигурирования слотов. В шине ISA все сигналы всех слотов соединяются параллельно, а хранилище конфигурационной информации не предусмотрено.

Мосты PCI – аппаратные средства подключения шины PCI к другим шинам. Host Bridge – главный мост – используется для подключения к системной шине. Peer-to-Peer Bridge – одноранговый мост – используется для соединения двух шин PCI. При конфигурировании мостов им указывается распределение системных ресурсов по шинам, которые они связываются. Таким образом задаются пути транслирования управляющих сигналов по шинам и управление буферами данных, обеспечивая для каждого адреса памяти или ввода/вывода единственную шину назначения, по крайней мере для операций чтения.

Среди устройств PnP выделяется класс динамически конфигурируемых устройств DCD. Ресурсы, используемые ими, могут динамически переназначаться во время работы, не требуя перезагрузки операционной системы. К этому классу относятся устройства PnP ISA и PCI. Устройство DCD может находится в заблокированном состоянии, тогда ресурсы не могут быть изменены до разблокирования.