MU_k_KR_Shemoteh_EVM

.pdfМИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РФ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ

УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «КАЗАНСКИЙ НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ТЕХНИЧЕСКИЙ

УНИВЕРСИТЕТ им. А.Н. ТУПОЛЕВА-КАИ»

Чистопольский филиал «Восток»

Кафедра приборостроения

МЕТОДИЧЕСКИЕ УКАЗАНИЯ К КУРСОВОЙ РАБОТЕ

по дисциплине

«СХЕМОТЕХНИКА ЭВМ»

Индекс по учебному плану: Б1.В.ДВ.03.01

Направление подготовки: 09.03.01 Информатика и вычислительная техника

Квалификация: Бакалавр

Профиль подготовки: Вычислительные машины, комплексы, системы и сети

Вид профессиональной деятельности: проектно-конструкторская, проектно-

технологическая

Чистополь

2017 г.

В курсовой работе предлагается разработать устройство контроля за со-

стоянием некоторого циклического процесса по заданной структурной схеме.

Правильному протеканию процесса отвечает некоторая смена контрольных сиг-

налов от такта к такту:

Х1Х2Х3 = 000 – 110 – 000 – 011 – 000 – 101 – 000

В ходе выполнения курсовой работы необходимо выполнить неформальный синтез дискретного автомата, получить схему электрических принципиальную устройства контроля и разработать отдельные узлы устройства.

Основная часть расчетно-пояснительной записки включает в себя:

библиографическую проработку;

анализ технических требований;

расчет технических характеристик преобразователя по заданным точност-

ным, временным и функциональным требованиям;

расчет и разработку принципиальных электрических схем функционирова-

ния узлов преобразователя;

разработку и оформление принципиальных электрических схем устройства.

Объем расчетно-пояснительной записки - 20...35 страниц.

Графическая часть должна содержать:

принципиальную электрические схему устройства (формат А1).

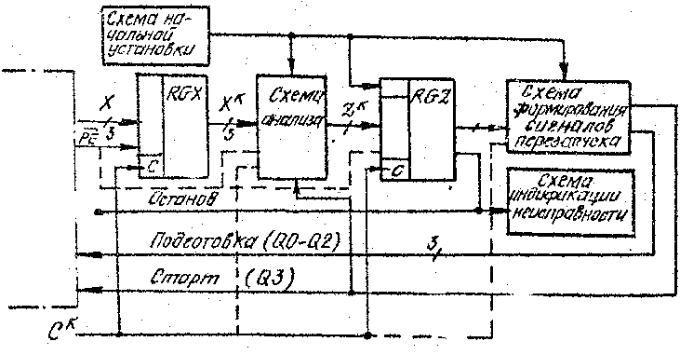

Пусть задана блок-схема устройства контроля за состоянием некоторого циклического процесса (рис.1). Правильному протеканию процесса отвечает сле-

дующая смена контрольных сигналов от такта к такту:

Х1Х2Х3 = 000 – 110 – 000 – 011 – 000 – 101 – 000

Рис. 1

Нарушение этой последовательности говорит о сбое в работе системы, на которой контролируемый процесс реализован.

При обнаружении сбоя схема анализа выдает набор Zk, по которому форми-

руются сигналы перезапуска:

QO – сигнал прерывания процесса;

Q1, Q2 – сигналы возврата к началу прерванного цикла;

Q3 – стартовый сигнал для возобновления прерванного цикла и перевода схемы анализа в режим индикации неисправности.

Если сбоя на повторном цикле не проявится, схема анализа выходит на ос-

новной рабочий режим. Если же попытка повторения прерванного цикла не увен-

чается успехом, индицируется неисправность, процесс останавливается.

Начальная установка устройства выполняется от механической кнопки с последующим формированием одиночного импульса нужной длительности и по-

лярности. Тактовая частота 1 МГц. Длительность синхроимпульсов 0,5 мкс.

Требуется разработать электрическую принципиальную схему устройства контроля в целом в базисе ИС KI55 из условия минимизации числа корпусов мик-

росхем. При этом энергопотребление должно быть возможно малым. В процессе проектирования необходимо учесть, что по сигналу прерывания процесса (сигнал

Q0) осуществляется блокировка регистров (сигналом  ), которая снимается стартовым сигналом Q3.

), которая снимается стартовым сигналом Q3.

Реализация схемы анализа – асинхронная.

Схема перезапуска – синхронная.

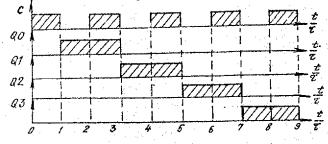

Временные диаграммы сигналов перезапуска отвечают рис. 2

Рис. 2.

Этапы выполнения Как видно из рис. 1 схема состоит из нескольких узлов:

1.Схема начальной установки.

2.Схема анализа.

3.Схема формирования сигнала перезапуска.

4.Схема индикации неисправности.

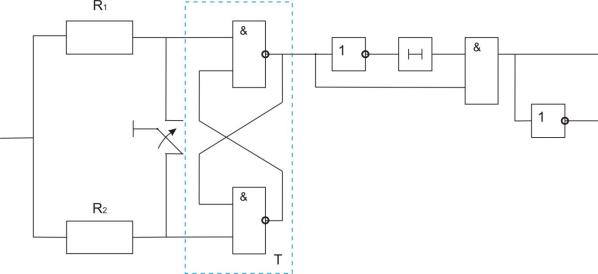

Схема начальной установки Реализована на микросхемах К155ЛА3, К155ЛИ1:

Где в качестве элемента |

|

|

|

|

мы используем 4 инвертора, тогда время |

|

|

|

|

||

|

|

|

|

||

|

|

|

|

||

|

|

|

задержки будет равно 60 нс (время задержки одного инвертора = 15 нс).

С помощью Т- бистабильной ячейки устраняются дребезги контактов.

Схема является типовой и используется уже в готовом виде.

Схема анализа.

Построение схемы анализа мы начнем с таблицы, в которой будут отражена заданная последовательность. Для индикации трех режимов работы схемы доста-

точно иметь 2 выхода: Z1 и Z2. В основном цикле Z1Z2 = 00, для повторного – 10,

при индикации неисправности – 11.

Таблица 1

х1х2х3 |

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

110 |

111 |

101 |

100 |

S k-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

(1),00 |

8,10 |

9,10 |

10,10 |

2*,00 |

12,10 |

13,10 |

14,10 |

|

|

|

|

|

|

|

|

|

2 |

3*,00 |

8,10 |

9,10 |

10,10 |

(2),00 |

12,10 |

13,10 |

14,10 |

|

|

|

|

|

|

|

|

|

3 |

(3),00 |

8,10 |

4*,00 |

10,10 |

11,10 |

12,10 |

13,10 |

14,10 |

|

|

|

|

|

|

|

|

|

4 |

5*,00 |

8,10 |

(4),00 |

10,10 |

11,10 |

12,10 |

13,10 |

14,10 |

|

|

|

|

|

|

|

|

|

5 |

(5),00 |

8,10 |

9,10 |

10,10 |

11,10 |

12,10 |

6*,00 |

14,10 |

|

|

|

|

|

|

|

|

|

6 |

1*,00 |

8,10 |

9,10 |

10,10 |

11,10 |

12,10 |

(6),00 |

14,10 |

|

|

|

|

|

|

|

|

|

7 |

(7) п,10 |

(7),11 |

(7),11 |

(7),11 |

15п,10 |

(7),11 |

(7),11 |

(7),11 |

|

|

|

|

|

|

|

|

|

8 |

7,10 |

(8) п,10 |

(8),11 |

(8),11 |

(8),11 |

(8),11 |

(8),11 |

(8),11 |

|

|

|

|

|

|

|

|

|

9 |

7,10 |

(9),11 |

(9) п,10 |

(9),11 |

(9),11 |

(9),11 |

(9),11 |

(9),11 |

|

|

|

|

|

|

|

|

|

10 |

7,10 |

(10),11 |

(10),11 |

(10) п,10 |

(10),11 |

(10),11 |

(10),11 |

(10),11 |

|

|

|

|

|

|

|

|

|

11 |

7,10 |

(11),11 |

(11),11 |

(11),11 |

(11) п,10 |

(11),11 |

(11),11 |

(11),11 |

|

|

|

|

|

|

|

|

|

12 |

7,10 |

(12),11 |

(12),11 |

(12),11 |

(12),11 |

(12) п,10 |

(12),11 |

(12),11 |

|

|

|

|

|

|

|

|

|

13 |

7,10 |

(13),11 |

(13),11 |

(13),11 |

(13),11 |

(13),11 |

(13) п,10 |

(13),11 |

|

|

|

|

|

|

|

|

|

14 |

7,10 |

(14),11 |

(14),11 |

(14),11 |

(14),11 |

(14),11 |

(14),11 |

(14) п,10 |

|

|

|

|

|

|

|

|

|

15 |

16п,10 |

(15),11 |

(15),11 |

(15),11 |

(15),10 |

(15),11 |

(15),11 |

(15),11 |

|

|

|

|

|

|

|

|

|

16 |

(16),10 |

(16),11 |

17п,10 |

(16),11 |

(16),11 |

(16),11 |

(16),11 |

(16),11 |

|

|

|

|

|

|

|

|

|

17 |

18п,10 |

(17),11 |

(17),10 |

(17),11 |

(17),11 |

(17),11 |

(17),11 |

(17),11 |

|

|

|

|

|

|

|

|

|

18 |

(18),10 |

(18),11 |

(18),11 |

(18),11 |

(18),11 |

(18),11 |

19п,10 |

(18),11 |

|

|

|

|

|

|

|

|

|

19 |

1*,00 |

(19),11 |

(19),11 |

(19),11 |

(19),11 |

(19),11 |

(19),10 |

(19),11 |

|

|

|

|

|

|

|

|

|

Таким образом, таблица получается очень большой, что приводит нас к мысли об упрощении этой таблицы. Так как в основном цикле и на повторном цикле мы проверяем практически одно и то же, то таблица сократиться, и будет выглядеть следующим образом (Z=0 – нет ошибки; Z=1 - ошибка):

Таблица 2

х1х2х3 |

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

110 |

111 |

101 |

100 |

S k-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

(1),0 |

7,1 |

7,1 |

7,1 |

2*,0 |

7,1 |

7,1 |

7,1 |

|

|

|

|

|

|

|

|

|

2 |

3*,0 |

7,1 |

7,1 |

7,1 |

(2),0 |

7,1 |

7,1 |

7,1 |

|

|

|

|

|

|

|

|

|

3 |

(3),0 |

7,1 |

4*,0 |

7,1 |

7,1 |

7,1 |

7,1 |

7,1 |

|

|

|

|

|

|

|

|

|

4 |

5*,0 |

7,1 |

(4),0 |

7,1 |

7,1 |

7,1 |

7,1 |

7,1 |

|

|

|

|

|

|

|

|

|

5 |

(5),0 |

7,1 |

7,1 |

7,1 |

7,1 |

7,1 |

6*,0 |

7,1 |

|

|

|

|

|

|

|

|

|

6 |

1*,0 |

7,1 |

7,1 |

7,1 |

7,1 |

7,1 |

(6),0 |

7,1 |

|

|

|

|

|

|

|

|

|

7 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

|

|

|

|

|

|

|

|

|

где 7-ое состояние – состояние случайной ошибки.

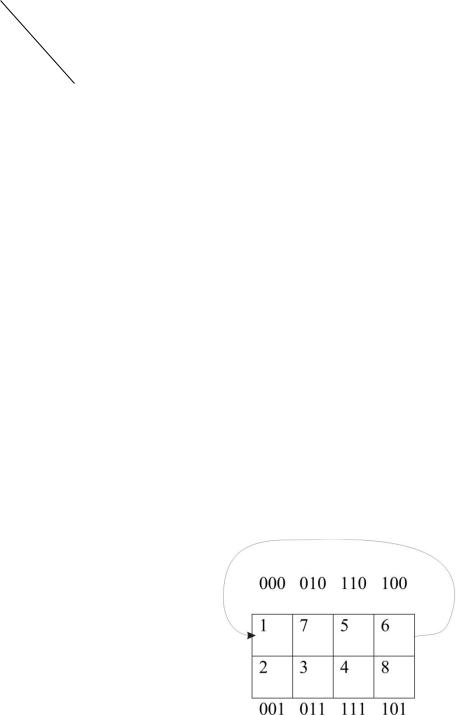

Чтобы по данной таблице построить схему анализа, нам придется закодиро-

вать ее, а затем разбить на несколько таблиц, характеризующих состояние сигна-

лов и переменных.

Таблица 3

После кодирования состояний таблица 2 будет выглядеть так:

Таблица 4

х1х2х3 |

|

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

110 |

111 |

|

101 |

100 |

S k-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

(1),0 |

7,1 |

7,1 |

7,1 |

2*,0 |

7,1 |

|

7,1 |

7,1 |

|

|

|

|

|

|

|

|

|

|

2 |

3*,0 |

1,1 |

1,1 |

1,1 |

(2),0 |

1,1 |

|

1,1 |

1,1 |

|

|

|

|

|

|

|

|

|

|

3 |

(3),0 |

7,1 |

4*,0 |

7,1 |

7,1 |

7,1 |

|

7,1 |

7,1 |

|

|

|

|

|

|

|

|

|

|

4 |

5*,0 |

3,1 |

(4),0 |

3,1 |

3,1 |

3,1 |

|

3,1 |

3,1 |

|

|

|

|

|

|

|

|

|

|

5 |

(5),0 |

7,1 |

7,1 |

7,1 |

7,1 |

7,1 |

|

6*,0 |

7,1 |

|

|

|

|

|

|

|

|

|

|

6 |

1*,0 |

5,1 |

5,1 |

5,1 |

5,1 |

5,1 |

|

(6),0 |

5,1 |

|

|

|

|

|

|

|

|

|

|

7 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

(7),1 |

|

(7),1 |

(7),1 |

|

|

|

|

|

|

|

|

|

|

Перейдя к переменным у1у2у3: |

|

|

|

|

|

|

|||

|

|

|

|

Таблица 5 |

|

|

|

|

|

х1х2х3 |

|

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

110 |

111 |

|

101 |

100 |

у1у2у3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

(000),0 |

010,1 |

010,1 |

010,1 |

001*,0 |

010,1 |

|

010,1 |

010,1 |

|

|

|

|

|

|

|

|

|

|

2 |

011*,0 |

000,1 |

000,1 |

000,1 |

(001),0 |

000,1 |

|

000,1 |

000,1 |

|

|

|

|

|

|

|

|

|

|

3 |

(011),0 |

010,1 |

111*,0 |

010,1 |

010,1 |

010,1 |

|

010,1 |

010,1 |

|

|

|

|

|

|

|

|

|

|

4 |

110*,0 |

011,1 |

(111),0 |

011,1 |

011,1 |

011,1 |

|

011,1 |

011,1 |

|

|

|

|

|

|

|

|

|

|

5 |

(110),0 |

010,1 |

010,1 |

010,1 |

010,1 |

010,1 |

|

100*,0 |

010,1 |

|

|

|

|

|

|

|

|

|

|

6 |

000*,0 |

110,1 |

110,1 |

110,1 |

110,1 |

110,1 |

|

(100),0 |

110,1 |

|

|

|

|

|

|

|

|

|

|

7 |

(010),1 |

(010),1 |

(010),1 |

(010),1 |

(010),1 |

(010),1 |

|

(010),1 |

(010),1 |

|

|

|

|

|

|

|

|

|

|

Построим таблицы для z, у1, у2 и у3 |

по отдельности: |

|

|

|

|

|||||

|

|

|

|

|

Таблица 6 |

|

|

|

||

х1х2х3 |

|

|

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

|

110 |

111 |

101 |

100 |

|

у1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

|

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

4 |

1 |

0 |

1 |

|

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

5 |

1 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

|

1 |

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

7 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 7 |

|

|

|

||

х1х2х3 |

|

|

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

|

110 |

111 |

101 |

100 |

|

у2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

|

1 |

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

2 |

1 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

3 |

1 |

1 |

1 |

|

1 |

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

4 |

1 |

1 |

1 |

|

1 |

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

5 |

1 |

1 |

1 |

|

1 |

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

|

1 |

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

7 |

1 |

1 |

1 |

|

1 |

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

Таблица 8

х1х2х3 |

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

110 |

111 |

101 |

100 |

у3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

2 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

3 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

5 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

6 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

Таблица 9

х1х2х3 |

|

|

|

|

|

|

|

|

|

000 |

001 |

011 |

010 |

110 |

111 |

101 |

100 |

z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

3 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

7 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

В данной схеме используется специальный асинхронный регистр внутрен-

них состояний, который строится на основе элементов И-ИЛИ-НЕ. По сути, для реализации внутренних переменных применяются асинхронные RSтриггеры с прямым управлением.