- •Лекция 10. Организация микропроцессорной системы

- •Лекция 12. Параллельные компьютерные системы Классификация параллельных вс

- •"Фон-Неймановские" и "не-Фон-Неймановские" архитектуры

- •Системы с общей и распределенной памятью

- •Способы межмодульного соединения (комплексирования)

- •Распределенный и разделяемый вычислительный ресурс второго уровня. Решающие поля

- •Способы распараллеливания

- •2. Рассмотрим задачу счета способом "пирамиды".

- •Лекция 11. Параллельные компьютерные системы Классификация параллельных вс

- •"Фон-Неймановские" и "не-Фон-Неймановские" архитектуры

- •Системы с общей и распределенной памятью

- •Способы межмодульного соединения (комплексирования)

- •Распределенный и разделяемый вычислительный ресурс второго уровня. Решающие поля

- •Способы распараллеливания

- •2. Рассмотрим задачу счета способом "пирамиды".

2. Рассмотрим задачу счета способом "пирамиды".

Эту задачу мы исследовали при рассмотрении ВС типа SPMD. Посмотрим еще раз, какая синхронизация нам здесь потребуется.

Пусть необходимо перемножить все элементы некоторого массива {a1,a2,... , a10}. Каждый элемент занимает одну ячейку памяти. Пусть число процессоров в ВС n=4. Чтобы распараллелить этот процесс, примем схему счета "пирамидой" (рис. 2.7).

Рис. 2.7. Граф-схема выполнения операции "свёртки"

Количество уровней операций в ней ]log2 m[=]log210[=4 (]x[ — ближайшее целое, не меньшее x).

Расширим массив, дополнив его ячейками, в которых будем хранить промежуточные частные произведения. Тогда весь план счета примем таким, как показано на рис. 2.8. Отмечены процессоры, выполняющие указанную операцию.

Рис. 2.8. Схема выполнения операции свёртки четырьмя процессорами

Следовательно, надо так написать программу, одну для всех процессоров, предусмотрев необходимую переадресацию для выборки и вычисления "своих" данных, чтобы по ней выбирались два соседних элемента этого удлиненного массива, а результат их умножения отправлялся в очередную ячейку этого "удлинения".

Возникает только одна трудность: для первых пяти произведений данные есть, а вот последующие произведения должны выполняться тогда, когда для них будут найдены исходные данные.

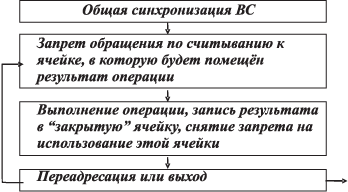

Значит, процессоры, которым выпало произвести такие умножения, должны "уметь" обнаруживать отсутствие данных и дожидаться их появления. Т.е. требуется синхронизация процессоров по использованию общих данных.

Здесь распараллеливание по данным смыкается с распараллеливанием по управлению.

Возможная схема общей для всех процессоров программы — на рис. 2.9. Она реализована в примере для ВС типа SPMD.

Рис. 2.

|

Конвейеры операций Выполнение любой операции складывается из нескольких последовательных этапов, каждый из которых может выполняться своим функциональным узлом. Это легко показать на операциях сложения и умножения. Выполнение деления мантисс (порядки вычитаются) чаще всего производятся с помощью вычитания из делимого делителя, сдвига влево полученного остатка, нового вычитания делителя из результата сдвига и т.д. В некоторых ВС находится обратная величина делителя с помощью аппроксимирующих полиномов. Затем делимое умножается на эту величину. Пусть задана операция, выполнение которой разбито на n последовательных этапов. Пусть ti — время выполнения i-го этапа. При последовательном их выполнении операция выполняется за время:

а быстродействие ЭВМ или одного процессора ВС, выполняющего только эту операцию, составит:

Выберем время такта — величину tT = max ti} и потребуем при разбиении на этапы, чтобы для любого i = 1, ...,n выполнялось условие ti + t(i+1) mod n > tT. Т.е. чтобы никакие два последовательных этапа (включая конец и новое начало операции) не могли быть выполнены за время одного такта. Функциональные узлы, выполняющие последовательные этапы одной операции, целесообразно выстроить в единую конвейерную линию, где устройство, выполняющее некоторый этап, закончив его для операции над одним набором данных, переходило бы в следующем такте к выполнению этого же этапа той же операции для другого набора исходных данных. Например, на рис. 3.1 представлен конвейер выполнения операции сложения.

Рис. 3.1. Выполнение операции сложения на конвейере Пусть реализуется поток команд одного процессора или существует доступ к этому устройству нескольких процессоров так, что в каждом такте возможно задание на выполнение сложения новой пары чисел. Тогда временная диаграмма работы конвейера может иметь вид, представленный на рис. 3.2.

Рис. 3.2. Схема заполнения конвейера Максимальное быстродействие процессора при полной загрузке конвейера составляет

Число n — количество уровней конвейера, или глубина перекрытия, т.к. каждый такт на конвейере параллельно выполняются n операций. Чем больше число уровней (станций), тем больший выигрыш в быстродействии может быть получен. В проекте МВК "Эльбрус-3" АЛУ его ЦП имеет конвейерные ИУ сложения (n=5), умножения (n=5), деления (n=8 для полусловного формата, — 32 разряда, n=16 для словного формата). Логические операции также выполняются на конвейере с n=2. Известна оценка

т.е.

выигрыш в быстродействии получается

в

Реальный выигрыш в быстродействии оказывается всегда меньше, чем указанный выше, поскольку:

Векторные конвейеры. "Зацепление" векторов Наряду с использованием конвейеров для обработки единичных (скалярных) данных, используют так называемые векторные конвейеры, единичной информацией для которых являются вектора — массивы данных. Применение векторных конвейеров определило класс ВС — векторно-конвейерных ВС, сегодня ещё являющихся основой построения некоторых супер-ЭВМ — ВС сверхвысокой производительности. Для эффективности векторно-конвейерных ВС (например, для подготовки алгоритмов решения задач на ВС "Электроника-ССБИС") необходима векторизация задач. Это — такое преобразование алгоритма, при котором максимально выделяются (если не вся задача сводится к этому) элементы обработки массивов данных одинаковыми операциями. Сюда входят все задачи, основанные на матричных преобразованиях, обработка изображений, сигналов, моделирование поведения среды и т.д. В основе векторного конвейера лежит то же самое разбиение операции на уровни или этапы выполнения, но он дополняется средствами аппаратной поддержки, позволяющими по информации о векторах организовать последовательную загрузку конвейера элементами векторов, учитывая их длину.

Пусть

необходимо выполнить операцию C

= A × B,

т.е. cj

= aj

+ bj,

j

= 1, ...,N.

Пусть на регистрах СОЗУ записаны

вектора A

и B.

Группа регистров отведена для

результатов C.

Для управления этим процессом известны

дескрипторы векторов DA

,DB

,DC,

где D Пусть операция умножения выполняется за три этапа. Тогда можно представить временную диаграмму получения N результатов при предположении о назначении функциональных устройств (рис. 3.3).

Рис. 3.3. Умножение векторов на конвейере В составе АЛУ может быть два и более конвейерных устройств, специализированных каждое для выполнения некоторой операции. Тогда возможно и эффективно "зацепление" векторов, иллюстрируемое примером на рис. 3.4 для выполнения сложной операции над векторами: D=A× B+C.

Рис. 3.4. "Зацепление" векторов Здесь два конвейера образовали один, с глубиной перекрытия n = n× + n+. Очередной результат умножения немедленно направляется на конвейер сложения, куда параллельно направляется необходимый сомножитель.

|

|

|

9

|

Выполнение операций на стеке В вычислительной технике повсеместно используется такая структура данных, как стек. Его применение при выполнении арифметических и логических операций в арифметическо-логическом устройстве (АЛУ) позволяет реализовать безадресную систему команд, что, в свою очередь, дает возможность минимизировать число обращений к оперативной памяти, осуществить буферизацию при многоуровневой памяти, кодировать большое число команд в одном слове. Рассмотрим механизмы обработки информации на стеке и формирования безадресных команд. Прежде всего - об идее применения безадресных команд. Рассматривая структуру команд, мы можем отметить, что практически команды бывают одно-, двух-, трехадресные. Трехадресная команда, как правило, по законченности соответствует одному оператору, т.к. отображает действие над двумя операндами и результат. Двухадресная команда — это такая команда, где один из адресов подразумевается (например, аккумулятор или сумматор), или результат направляется по одному из указанных адресов. То же касательно одноадресной команды: по числу адресов - число обращений к памяти, не считая считывания самой команды. Возникает вопрос: можно ли отделить загрузку регистров сверхоперативного запоминающего устройства (СОЗУ) от собственно выполнения команды, сделать эту загрузку опережающей, выполнение команды производить только с использованием подразумеваемых адресов СОЗУ и при этом в целом минимизировать количество обращений к ОП? Ответ приводит к структуре безадресных команд и к выполнению операций на стеке. Стек представляет собой множество последовательно пронумерованных регистров СОЗУ или ячеек ОП, снабженное указателем вершины стека УВС, в котором автоматически при записи и считывании устанавливается номер (адрес) последнего занятого регистра — вершины стека. При записи в стек (загрузка стека) слово пишется в следующий по номеру регистр, а УВС увеличивается на единицу. При считывании извлекается слово с адресом, указанным в УВС. Затем УВС уменьшается на единицу. Таким образом, в стеке реализуется правило последний "пришел — первый ушел". Адреса памяти фигурируют только в командах загрузки стека и записи из стека в память. Значения выражений можно вычислять полностью безадресным способом. Команда, состоящая только из кода операции, извлекает из стека один или два операнда, выполняет операцию и заносит результат в стек. На рис. 3.5 приведен пример преобразования стека при выполнении трех команд программы.

Рис. 3.5. Выполнение команд на стеке Вычисления с использованием стеков удобно задавать, описывать и программировать с помощью польской инверсной (бесскобочной) записи арифметических выражений ПОЛИЗ (предложил польский математик Лукашевич в 1929 г.). Запись производится по правилу "читаем арифметическое выражение слева направо и последовательно друг за другом выписываем встречающиеся операнды". Как только окажется, что все операнды некоторой операции выписаны, записываем знак этой операции, условно учитываем вместо операндов и знака операции потенциальное имя ее результата. Это может породить возможность записи новой операции; или же будем продолжать выписывать операнды, если условно учтенный результат не позволяет записать знак операции. Запись на ПОЛИЗ состоит из цепочек имен и цепочек операций. Например,

y

:= (k + (l - mn))(a - b)

Последовательность символов в ПОЛИЗ может рассматриваться как программа вычисления значения данного выражения, если под именами понимать команды загрузки стека (кроме случая, когда имени следует знак операции :=, тогда это имя определяет запись из стека), а под знаками операций — безадресные команды, содержащие только коды операций. Удобно ввести команду вида Зп У — записи из стека по адресу У. Тогда мы получим окончательный вид программы klmn × - + ab - × Зп Y (3.1) Не будем отображать УВС, интерпретируя стек магазинной памятью. Тогда схема выполнения данной программы сводится к представленной на рис. 3.6.

Рис. 3.6. Выполнение программы на стеке

|

|

|

|

|

|

|

.

|

Лекция 13: Распараллеливание в ВС на уровне исполнительных устройств | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

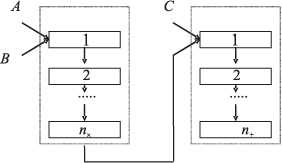

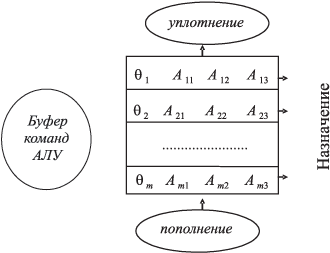

Обобщенная процедура динамического распараллеливания в многофункциональном АЛУ В многопроцессорном вычислительном комплексе "Эльбрус-2" используется динамическое распределение работ между исполнительными устройствами АЛУ. При этом успешно разрешается противоречие между безадресной системой команд, предполагающей их выполнение на стеке, и возможностью одновременной загрузки многих исполнительных устройств. При ближайшем рассмотрении стек представляется сугубо последовательностной структурой. Работа со стеком, как через "узкое горло", производится с использованием его вершины, и в случае многофункциональных АЛУ (т.е. АЛУ, состоящих из набора нескольких специализированных по операциям исполнительных устройств) представляется проблематичной. Казалось бы, стек по самой своей природе не предназначен для распараллеливания. Однако это не так, что и было продемонстрировано в МВК "Эльбрус-2". Здесь мы обобщим данный опыт. Формирование потока трехадресных команд В ИУ АЛУ в основном выполняются двуместные операции. Для выполнения такой операции надо знать код операции, адреса двух операндов (как правило, — в СОЗУ) и адрес результата. Т.е. АЛУ в общем случае оперирует трехадресными командами вида θA1A2A3. Для эффективного использования многофункционального АЛУ надо в каждый момент иметь в рассмотрении большое число таких команд, чтобы на их основе производилась полная загрузка заданиями и параллельная работа всех ИУ. Значит, надо иметь некоторый буфер команд АЛУ (рис. 3.7), в котором формируется и поддерживается в достаточном количестве множество команд данной структуры. Готовые к выполнению команды из этого буфера назначаются на ИУ. Буфер "снизу" пополняется устройством управления новыми командами взамен назначенных для выполнения.

Рис. 3.7. Обработка буфера команд АЛУ В ЦП МВК "Эльбрус-2" для загрузки 10 ИУ разной специализации просматривается до 30 команд. Такой буфер и есть "окно просмотра", через которое проходят исполнительные команды, сформированные на основе выполняемой программы, m — максимальное число команд в "окне просмотра". Буфер может заполняться УУ после базирования и индексации команд. Выше говорилось, что стек максимально снижает число обращений к ОП. Кроме того, ПОЛИЗ - естественный и простой результат трансляции с любого алгоритмического языка. Однако выполнение операций на стеке заключается в последовательном преобразовании его вершины. Это, казалось бы, исключает параллелизм, но и на ПОЛИЗ он виден. Например, по приведенной выше записи можно выделить первые параллельные операции счета:

— две двуместные операции умножения и вычитания, которыми можно бы было загрузить два ИУ. Значит, чтобы распараллелить выполнение программы на стеке, надо выполнить промежуточный перевод

— динамически, в процессе выполнения программы. Т.е. от безадресной системы необходимо перейти к системе программирования, использующей адреса. Тогда команды будут иметь вид тех процедур, о которых говорилось выше. Для этого предполагается, что стек формируется не на основе данных, как выше, а на основе их адресов в СОЗУ, вне стека. Т.е. данные и промежуточные результаты располагаются в регистрах СОЗУ, а их адресами загружается стек; в стеке представлены не данные, а их адреса. Такой стек называется адресным стеком. Расположение же данных (включая промежуточные результаты) в СОЗУ планируется аппаратно, динамически так, чтобы оптимально использовать ограниченный объем СОЗУ (или предоставляемой его области) при достижении максимального параллелизма. Быстрые регистры СОЗУ являются распределяемым ресурсом. Подобная общая схема работы АЛУ представлена на рис. 3.8.

Рис. 3.8. Схема распараллеливания выполнения команд Рассмотрим работу блока динамического распределения регистров. Он обрабатывает два списка адресов регистров СОЗУ: адресный стек и список свободных регистров. Ранее мы видели, что в программе ПОЛИЗ есть три вида команд: загрузка стека, выполнение операции, запись из стека. Каждая из этих команд порождает трехадресную команду следующим образом. Загрузка стека порождает трехадресную команду, в которой адрес считываемой величины в памяти указывается по первому адресу формируемой команды. По третьему адресу указывается первый адрес из списка свободных регистров. Этот адрес образует новую вершину адресного стека. (Т.е. регистр с этим адресом образует новую вершину стека, на котором производится счет.) Команда выполнения операции порождает трехадресную команду, где одним из операндов является вершина стека. Если операция одноместная, адрес, стоящий в вершине адресного стека, становится первым адресом команды. Если операция двуместная, то адрес из вершины адресного стека становится вторым адресом формируемой команды, а первым адресом становится адрес, составляющий второй уровень адресного стека. Третий адрес берется из списка свободных регистров. Использованные адреса операндов исключаются из адресного стека и переводятся в конец списка свободных регистров. Адрес регистра, составивший третий адрес сформированной команды, т.е. адрес результата, включается в адресный стек как его новая вершина. Запись из стека порождает трехадресную команду, где первый адрес — адрес из вершины адресного стека, третий адрес — адрес записи (в СОЗУ или ОП). Использованный адрес из вершины адресного стека исключается из этого стека и записывается в конец списка свободных регистров. Пример.

В таблице 3.1 представлен перевод программы из безадресной системы команд в трехадресную.

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||