Курсач / Курсовая работа. 20 вариант. Сейткалиев Диас.ИС-16-1п

.pdf

3.4 Методы минимизации на основе карт Карно

Куб Карно — графический способ минимизации переключательных (булевых) функций, обеспечивающий относительную простоту работы с большими выражениями и устранение потенциальных гонок. Представляет собой операции попарного неполного склеивания и элементарного поглощения. Карты Карно рассматриваются как перестроенная соответствующим образом таблица истинности функции. Карты Карно можно рассматривать как определённую плоскую развертку n-мерного булева куба.

Карты Карно были изобретены в 1952 году Эдвардом В. Вейчем и усовершенствованы в 1953 году Морисом Карно, физиком из «Bell Labs», и были призваны помочь упростить цифровые электронные схемы.

В карту Карно булевы переменные передаются из таблицы истинности и упорядочиваются с помощью кода Грея, в котором каждое следующее число отличается от предыдущего только одним разрядом.

Рисунок 3.13 – Примеры карт Карно

21

4 Триггеры

Триггером называется устройство, имеющее два устойчивых состояния и сохраняющее любое из них сколь угодно долго после снятия внешнего воздействия, вызвавшего переход триггера из одного состояния в другое. Поэтому говорят, что триггер обладает памятью. Триггер можно представить в общем случае состоящим из ячейки памяти и устройства управления (порой весьма сложного), преобразующего входную информацию в комбинацию сигналов, под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний.

Такими цифровыми микросхемами являются триггеры (англ. – Trigger или Flip-Flop). В отличие от простых логических микросхем, которые называют комбинационными (НЕ, И-НЕ, ИЛИ и другие) и их сигналы на выходе чётко соответствуют сигналам на входе, то триггеры относятся к последовательным или последовательностным микросхемам, уровень выходного напряжения которых, зависит от того в какой последовательности поступали сигналы на вход триггера. С помощью триггеров строят более сложные цифровые микросхемы.

Сигналы, поступившие на вход триггера, могут храниться только до тех пор, пока на него подается напряжение питания. После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит.

Внутреннее устройство триггера. Простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время.

Рисунок – 4 Схема триггерной ячейки на логических элементах (RS триггер)

22

Схема на рисунке выше представляет простейший триггер (или триггерная ячейка), который имеет два входа и два выхода. Входы триггера реагируют на низкий логический уровень: вход R – сброс (англ. Reset – сброс) и вход S – установка (англ. Set – установка), выходы: прямой Q(англ. Quit – выход) и инверсный –Q.

23

4.1 Типы триггеров

По функциональному признаку различают RS-триггеры, D-триггеры, Т- триггеры и JK-триггеры, а также их комбинации.

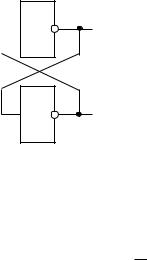

Основу любого триггерного устройства составляет элементарная ячейка памяти на двух инверторах с кольцом положительной обратной связи, называемая защелкой (рисунок 4.1).

1

1

Рисунок 4.1 – Элементарная ячейка

При подаче питания ЛЭ не могут находиться в активной области передаточной характеристики, так как петлевое усиление много больше единицы, и ячейка переходит в одно из двух устойчивых состояний с

инверсными уровнями на выходах Q и Q . Это состояние ячейка будет хранить, пока включен источник питания.

24

4.1.1 RSтриггер

RS триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход триггера Q (Quit — выход англ.) в нулевое состояние (записывать ноль).

В простейшем случае RS триггер это два логических элемента "2И-НЕ", соединенные последовательно друг с другом. Его принципиальная схема приведена на рисунке 4.2

Рисунок 4.2

Схема простейшего RS триггера на схемах "2И-НЕ". Входы R и S инверсные (активный уровень'0')

Рисунок – 4.3 Обозначение RS триггера

Рассмотрим принцип работы RS триггера, выполненный по изображенной на рисунке 1 схеме подробнее. Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "2ИНЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "2И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе Q. Если на выходе верхнего логического элемента "2И-НЕ" Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента "2И-НЕ" появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть при единичных входных уровнях схема RS триггера работает точно так - же как и схема на инверторах.

Подадим на вход S нулевой потенциал. Согласно таблице истинности логического элемента "И - НЕ" на выходе Q появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала.

Теперь, даже если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер логическую единицу.

Точно так же можно записать в RS-триггер и логический ноль. Для этого следует воспользоваться входом R. Так как активный уровень на входах

25

оказался нулевым, то эти входы — инверсные. Составим таблицу истинности RS триггера. Входы R и S в этой таблице будем использовать прямые, то есть и запись нуля, и запись единицы будут осуществляться единичными потенциалами (таблица 4).

Таблица 4

Таблица истинности RS триггера

С |

R |

S |

Q(t) |

Q(t+) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

|

|

|

|

|

||

0 |

x |

x |

1 |

1 |

||

|

||||||

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

|

|

|

|

|

||

1 |

0 |

0 |

1 |

1 |

||

|

||||||

1 |

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

|

|

|

|

|

||

1 |

0 |

1 |

1 |

1 |

||

|

||||||

1 |

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

|

|

|

|

|

||

1 |

1 |

0 |

1 |

0 |

||

|

||||||

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

|

|

|

|

|

||

1 |

1 |

1 |

1 |

* |

||

|

RS триггер можно построить и на логических элементах "ИЛИ". Его схема приведена на рисунке 4.4. Принцип работы RS триггера, собранный на логических элементах "ИЛИ" будет точно таким же, как и рассмотренный ранее. Единственное отличие в работе этой схемы по сравнению с предыдущей схемой RS триггера будет заключаться в том, что сброс и установка триггера будет производиться единичными логическими уровнями. Эти особенности связаны с принципами работы инверсной логики, которые рассматривались ранее.

Рисунок 4.4 - Схема простейшего RS триггера на логических элементах ИЛИ-

НЕ. Входы R и S прямые (активный уровень '1')

Так как RS триггер при реализации его на логических элементах "И" и "ИЛИ" работает одинаково (его принцип работы от схемы не зависит), то и условно-графическое изображение на принципиальных схемах тоже одинаково. Условно-графическое изображение RS триггера на принципиальных схемах приведено на рисунке 4.3

26

Рисунок 4.5 - Условно-графическое обозначение RS триггера Синхронный RS триггер

Схема RS триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RS триггер и триггер Шмитта) эти триггеры получили название асинхронных.

27

4.1.1.1 Синхронный RS – триггер

Триггеры, записывающие сигналы только при наличии синхронизирующего сигнала называются синхронными. Принципиальная схема синхронного RS-триггера приведена на рисунке 4.6.

Рисунок 4.6 - Схема синхронного RS триггера, построенного на элементах "И- НЕ"

В таблице 4.1 приведена таблица истинности синхронного RS триггера. Принцип работы RS триггера не изменился, добавилось дополнительное условие: синхронизация момента срабатывания схемы. В этой таблице символ 'x' означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера.

Таблица 4.1

Таблица - истинности синхронного RS триггера.

С |

R |

S |

Q(t) |

Q(t+) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

|

|

|

|

|

||

0 |

x |

x |

1 |

1 |

||

|

||||||

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

|

|

|

|

|

||

1 |

0 |

0 |

1 |

1 |

||

|

||||||

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

|

|

|

|

|

||

1 |

0 |

1 |

1 |

1 |

||

|

||||||

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

|

|

|

|

|

||

1 |

1 |

0 |

1 |

0 |

||

|

||||||

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

1 |

* |

||

|

||||||

|

|

|

|

|

|

Как мы уже показали выше, RS триггеры могут быть реализованы на различных логических элементах. При этом их логика работы не изменяется. В то же самое время триггеры часто выпускаются в виде готовых микросхем (или реализуются внутри БИС в виде готовых модулей), поэтому на принципиальных схемах синхронные RS триггеры обычно изображаются в виде условно-графических обозначений. Условно-графическое обозначение синхронного RS триггера приведено на рисунке 4.7.

28

Рисунок 4.7 - Условно-графическое обозначение синхронного RS триггера

29

4.1.2 D-триггер

D-триггер(от английского Delay–задержка) имеет один информационный (D – Data – данные) и один тактируемый (С – Clock – тактовая последовательность) вход. Такой триггер можно получить из RS-триггера,подав на R-вход инвертированный сигнал с S-входа (рисунок 4.8, а). Уловное обозначение D-триггера со статическим управлением показано на рисунке 4.8, б.

|

|

S |

|

|

|

|

T |

|

D |

T |

|

|

|

C |

|

||

|

|

|

|

|

|

1 |

|

R |

|

|

|

|

|

а) |

|

б) |

в) |

Рисунок 4.8 – D-триггер со статическим управлением

Из временных диаграмм, приведенных на рисунке 4.8, в, можно увидеть, что при С = 1 триггер работает как повторитель (Q = D), а при переходе сигнала на входе С от логической единицы к логическому нулю триггер запирается и переходит в режим хранения (защелкивает информацию со входа D). В отличие от RS-триггера, D-триггер не имеет запрещенного состояния.

Статический синхронный триггер реагирует на входные сигналы в течение всего времени, пока тактовый сигнал С равен единице. Часто, однако, требуется триггер, в котором считываемая информация не передавалась бы непосредственно на выход, а появлялась там только тогда, когда все схемы уже заперты. Этим свойством обладают триггеры с динамическим управлением.

30