Некоммерческое акционерное общество

«АЛМАТИНСКИЙ УНИВЕРСИТЕТ ЭНЕРГЕТИКИ И СВЯЗИ»

Кафедра Электроника

Курсовая работа

По дисциплине «Цифровые устройства и микропроцессоры.»

Тема: «Проектирование устройства сбора данных»

Специальность 5В071900 – Радиотехника, электроника и телекоммуникации

Выполнил студент Исаков Ербол Группа РЭТ-12-12 «_____»__________________________2014г

Алматы 2014

Содержание

Введение 3

Техническое задание 4

1. Проектирование структурной схемы устройства сбора данных(УСД) 5

2. Программа работы УСД 8

2.1. Алгоритм работы устройства 8

2.2. Составление программы на языке ассемблера и её размещение в ОЗУ 10

3. Оценка быстродействия устройства 1

Заключение 15

Список использованной литературы 16

Введение

Курсовая работа по дисциплине «Цифровые устройства и микропроцессоры» предназначена для того, чтобы студент получил навыки схемотехники, организации и программирования микрокомпьютеров. Данная работа показывает все возможности данной дисциплины в области телекоммуникаций. Задачей курсовой работы является углубление знаний, полученных при изучении курса, а также развитие навыков самостоятельной работы с технической и справочной литературой. Основная задача — это разработка функционально законченного устройства для обработки входных сигналов линии с использованием цифровых устройств и аналого-цифровых узлов.

Техническое задание

Спроектировать устройство сбора данных (УСД), которое должно работать следующим образом: последовательно опрашивая аналоговые сигналы, поступающие на F входов коммутатора каналов (КК), необходимо с помощью аналогово-цифрового преобразователя (АЦП) преобразовывать эти сигналы в цифровую форму (двоичные слова разрядностью 1 байт = 8 бит) и разместить их в некоторую область оперативного запоминающего устройства (ОЗУ), начиная с ячейки, имеющей адрес с символическим названием «М».

УСД имеет в своём составе ОЗУ ёмкостью Q = N*n (N ячеек с разрядностью n) и форматом адресного слова 2 байта = 16 бит. Синхронизация работы микропроцессорной системы (МПС) осуществляется от генератора тактируемых импульсов (ГТИ). Частота синхронизации f = 500 кГц.

Исходные данные:

Число входов коммутатора каналов F=14

Текущий адрес очередного канала должен храниться в регисторе R=D

Область оперативного запоминающего устройства (ОЗУ) М=03Е5

Ёмкость ОЗУ Q=1024

8

8Программа будет размещаться в памяти начиная с ячейки с адресом BEG=071А

Требуется:

а) Проработать вопрос организации ОЗУ;

б) Реализовать УСД в виде микропроцессорного устройства, выполненного на основе 8-разрядного МП. При этом текущий адрес очередного канала должен храниться в регистре R. Микропроцессорное устройство необходимо довести до уровня структурной схемы, составить программу его функционирования на языке ассемблера, представить таблицу размещения программы в памяти, начиная с ячейки с адресом BEG, а также оформить программу в кодовых комбинациях (на машинном языке);

в) Оценить быстродействие УСД.

Проектирование структурной схемы устройства сбора данных (УСД)

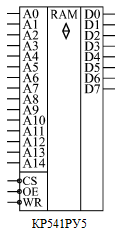

По заданию необходимо организовать ОЗУ имеющее объём памяти 32768х8 бит. Это значит 1024 ячеек разрядностью 8 бит. Выберем микросхему КР541РУ5 с организацией 1K×8 для ОЗУ. Она содержит 1K ячеек с разрядностью 8 бит.

Рассчитаем количество микросхем необходимое для данного объёма памяти по формуле:

Где МТ – требуемая ёмкость ОЗУ, М1 – ёмкость одной микросхемы.

Для микросхемы количество адресных входов А=15, так как 215 обеспечивает адресацию 1024 ячеек памяти разрядностью 8 бит.

Приведем условное графическое обозначение микросхемы КР541РУ5.

Рисунок 1 – Условное графическое обозначение

микросхемы KP541PУ5

A0 – A14 –адресные входы;

D0 – D7 – вход и выход данных;

CS – вход выбора микросхемы;

OE – вход разрешения выходов;

WR – вход разрешения записи.

Блок управления осуществляет синхронизацию работы микросхемы в режимах выборки, записи, считывания. На блок управления подаются сигналы CS,OE,WR.

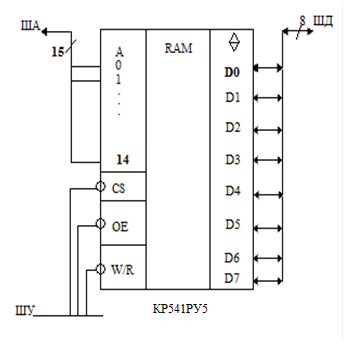

Рисунок 2 – Схема построения ОЗУ.

ШУ – шина управления;

ШД – шина данных;

ША – шина адреса.

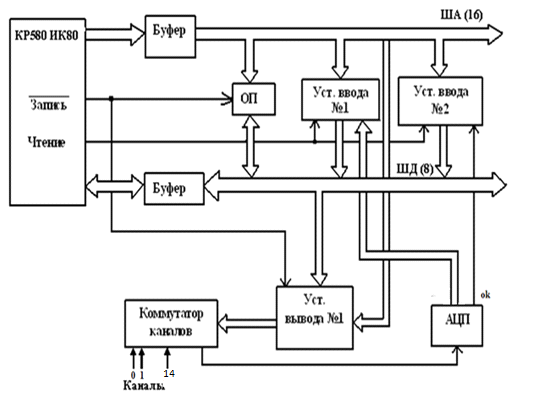

Рисунок 3. Структурная схема УСД.

Структурная схема УСД, построенного в виде микропроцессорного устройства (МПУ), представлена на рисунке 3. Кроме микропроцессора (МП), аналого-цифрового преобразователя (АЦП), оперативной памяти (ОП) и коммутатора аналоговых каналов (КАК), схема МПУ содержит два устройства ввода и одно устройство вывода данных, роль которых могут выполнять программно-управляемые регистры-порты, например, многорежимные буферные регистры (МБР) К589ИР12. В таком варианте МПУ и шина управления может состоять всего из двух линий: ЗАПИСЬ и ЧТЕНИЕ.

На схеме рисунка 3 для простоты не показаны: триггер-флаг АЦП (Тфл) и дешифратор сигналов выборки модуля ОП(CS).