- •Содержание

- •Часть 1 3

- •Часть 2 50

- •Часть 1

- •1. Микропроцессоры. Определение, классификация, закономерности развития, области применения. Обобщенная структура микропроцессора

- •2. Арифметико–логические устройства. Структура, подход к проектированию, основные уравнения работы алу

- •3. Организация цепей переноса в пределах секции алу. Наращивание разрядности, схема ускоренного переноса

- •4. Регистровое алу – базовая структура микропроцессора. Варианты построения регистровых структур. Задача управления и синхронизации

- •7. Устройство микропрограммного управления. Структура, способы формирования управляющих сигналов, адресация микрокоманд

- •8. Система команд и способы адресации операндов. Конвейерный принцип выполнения команд

- •9. Структурные конфликты и способы их минимизации. Конфликты по данным, остановы конвейера и реализация механизма обходов

- •10. Сокращение потерь на выполнение команд перехода и минимизация конфликтов по управлению

- •11. Классификация систем памяти. Организация систем памяти в микропроцессорных системах

- •12. Принципы организации кэш-памяти. Способы отображения данных из озу в кэш-память

- •13. Режимы прямого доступа к памяти. Структуры контроллеров пдп

- •14. Принципы функционирования виртуальной памяти

- •15. Типовые структуры и принципы функционирования микропроцессорных систем

- •16. Основные режимы функционирования микропроцессорной системы. Выполнение основной программы, вызов подпрограмм

- •17. Основные режимы функционирования микропроцессорной системы. Обработка прерываний и исключений

- •18. Системы с циклическим опросом. Блок приоритетных прерываний

- •19. Обмен информацией между элементами в микропроцессорных системах. Арбитр магистрали

- •Часть 2

- •20. Классификация архитектур современных микропроцессоров. Архитектуры с полным и сокращенным набором команд, суперскалярная архитектура

- •21. Классификация архитектур современных микропроцессоров. Принстонская (Фон-Неймана) и гарвардская архитектуры

- •22. Структура современных 8-разрядных микроконтроллеров сRisc-архитектурой

- •22(?). Структура современных 32-разрядных микроконтроллеров сRisc-архитектурой

- •23. Процессоры цифровой обработки сигналов: принципы организации, обобщенная структура

- •24. Процессоры общего назначения на примере архитектурыIntelP6

- •25. Классификация архитектур параллельных вычислительных систем. Системы с разделяемой общей памятью

- •26. Классификация архитектур параллельных вычислительных систем. Системы с распределенной памятью

- •27. Векторно-конвейерные вычислительные системы. Память с расслоением. Особенности структуры системыCray-1

- •28. Матричные вычислительные системы. Особенности построения систем памяти и коммутаторов

- •29. Машины, управляемые потоком данных. Принципы действия и особенности их построения. Графический метод представления программ

- •30. Системы с программируемой структурой. Однородные вычислительные среды

- •31. Систолические вычислительные системы

- •32. Кластерные вычислительные системы: определение, классификация, топологии

2. Арифметико–логические устройства. Структура, подход к проектированию, основные уравнения работы алу

Арифметико-логическое устройство непосредственно выполняет микрооперации над исходными операндами. Формально АЛУ — это комбинационная схема (КС), предназначенная для выполнения арифметических и поразрядно-логических операций над многоразрядными словами. Напомним, чтокомбинационной называется схема, состояние выходных сигналов которой однозначно определяется набором входных сигналов; такая схема не содержит элементов памяти.

В общем случае к АЛУ предъявляются следующие требования:

∙ выполнение арифметических и логических операций; разнообразие данных операций обеспечивает набор команд, которые сможет выполнять микропроцессор;

∙ обеспечение межразрядного переноса при выполнении арифметических операций, от этого во многом зависит быстродействие вычислительной системы;

∙ обеспечение наращивания разрядности обрабатываемых слов однотипными секциями.

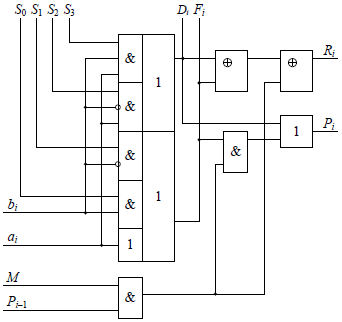

Структура АЛУ на примере 4-разрядной секции:

Основой АЛУ является одноразрядный комбинационный сумматор SM, который изменяет конфигурацию в зависимости от управляющего слова S. Управляющее слово S входит в состав микрокоманды и определяет тип выполняемой операции. Сигнал M обеспечивает разделение арифметических и логических операций за счет запрета передачи арифметического переноса от секции к секции: при M = 1 выполняются арифметические операции, при M = 0 — логические. Pi — бит арифметического переноса, формируемый i-й секцией АЛУ; ai, bi — разряды многоразрядных операндов A и B; Ri — разряды результата R.

Работу одноразрядного комбинационного сумматора можно описать выражением:

![]()

Данное выражение удобно использовать при анализе логических операций, в случае анализа арифметических операций его можно представить тождественным выражением:

![]()

Данные выражения содержат четыре управляющих переменных, посредством которых можно определить шестнадцать различных операций. Количество операций удваивается, поскольку с помощью сигнала Mмы разделяем шестнадцать логических и шестнадцать арифметических операций. Результат арифметической операции зависит от значенияP0, т. е. существуют два разных результата арифметической операции (приP0= 0 иP0= 1). Таким образом, данные выражения позволяют построить АЛУ, выполняющее 48 операций.

3. Организация цепей переноса в пределах секции алу. Наращивание разрядности, схема ускоренного переноса

Структура секции АЛУ:

Рассмотрим структуру секции АЛУ, представленную на рисунке и функционирующую согласно выражению:

![]()

![]()

Объединение нескольких подобных секций в операционном устройстве требует организации цепей переноса. Быстродействие расширенного по разрядности АЛУ в большой степени зависит от способа организации цепей переноса внутри секции и между секциями. Внутри секции могут быть предложены два способа переноса: последовательный (сквозной) и параллельный.

При последовательном (сквозном)переносе в каждой секции АЛУ формируется сигнал переноса на основании подготовительных функций и сигнала переноса из предыдущей секции в соответствии с выражением:

![]()

Время распространения переноса по всей схеме равно ntn, где n — число разрядов в секции; tn — время распространения переноса через одну секцию (разряд). Таким образом, схема с последовательным переносом характеризуется относительной простотой. Использовать последовательный перенос целесообразно, когда нет необходимости в высоком быстродействии, но предъявляются жесткие требования к аппаратным затратам.

Параллельный перенос обеспечивает более высокое быстродействие, но требует больших аппаратных затрат. При этом все сигналы переноса формируются параллельно на основании подготовительных функций в соответствии с выражением:

![]()

![]()

Для 4-разрядной секции АЛУ имеем следующую систему выражений:

где D1,F1— подготовительные функции первого порядка, использующиеся для реализации межсекционного переноса. Из данной системы выражений видно, что каждый из сигналов зависит только от операндов и нулевого бита переноса, т. е. все они могут вычисляться одновременно, за счет чего и достигается увеличение производительности.

При наращивании разрядности между секциями обычно используют два способа организации цепей переноса: последовательный (сквозной) и групповой.

Последовательный (сквозной) перенос между секциями применим при малом числе связанных секций. В этом случае внутри секций, как правило, реализуют параллельный перенос. Суммарная задержка появления старшего бита переноса результата с момента поступления операндов и управляющих сигналов определяется как T = ntАЛУ, где tАЛУ — время формирования бита по переносу одной секцией АЛУ; n — число секций в системе.

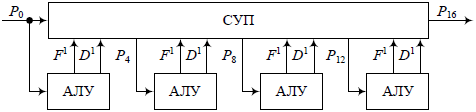

Схема организации последовательного (сквозного переноса):

![]()

Групповой перенос с помощью внешней схемы ускоренного переноса (СУП) целесообразно использовать при числе секций больше четырех. В этом случае в каждой секции формируются подготовительные функции первого порядка, поступающие на вход СУП. На основании этих функций в СУП формируются входные биты переноса для каждой секции. Суммарная задержка появления старшего бита переноса составляет T = tАЛУ+tСУП, где tСУП — время формирования результата СУП.

Схема организации группового переноса: