- •Содержание

- •Часть 1 3

- •Часть 2 50

- •Часть 1

- •1. Микропроцессоры. Определение, классификация, закономерности развития, области применения. Обобщенная структура микропроцессора

- •2. Арифметико–логические устройства. Структура, подход к проектированию, основные уравнения работы алу

- •3. Организация цепей переноса в пределах секции алу. Наращивание разрядности, схема ускоренного переноса

- •4. Регистровое алу – базовая структура микропроцессора. Варианты построения регистровых структур. Задача управления и синхронизации

- •7. Устройство микропрограммного управления. Структура, способы формирования управляющих сигналов, адресация микрокоманд

- •8. Система команд и способы адресации операндов. Конвейерный принцип выполнения команд

- •9. Структурные конфликты и способы их минимизации. Конфликты по данным, остановы конвейера и реализация механизма обходов

- •10. Сокращение потерь на выполнение команд перехода и минимизация конфликтов по управлению

- •11. Классификация систем памяти. Организация систем памяти в микропроцессорных системах

- •12. Принципы организации кэш-памяти. Способы отображения данных из озу в кэш-память

- •13. Режимы прямого доступа к памяти. Структуры контроллеров пдп

- •14. Принципы функционирования виртуальной памяти

- •15. Типовые структуры и принципы функционирования микропроцессорных систем

- •16. Основные режимы функционирования микропроцессорной системы. Выполнение основной программы, вызов подпрограмм

- •17. Основные режимы функционирования микропроцессорной системы. Обработка прерываний и исключений

- •18. Системы с циклическим опросом. Блок приоритетных прерываний

- •19. Обмен информацией между элементами в микропроцессорных системах. Арбитр магистрали

- •Часть 2

- •20. Классификация архитектур современных микропроцессоров. Архитектуры с полным и сокращенным набором команд, суперскалярная архитектура

- •21. Классификация архитектур современных микропроцессоров. Принстонская (Фон-Неймана) и гарвардская архитектуры

- •22. Структура современных 8-разрядных микроконтроллеров сRisc-архитектурой

- •22(?). Структура современных 32-разрядных микроконтроллеров сRisc-архитектурой

- •23. Процессоры цифровой обработки сигналов: принципы организации, обобщенная структура

- •24. Процессоры общего назначения на примере архитектурыIntelP6

- •25. Классификация архитектур параллельных вычислительных систем. Системы с разделяемой общей памятью

- •26. Классификация архитектур параллельных вычислительных систем. Системы с распределенной памятью

- •27. Векторно-конвейерные вычислительные системы. Память с расслоением. Особенности структуры системыCray-1

- •28. Матричные вычислительные системы. Особенности построения систем памяти и коммутаторов

- •29. Машины, управляемые потоком данных. Принципы действия и особенности их построения. Графический метод представления программ

- •30. Системы с программируемой структурой. Однородные вычислительные среды

- •31. Систолические вычислительные системы

- •32. Кластерные вычислительные системы: определение, классификация, топологии

23. Процессоры цифровой обработки сигналов: принципы организации, обобщенная структура

Процессор цифровой обработки сигналов (ПЦОС) (Digital Signal Processor — DSP) — это специализированный микропроцессор, обладающий архитектурными особенностями, которые востребованы в цифровой обработке сигналов. К таким особенностям относятся способ организации памяти, система команд, векторная и конвейерная обработка данных.

Отличительными особенностями задач цифровой обработки сигналов являются:

∙ высокая скорость поступления входных и выдачи выходных данных;

∙ широкий динамический диапазон данных;

∙ большое количество логических и арифметических операций;

∙ обеспечение гибкости и перестройки цифровых систем обработки сигналов;

∙ возможность параллельного выполнения алгоритмов.

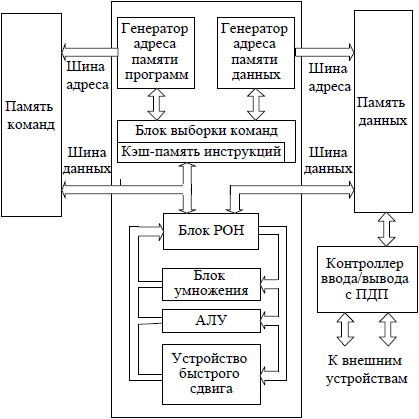

Обобщенная структура ПЦОС:

Обобщенная структура современных ПЦОС основана на VLIW-архитектуре системы команд и модифицированной гарвардской архитектуре памяти.Архитектура VLIW реализует распараллеливание обработки данных на этапе компиляции и позволяет не вводить в состав процессора дополнительный блок, отвечающий за обеспечение параллельно работающих исполнительных устройств полезной нагрузкой. Гарвардская архитектура применяется для повышения производительности и гибкости работы ПЦОС. Она подразумевает размещение программы и данных в раздельных запоминающих устройствах и их передачу по раздельным шинам, позволяет совмещать во времени выборку и выполнение команд. Модифицированная гарвардская архитектура допускает обмен содержимым между памятью программ и памятью данных, что расширяет возможности устройства.

В состав обобщенной структуры ПЦОС входят:

∙ генераторы адресов памяти программ и данных;

∙ разделенные блоки памяти команд и данных;

∙ блок выборки команд с кэш-памятью инструкций;

∙ блок РОН;

∙ блок умножения;

∙ арифметико-логическое устройство;

∙ контроллер ввода/вывода с ПДП;

∙ устройство быстрого сдвига.

Важной архитектурной особенностью ПЦОС является применение дублирующих (теневых) регистров для всех ключевых регистров центрального процессорного устройства. Эти регистры используются для быстрого выполнения прерываний. В традиционных микропроцессорах для выполнения прерываний требуется сохранение всех внутренних данных процессора. Обычно это реализуется путем записи содержимого всех регистров в стек, причем на запись содержимого каждого регистра в стек требуется один машинный цикл. В ПЦОС с архитектурой SHARC прерывание выполняется после записи содержимого всех регистров процессора в течение одного машинного цикла.

24. Процессоры общего назначения на примере архитектурыIntelP6

Микропроцессоры общего назначения ориентированы на решение широкого круга задач цифровой обработки информации. Их основной областью применения являются персональные компьютеры, рабочие станции, серверы и другие системы массового применения. Расширение области применения таких микропроцессоров в основном достигается путем повышения их производительности и снижения энергопотребления.

Архитектура современных x86-совместимых процессоров Intel представляет собой усовершенствованную и дополненную функциональными устройствами архитектуру Intel P6. Рассмотрим особенности построения современных микропроцессоров общего назначения на примере архитектуры Intel P6.

Основные характеристики данной архитектуры:

∙ суперскалярный механизм исполнения инструкций с изменением их последовательности;

∙ суперконвейеризация;

∙ двухуровневый адаптивный статистический алгоритм предсказания ветвлений;

∙ двойная независимая шина.

Принципиальным отличием архитектуры P6 от предшественников является RISC-ядро, работающее не с инструкциями x86, а с простыми внутренними микрооперациями. Это позволяет снять множество ограничений набора команд x86, таких как нерегулярное кодирование команд, переменная длина операндов и операции целочисленных пересылок .регистр-память.. Кроме того, микрооперации исполняются не в той последовательности, которая предусмотрена программой, а в оптимальной с точки зрения производительности, применение трехконвейерной обработки дает возможность выполнять несколько инструкций за один такт.

Процессоры архитектуры P6 имеют конвейер длиной 12 ступеней. Это позволяет достигать более высоких тактовых частот по сравнению с процессорами, имеющими более короткий конвейер при одинаковой технологии производства.

Для того чтобы предотвратить ситуацию ожидания исполнения инструкции в архитектуре Intel P6 используется структура, называемая буфером предсказания переходов (Branch Target Buffer — BTB). В Intel P6 использован двухуровневый адаптивный статистический алгоритм, который регистрирует предысторию и предсказывает переходы.

Процессоры архитектуры P6 состоят из четырех основных подсистем:

∙ подсистемы упорядоченной предварительной обработки;

∙ ядра исполнения с изменением последовательности;

∙ подсистемы упорядоченного завершения;

∙ подсистемы памяти.

Подсистема упорядоченной предварительной обработки отвечает за выборку и декодирование инструкций в порядке, предусмотренном программой, и выполняет предсказание переходов.Исполнительное ядро с изменением последовательности операцийотвечает за выполнение микроопераций в оптимальном порядке и организует взаимодействие ОУ.Подсистема упорядоченного завершения выдает результаты выполнения инструкций в порядке, предусмотренном программой.Подсистема памяти осуществляет взаимодействие с оперативной памятью.