- •Содержание

- •Часть 1 3

- •Часть 2 50

- •Часть 1

- •1. Микропроцессоры. Определение, классификация, закономерности развития, области применения. Обобщенная структура микропроцессора

- •2. Арифметико–логические устройства. Структура, подход к проектированию, основные уравнения работы алу

- •3. Организация цепей переноса в пределах секции алу. Наращивание разрядности, схема ускоренного переноса

- •4. Регистровое алу – базовая структура микропроцессора. Варианты построения регистровых структур. Задача управления и синхронизации

- •7. Устройство микропрограммного управления. Структура, способы формирования управляющих сигналов, адресация микрокоманд

- •8. Система команд и способы адресации операндов. Конвейерный принцип выполнения команд

- •9. Структурные конфликты и способы их минимизации. Конфликты по данным, остановы конвейера и реализация механизма обходов

- •10. Сокращение потерь на выполнение команд перехода и минимизация конфликтов по управлению

- •11. Классификация систем памяти. Организация систем памяти в микропроцессорных системах

- •12. Принципы организации кэш-памяти. Способы отображения данных из озу в кэш-память

- •13. Режимы прямого доступа к памяти. Структуры контроллеров пдп

- •14. Принципы функционирования виртуальной памяти

- •15. Типовые структуры и принципы функционирования микропроцессорных систем

- •16. Основные режимы функционирования микропроцессорной системы. Выполнение основной программы, вызов подпрограмм

- •17. Основные режимы функционирования микропроцессорной системы. Обработка прерываний и исключений

- •18. Системы с циклическим опросом. Блок приоритетных прерываний

- •19. Обмен информацией между элементами в микропроцессорных системах. Арбитр магистрали

- •Часть 2

- •20. Классификация архитектур современных микропроцессоров. Архитектуры с полным и сокращенным набором команд, суперскалярная архитектура

- •21. Классификация архитектур современных микропроцессоров. Принстонская (Фон-Неймана) и гарвардская архитектуры

- •22. Структура современных 8-разрядных микроконтроллеров сRisc-архитектурой

- •22(?). Структура современных 32-разрядных микроконтроллеров сRisc-архитектурой

- •23. Процессоры цифровой обработки сигналов: принципы организации, обобщенная структура

- •24. Процессоры общего назначения на примере архитектурыIntelP6

- •25. Классификация архитектур параллельных вычислительных систем. Системы с разделяемой общей памятью

- •26. Классификация архитектур параллельных вычислительных систем. Системы с распределенной памятью

- •27. Векторно-конвейерные вычислительные системы. Память с расслоением. Особенности структуры системыCray-1

- •28. Матричные вычислительные системы. Особенности построения систем памяти и коммутаторов

- •29. Машины, управляемые потоком данных. Принципы действия и особенности их построения. Графический метод представления программ

- •30. Системы с программируемой структурой. Однородные вычислительные среды

- •31. Систолические вычислительные системы

- •32. Кластерные вычислительные системы: определение, классификация, топологии

21. Классификация архитектур современных микропроцессоров. Принстонская (Фон-Неймана) и гарвардская архитектуры

В 1946 году группа ученых под руководством фон Неймана опубликовала статью, в которой рассматривались принципы, по которым должны строиться компьютеры, а именно:

∙ двоичное кодирование;

∙ последовательное программное управление;

∙ однородность памяти;

∙ адресуемость памяти.

Принцип двоичного кодирования заключается в использовании двоичной системы счисления для построения цифровых вычислительных машин.

Принцип последовательного программного управления состоит в том, что арифметические устройства выполняют последовательно поступающие из памяти команды.

Принцип однородности памяти заключается в том, что программы и данные хранятся в одной и той же памяти, и неважно, что хранится в данной ячейке памяти – число или команда.

Принцип адресуемости памяти заключается в том, что память должна состоять из пронумерованных ячеек, причем к каждой из них должен быть обеспечен мгновенный доступ.

Архитектуру компьютеров, отвечающих этим принципам, называют принстонской, илифон Неймана. Однако обычно, когда говорят о принстонской архитектуре, речь идет о способе организации памяти, потому что большинство современных компьютеров отвечают принципам фон Неймана.

Согласно принципу адресуемости, память микросистемы представляет собой упорядоченный набор K-разрядных ячеек с произвольным доступом. Такая память называетсялинейной. Совокупность адресов памяти от 0 до 2n− 1, гдеn— количество двоичных разрядов адреса, называетсяадресным пространством. Обычно адресное пространство разделяется на два подмножества: пространство ввода/вывода и адресное пространство памяти. В этом случае ввод/вывод называютизолированным, в противном случае —совместным.

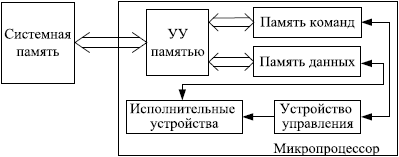

Структура вычислительной системы с принстонской архитектурой:

Характерной особенностью принстонской архитектуры является то, что в ее состав входит отделенная от исполнительных устройств общая память команд и данных. В системе с такой архитектурой исполнительные устройства и основная память соединены одним коммутационным трактом, передачи команд и данных разделены во времени. Достоинствами принстонской архитектуры стали гибкость вычислительной системы, простота реализации и отладки.

Простота отладки определяется наличием только одной системной шины. Однако в связи с увеличением производительности исполнительных устройств и ростом объема передаваемых данных единая системная шина стала ограничивать производительность таких систем.

В гарвардской архитектуре память команд и память данных физически разделены. Шины, соединяющие их с процессором, могут иметь как разную разрядность, так и разный объем памяти под команды и данные. Такое архитектурное решение дает выигрыш в быстродействии по сравнению с принстонской архитектурой, поскольку за один машинный цикл процессор может получить команды и данные.

Структура вычислительной системы с гарвардской архитектурой:

Основным недостатком гарвардской архитектуры является сложность технической реализации двух независимых шин, требующая дополнительных аппаратных затрат. Другим недостатком является то, что объемы памяти команд и памяти данных фиксированы, нет возможности динамически перераспределять информацию между ними.

В модифицированной гарвардской архитектуре эти недостатки устранены за счет использования общей памяти и общих шин данных и адреса для всей внешней информации. Внутри процессора применяются два модуля памяти с независимыми шинами адреса, данных и команд. Таким образом, сокращается количество физических линий, а также используется внешняя память для хранения как данных, так и команд.

Дальнейшим развитием гарвардской архитектуры является применение раздельной внутрикристальной кэш-памяти для команд и данных. Такая архитектура получила название расширенной гарвардской архитектуры (Super HArvard ARchitecture Computer — SHARC).

Структура вычислительной системы с модифицированной гарвардской архитектурой: