БАЗОВЫЕ СРЕДСТВА И АРХИТЕКТУРА

ЭВМ предназначена для автоматического решения задач пользователя и представляется совокупностью аппаратных, микропрограммных и программных средств, обеспечивающих возможность преобразования исходных данных в результат решения задачи.

software– программные средства

software– программные средства

firmware– микропрограммные

средства

firmware– микропрограммные

средства

hardware–

аппаратные средства

hardware–

аппаратные средства

Рис.1. Базовые средства ЭВМ.

Для понимания организации ЭВМ и принципов ее работы необходимы описания различной степени детализации.

Архитектура– это наиболее обобщенный уровень описания названных ранее средств. На архитектурном уровне описываются функциональные возможности, предоставляемые пользователю, указанными средствами и выделяются функциональные блоки. Составляются описания пользовательского интерфейса, системы команд, форматов данных и команд, способов адресации, программно доступных регистров.

На этом уровне описания излагаются модели вычислений и соответствующие этим моделям компоненты ЭВМ и правила сопряжения компонентов. Компоненты могут быть техническими, программными, информационными. Все компоненты должны удовлетворять принципу открытости, то есть иметь стандартизированный интерфейс (аналогично сетевым компонентам).

Архитектурный уровень описания раскрывает содержание понятий, воплощаемых базовыми средствами. Например, понятие процессора, драйверного интерфейса, системного и прикладного программного обеспечения. Излагаются архитектурные методы повышения производительности ЭВМ, например, методы конвейеризации вычислений, потоковый способ обработки информации.

При описании программных средств soft ware их подразделяют на прикладные и системные. Системное программное обеспечение служит для разработки программного продукта и предоставления услуг пользователю. Одной из компонент системного программного обеспечения является операционная система (ОС). ОС обеспечивает управление ресурсами (локальными и сетевыми) и взаимодействие пользователя с ЭВМ. Другими компонентами являются: система технического обслуживания, которая обеспечивает поиск неисправностей, учет статистики и др.; инструментальная система, предоставляющая интегрированные среды для разработки программного обеспечения, языки описания алгоритмов и др. Сервисная система предоставляет дополнительные услуги (архиваторы, утилиты).

Прикладным называют программное обеспечение, предназначенное для решения определенной целевой задачи, возникающей в различных областях человеческой деятельности. Например, для решения задач искусственного интеллекта в области медицины, военного дела или для обработки текстов в издательской деятельности.

Программные продукты в конечном виде представляются в ЭВМ последовательностью команд, алгоритм функционирования которых реализуется обычно микропрограммными средствами управления firm ware.Для реализации микропрограмм используются автоматные модели. Автоматы могут быть реализованы на логике, хранимой в ПЗУ или с помощью последовательностной логики, т.е. комбинационными схемами с регистровой памятью.

Обобщенный алгоритм функционирования ЭВМ включает в себя последовательность действий, осуществляемых при выполнении каждой команды. Если эти действия арифметические, то они выполняются в АЛУ, которое содержит свои локальные средства управления. ОЗУ, из которого извлекаются операнды для арифметических действий, также содержит свои локальные средства управления.

Микропрограммы обычно не доступны пользователю. Их назначение – обеспечить правильное функционирование аппаратуры – hard ware.

Микросхемы, являющиеся базой аппаратных средств, из которых строятся АЛУ, ОЗУ и другие устройства, подразделяются на стандартные, предназначенные для массового потребителя и специализированные, предназначенные для конкретного заказчика. Специализированные микросхемы могут быть заказными (полностью изготавливаемыми производителем), полузаказными (изготавливаемыми производителем путем настройки стандартных полуфабрикатов), и программируемыми пользователем, точнее реконфигурируемыми (модернизация микросхемы для нужд пользователя осуществляется с помощью САПР).

В виде микросхем реализуются запоминающие устройства, аналоговые и цифровые устройства.

Известны три вида архитектур процессоров, реализуемых в виде микросхем:

CISC(расширенный набор команд);

RISC(усеченный набор команд);

SISC(специализированный набор команд).

В микросхеме, реализующей процессор, объединены два базовых средства: аппаратура и микропрограмма.

ШИННАЯ ОРГАНИЗАЦИЯ ЭВМ

Базовые функциональные блоки объединяются в устройства, которые одновременно подключены к среде передачи информации, организованной в виде группы линий электрических соединений. Среду передачи информации называют системной шиной. Существуют различные реализации системной шины.

Среди устройств, подключаемых к системной шине, выделяют устройство памяти и центральное процессорное устройство (CPU). Архитектурный уровень описанияCPUвключает описание пользовательских возможностей программирования. АрхитектурыCPUсчитаются одинаковыми, если различныеCPUспособны выполнять одинаковые программы.

Данный уровень описания CPUпредусматривает:

описание доступных программисту средств хранения данных (регистры, память, порты ввода-вывода, стеки и др. компоненты);

указание набора операций (команд) над данными;

пояснение форматов команд и данных;

описание правил (алгоритмов) выполнения команд.

Реализация архитектуры может быть разная. Например, конвейерная и бесконвейерная. Современные процессоры имеют конвейерную реализацию, для понимания которой необходимо ясно представлять правила бесконвейерной обработки команд. Рассмотрим классическую структуру машины типа OKOD(1 поток команд – 1 поток данных) с шинной организацией, представленную на рис.2. Внешние устройства подключаются к системной шине с помощью специальных интерфейсных средств, обеспечивающих, в частности, возможность взаимодействия процессора и внешних устройств по запросу прерывания. Для обеспечения такого взаимодействия интерфейс содержит регистр, используемый для указания адреса вектора прерывания – АВП.

шина D

(данных)

шина D

(данных)

шина A

(адреса)

шина A

(адреса)

шина управления

шина управления

Процессор

INTR

Основная INT

Процессор

INTR

Основная INT

Интерфейс Регистр

Pг

адр. Рг дан.

память ввода

/ вывода АВП

Pг

адр. Рг дан.

память ввода

/ вывода АВП

INTA

INTA

RA RD Рг состояния Рг состояния

и управления и управления

Центральное

устройство

буфер пуст буфер

полон

Центральное

устройство

буфер пуст буфер

полон

управления

и

маска

маска &

управления

и

маска

маска &

11

7 6 0 00000 11 7 6

0 юооо00000

регистры управления

регистры управления

IP,IR,FR

Разрешение Разрешение

вывода

ввода

вывода

ввода

ALU и Pг-ры Занято Занято

локальн. УУ Буфер Буфер

выводимых

вводимых

выводимых

вводимых

данных

данных

данных

данных

операцион.

У

операцион.

У

8

8

8

8

Рис.2. Структура ЭВМ

В современных ЭВМ каждое внешнее устройство, подключаемое к системной шине, должно предоставить для ОС перечень системных ресурсов, которые оно потребляет. Состав этого перечня следующий. Диапазон адресов ввода-вывода (порты). Диапазон адресов оперативной памяти. Номера прерываний IRQ (Interrupt Request Line). Аппаратные линии (проводники) от периферийного устройства, по которым можно передавать сигналы (требования) прерывания, для обслуживания центральным процессором. Номера каналов DMA (Direct Memory Access). Обмен данными между устройством и оперативной памятью может осуществляться либо под управлением самого устройства (bus-mastering DMA или first-party DMA), либо под управлением системного DMA контроллера (slave DMA или third-party DMA). Идентификатор производителя (Manufacturer ID). Идентификатор типа устройства (Device type ID).

В первых ЭВМ выделение ресурсов производилось с помощью ручного выставления перемычек, определяющих настройку ресурсов. Такой способ конфигурирования порождает большое количество ошибок. Новые принципы построения шинных архитектур предусматривают автоматическое распознование и конфигурирование устройств. Согласно спецификации Plug and Play (PnP) устройства должны соответствовать определенным механическим и электрическим нормам и предоставлять операционной системе о себе идентификационную информацию.

Устройства должны обеспечивать возможность программной установки базовых ресурсов. ОС с помощью диспетчера PnP должна обнаруживать факты подключения и отключения устройства. Об изменениях аппаратной конфигурации подключаемые (или отключаемые) устройства и системная шина должны информировать ОС. Драйверы подключаемых устройств должны загружаться автоматически под управлением ОС. Предусматривается "горячее" (при включенном питании) подключение к ЭВМ аппаратуры. К программным компонентам ОС, обеспечивающим технологию PnP, кроме диспетчера PnP относятся диспетчер управления энергопитанием, системный реестр (база данных установленного аппаратного и программного обеспечений), Inf-файлы, в которых описаны устройства и местоположение в реестре информации об устройстве, драйверы устройств.

Архитектуры ЭВМ типа ОКОД имеют общие особенности:

Количество регистров значительно меньше количества ячеек памяти.

В любой момент времени только один элемент данных подлежит обработке.

Результат преобразования только один.

Выполняется только одна команда от начала до завершения. Местоположение очередной команды указывает специальный счетчик – указатель команд (IP). Линейную последовательность команд можно изменить с помощью специальных команд безусловного перехода и условного перехода и средствами прерывания.

Процесс выполнения любой команды можно представить в виде последовательности действий. Для конкретизации этих действий определим набор команд машины.

Пусть шины данных и адреса имеют одинаковый размер 16 линий, а все команды имеют размер 2 байта и следующий формат.

15 12 11 10 0 (разряд)

код операции способ

адресации адрес операнда

код операции способ

адресации адрес операнда

(КОП) (СА) (А) IR

При использовании прямого способа адресации обеспечивается доступ к оперативной памяти объемом 2048 байт. Косвенный способ адресации обеспечивает доступ к памяти объемом 2**16 байт. Для увеличения адресуемого пространства памяти целесообразно использовать сегментную и страничную организации памяти.

Для задания возможности обработки внешних прерываний и для описания свойств числового результата, полученного после выполнения команды, используется четыре младших разряда флагового регистра.

3 2 1 0

IFOFZFSFFR

Назначение флагов:

S– соответствует знаку операнда, полученного после арифметической операции. Плюс изображается нулем, а минус – единицей.

Z– единичное значение этого флага указывает на нулевой результат, полученный после выполнения текущей команды. Если значение флага нуль, то результат выполненной операции ненулевой.

О – указывает на переполнение регистра, в котором сохраняется результат арифметической команды. Нуль в этом разряде обозначает отсутствие переполнения, т.е. количество разрядов, требуемое для изображения результирующего операнда, не превышает количества разрядов соответствующего регистра.

I– единичное значение этого флага указывает на возможность обработки запросов на прерывание от внешних устройств.

ПЕРЕЧЕНЬ ИНСТРУКЦИЙ (КОМАНД)

Выбор системы команд определяется областью применения и совокупностью задач, для решения которых предназначена ЭВМ. Все команды можно разделить на две группы: команды, выполняемые устройством управления процессора и команды, выполняемые ALU.

Учитывая опыт программирования, определим минимальный набор команд, в который войдут команды обеих названных групп.

|

Мнемокод |

Код |

Операнд |

Назначение и действия |

Флаги |

|

|

1100 |

Rr |

Сложение с фиксированной точкой Акк Акк + Rr |

OF, ZF, SF |

|

|

1010 |

Rr |

Сложение с плавающей точкой Акк Акк + Rr |

OF, ZF, SF |

|

|

0011

|

Rd

|

Запись в память из Акк RAM(Rd) Акк |

None |

|

|

0100 |

Rr |

Чтение из памяти в Акк Акк RAM(Rr) |

None |

|

|

0101 |

K |

Безусловный переход IPK+IP |

None |

|

|

0001 |

K |

Условный переход If (S==1) then IP IP+K |

None |

|

JZ |

0010 |

K |

Условный переход If(Z==1)thenIP+K |

None |

|

|

0000 |

|

Останов Тп 0 |

None |

|

|

0110 |

|

Сброс флага IF I 0 |

IF

|

|

|

0111 |

|

Установка IF I 1 |

IF |

В таблице использованы следующие обозначения:

Акк – (аккумулятор) источник данных или приемник;

К – адресная константа, для задания которой выделены n+1 разрядов. Диапазон значений адресной константы: -2**nK+(2**n-1).

Rr– источник данных;

Rd– приемник данных.

Адрес операнда вычисляется в зависимости от используемого в команде способа адресации.

Так как учебный план дисциплины «Архитектуры ЭВМ» предусматривает разработку студентами курсового проекта, то в лекциях наряду с описанием архитектуры ЭВМ, включающим разъяснения принципа действия составных частей ЭВМ, рассматриваются вопросы проектирования компонентов ЭВМ, организации внутренней структуры и правил функционирования каждого компонента.

На очередном этапе проектирования после выбора перечня команд создаваемой ЭВМ разрабатывается регистровая модель CPU. Разработка заключается в детализации структуры ЭВМ, представленной в качестве исходной на рис.2

РЕГИСТРОВАЯ МОДЕЛЬ ЭВМ

Изобразим основные регистры и связи между ними, управляемые сигналами, поступающими из центрального устройства управления (УУ процессора). В алгоритме функционирования УУ процессора, описываемом на следующем этапе проектирования, предусматривается проверка значений признаков, поступающих на входы УУ процессора от исполнительных устройств и формирование управляющих сигналов, подаваемых на исполнительные устройства. Инициирование процесса формирования управляющих сигналов в УУ процессора осуществляется оператором путем установки триггера пуска (Тп) в единичное состояние. При переводе указанного триггера Тп в нулевое состояние УУ процессора проектируемой ЭВМ перестают формировать управляющие сигналы, ожидая появления единичного состояния триггера пуска Тп.

Приведенная на рис.3 модель содержит типовой набор регистров и устройств, обеспечивающих реализацию программного принципа управления.

Ready

ALU

ШД

Ready

ALU

ШД

Y10

S

ША

Y10

S

ША

R

T ALU

ШК

R

T ALU

ШК

ALU

&

УУ

Ai

R 0

Y7

&

УУ

Ai

R 0

Y7

АLU

ОУ

ALU RD RA

АLU

ОУ

ALU RD RA

Pi

Pi

Акк

Y6 Y9

V1

Акк

Y6 Y9

V1

Y5

IP

Y5

IP

SF

SF S V2 Y2

SF

SF S V2 Y2

ZF FR

ZF Z

ZF FR

ZF Z

OF

OF O Y8

OF

OF O Y8

STI

IF IF I

STI

IF IF I

CLI

CLI

Y4

Y4

Ready RAM

Ready RAM

RI КОП СА А

Ready

ALU Z S O INT

Ready

ALU Z S O INT

АО

АО

ЧТ

INTR WR RAM режим

ЧТ

INTR WR RAM режим

DС

ЗП

DС

ЗП

…УУ

Процессора RD

RAM

режим

…УУ

Процессора RD

RAM

режим

Y0

Y0

INTA

G

…

Y10

G

…

Y10

Пуск

Пуск

S

S

Тп

Тп

1 E R

E R

Y3

Рис.3. Регистровая модель гипотетического CPU

Далее приводятся пояснения некоторых обозначений, используемых для предоставления регистровой модели CPU.

Yi – сигналы, которые вырабатываются УУ процессора, подаются на исполнительные устройства.

Ai– сигналы, управляющие функционированием арифметических блоков.

RD – регистр данных, на который поступает содержимое ячеек основной памяти.

RA – регистр адреса памяти.

IP– регистр - указатель адреса очередной команды.

IR– регистр для хранения текущей команды.

RO, Акк – регистры для хранения обрабатываемых операндов.

ALU– арифметико-логическое устройство, управляемое локальным устройством УУ ALU, функционирование которого инициирует УУ процессора. Взаимодействие названных устройств управления осуществляется с помощью триггера TALU,единичное состояние которого свидетельствует о функционировании ALU (ReadyALU).

ReadyRAM - единичное значение этого сигнала свидетельствует о функционировании основной памяти в режиме записи или чтения.

ПОРЯДОК ФУНКЦИОНИРОВАНИЯ ЭВМ

Порядок функционирования устройств разрабатываемой ЭВМ представим в виде ГСА (граф-схема алгоритма). Центральное устройство управления (УУ процессора) реализуется в виде (МПА) микропрограммного автомата – firm ware.МПА вырабатывает последовательность управляющих сигналов, поступающих своевременно на устройства разрабатываемой ЭВМ с целью инициирования работы этих устройств.

Лист1

Рис. 4

КОСВЕННАЯ АДРЕСАЦИЯ(6 тактов) ВЫБОРКА ОПЕРАНДА (4 такта)

СОХРАНЕНИЕ (4 такта) АРИФМЕТИЧЕСКИЕ ОПЕРАЦИИ (3 такта)

ВЫБОРКА КОМАНД (8 тактов)

IFETCH

Пуск автомата V INIFETCH

Нет

TIFETCH

= = 1

TIFETCH

= = 1

Да

Да

ОЖ Y0

АЛГОРИТМ ФУНКЦИОНИРОВАНИЯ АВТОМАТА V(7 тактов)

Выборка команды

Нет

TIFETCH

= = 1

TIFETCH

= = 1

ОЖ Y0

Да

RA = IP V1

RDRAM V3

INIRAM V4

Нет Да

Ready RAM = = 1

RI = RD V2 ОЖ Y0

TIFETCH = 0 V5

6

Для организации прерываний от внешних устройств можно использовать типовой контроллер прерываний или упрощенную версию его реализации. Смотри на рис.2 интерфейс ввода-вывода, обеспечивающий формирование требования (запрос) прерывания (сигнал INT), подаваемого на вход INTR УУ процессора. Алгоритм функционирования CPU при обработке запроса прерывания представлен на рис.5. Прерываемое состояние флага IF может устанавливаться пользователем с помощью команд STI, CLI.

Рис. 5

Каждая программа обработки прерывания завершается командой IRET, выполнение которой обеспечивает возврат к прерванной программе для продолжения ее выполнения.

Для реализации алгоритма управления работой ЭВМ требуется аппаратное устройство управления. УУ (устройство управления) может быть реализовано; либо на основе хранимой логики, т. е. на основе устройства, хранящего последовательность микрокоманд, которые инициируют работу исполнительных блоков (операционных устройств - ОУ); либо на основе последовательностной логики, обеспечивающей реакцию на входные сигналы (признаки) в виде ответных управляющих сигналов, инициирующих работу операционных блоков. Причем реакция на текущее входное воздействие зависит от входных воздействий, поступивших ранее, т.е. последовательностная логика обладает памятью, реализуемой обычно с помощью триггерных схем. Устройство с памятью, выходные сигналы которого зависят от предыстории поступления входных сигналов, называется конечным автоматом.

Существуют правила перехода от графического описания алгоритма функционирования управляемого объекта к функциональной схеме аппаратного устройства управления.

Типовое устройство управления с хранимой логикой имеет структуру, представленную на рис. 6.

Рис. 6

Каждая микрокоманда соответствует описанию двух последовательно соединенных элементов ГСА: прямоугольника и ромба. При необходимости в исходную ГСА могут быть добавлены прямоугольники, отображающие тождественные преобразования, и ромбы, отображающие безусловные переходы.

НЕКОТОРЫЕ ОТЛИЧИЯ КЛАССИЧЕСКОЙ ЭВМ ОТ СОВРЕМЕННОЙ

1. Использование методов совмещения операций, выполняющихся в текущий момент. При этом используются два понятия: параллелизм (одновременность) и конвейеризация. Процессоры классифицируются по признаку поточности IиD(команд и данных) как системы ОКОД, ОКМД, МКОД, МКМД.

При параллелизме совмещения достигаются путем расщепления реализуемой функции на части, для вычисления каждой из которых используется отдельный аппаратный компонент. Все части функции вычисляются одновременно. Обрабатываемые операнды подаются на все аппаратные компоненты одновременно. Время функционирования каждого аппаратного компонента разное. Поэтому время вычисления функции определяется временем наиболее медленно функционирующего аппаратного компонента.

При конвейеризации функция расщепляется тоже на части, именуемые ступенями, для вычисления каждой части функции используется отдельный аппаратный компонент. Аппаратные компоненты последовательно соединены между собой. Обрабатываемые операнды перемещаются последовательно между ступенями, реализованными аппаратно, со скоростью, которая не зависит от количества ступеней, а зависит от времени прохождения одной ступени. Время вычисления функции определяется временем вычисления части функции, осуществляемого на одной ступени. Время вычисления, затрачиваемое на каждой ступени, одинаковое.

При реализации методов совмещения операций используются многопроцессорные архитектуры. Наиболее распространена симметричная многопроцессорная архитектура, предусматривающая использование понятия программного потока, которому выделяются вычислительные ресурсы.

2. Использование реконфигурируемых структур с целью повышения отказоустойчивости и построения систем высокой готовности (кластерная и сетевая архитектуры). Создание системы хранения (массив дисков, технология RAID).

3. Использование средств защиты. Теговые архитектуры предотвращают неправильное вмешательство пользователя в процесс работы ЭВМ. Существуют различные стратегии обеспечения безопасности. Разработаны стандарты обеспечения защиты.

4. Использование расширенных систем команд, обеспечивающих повышение скорости решения задач, возникающих в некоторых предметных областях. Например, для решения задач архивации, криптографии.

ВЗАИМОДЕЙСТВИЕ КЛАВИАТУРЫ И CPU

Программное. Контроллер клавиатуры имеет адресуемые порты (регистры).

С помощью системы прерывания.

В программе пользователя осуществляется обращение к клавиатуре с помощью функций BIOS,DOSили функции языка высокого уровня (C,Paskal).

Для идентификации клавиш, размещенных на поверхности клавиатуры, и действия (нажатие или отпускание), осуществляемого над клавишей, используются сканируемые (позиционные) коды клавиш. Сканируемый код клавиши представляется последовательностью, состоящей из одного или более 8-битовых чисел. Сканируемые коды назначаются также определенным комбинациям клавиш. Для обеспечения взаимодействия клавиатуры и CPU используется контроллер клавиатуры, соединяемый с клавиатурой средствами последовательного интерфейса, а взаимодействие контроллера с CPU осуществляется по параллельному интерфейсу.

Контроллер клавиатуры имеет порты 60h- 67h, из которых обычно используются порты 60hдля хранения данных или команд и 64hдля хранения состояния контроллера или команд упраления клавиатурой.

При каждом нажатии и отпускании клавиши выполняется аппаратное прерывание, имеющее номер N=9, АВП=9*4=24h. Данный вектор прерывания содержит адрес драйвера клавиатуры, входящего вBIOS:

24h:IP– адрес начала обработчика

26h:CS- адрес начала обработчика

26h:CS- адрес начала обработчика

Обработчик прерывания считывает из

порта 60hконтроллера

клавиатуры скан-код. Например, клавиша

имеет сканируемый код 75D,

клавиша - 77D,

Обработчик прерывания считывает из

порта 60hконтроллера

клавиатуры скан-код. Например, клавиша

имеет сканируемый код 75D,

клавиша - 77D,

- 80D, - 72D,Esc- 1D. Обработчик прерывания – это часть стандартно-

го драйвера BIOS. Этот драйвер формирует 2 байта из сканируемого кода, размещаемого в порте 60h, и посылает их в буфер (в ячейки памяти) клавиатуры. Адрес начала буфера 0040:001Eh. Первый формируемый байт должен содержать символьный кодASCII, сопоставленный с клавишей. Но некоторым клавишам не соответствует печатаемый символ. Например, ранее приведенным клавишам не соответствуют печатаемые символы. Если клавише не сопоставлен печатаемый символ, то в первом байте размещается 0 или префикс скан-кода, например,E0h, а во втором байте размещается расширенный ASCII код (часто совпадающий со скан-кодом). Для клавиш, которым соответствуют печатаемые символы, во втором байте формируется соответствующий скан-код, зависящий от действия, произведенного над клавишей. Для нажатой клавиши скан-код принадлежит множеству значений 01H-58H, а для той же отпущенной клавиши значение скан-кода увеличивается на величину 80Hи принадлежит другому множеству значений (81H–D8H).

При нажатии некоторых клавиш, например, PrintScreenили комбинации клавишCtrl+Alt+Delзапись в буфер клавиатуры не производится, а вызывается специальная процедура обработки.

Буфер клавиатуры, в который драйвер помещает два сформированных байта, устроен циклически. Программа пользователя может извлекать коды из буфера. Для этой цели используются функции BIOSa, либоDOSа. ВBIOSимеются три функции для работы с буфером клавиатуры. Вызов этих функций осуществляется с помощью команды прерыванияINTс номеромN=16H, задаваемой в программе пользователя. Например, функция 00HвBIOSосуществляет чтение очередного символа из буфера клавиатуры и удаление прочитанного символа из буфера. Если буфер пуст, то данная функция ожидает появления символа в буфере. Для выбора вызываемой функции нужно перед выполнением команды прерыванияINT16Hзанести в регистр АН номер функции. Результат выполнения функции размещается в регистрахALиAH. Если нажатой клавише соответствует обычныйASCII-код, то вALразмещаетсяASCII-код, а вAH– сканируемый код клавиши. Если нажатой клавише соответствует расширенныйASCII-код, то вALразмещается префикс скан-кода, например,E0hили 0, если префикса нет, а вAHразмещается расширенныйASCII-код.

В DOSимеется большее количество функций для работы с клавиатурой, чем вBIOS. Для вызова функцииDOSиспользуется регистр АН, содержащий номер функции, и командаINT21H. Результат выполнения функцииDOSразмещается вAL. ВDOSкаждая функция характеризуется тремя признаками:

Функция либо ожидает ввода символа в буфер, либо сразу выдает сообщение о том, что буфер пуст;

Функция либо выполняет эхо-печать, либо эхо-печать отсутствует;

Функция либо может быть прерванной другими функциями, например, 1BH, 23H (Ctrl_Break), либо нет.

Например, функция 01HвDOSожидает ввода символа в буфер, выполняет эхо-печать и может быть прервана.

Функция 08 – подобна функции 01, но без эхо-печати. Функция 07 обеспечивает ввод символа с ожиданием без эхо-печати и без проверки нажатия Ctrl_Breakдля прерывания.

Если клавише соответствует расширенный ASCIIкод, то в результате выполнения вызванной функцииDOSвALразмещается 0 или префикс скан-кода. Чтобы в регистреALполучить расширенныйASCIIкод клавиши, требуется повторное выполнение функцииDOS.

Определим основные компоненты программы, в которой используются средства прерывания DOS. Пусть требуется осуществить циклический вывод на экран символа "*". В теле цикла необходимо использовать функцию 07 прерыванияDOS, обеспечить возможность перемещения положения курсора при нажатии соответствующей клавиши и обеспечить возможность перемещения курсора на ограниченной плоскости экрана подобно перемещению вдоль большого или малого экваторов тора, разделенного на квадраты. Ограниченная плоскость представляется в виде разрезанного и развернутого тора. Выход из цикла и завершение программы осуществляется при нажатии клавишиESC.

Структура программы состоит из заголовка и тела. В заголовке приводятся необходимые директивы препроцессора, задаваемые на языке Cсимволом #, и имя главной функции, используемой в программе. Например:

# include<dos.h>

# includeESC27

voidmain(void)

В теле программы описываются операторы, размещаемые между двумя фигурными скобками. В качестве операторов используются операторы описания, присваивания, вызова функции и другие. Далее приводятся основные фрагменты программы.

{//объявление простых и структурных переменных

intx=30,y=10; //начальное положение курсора

union REGS in, out;

char temp, extend;

Далее описывается основной цикл программы, прекращаемый при нажатии ESC.

do

{

В данном операторе цикла следует использовать оператор очистки экрана, оператор печати символа * в заданной зоне экрана, вызов функции 07 прерывания DOSдля ввода кода, соответствующего нажатой клавише. Обработке подлежат только коды клавиш перемещения курсора иESC. Код нажатой клавиши помещается в переменнуюtemp. С помощью оператора выбораSWITCHанализируется код в переменнойtempи в зависимости от кода выполняется изменение координаты курсора. Выполняется проверка факта пермещения курсора за пределы заданной зоны на экране. Перед возвратом на начало цикла осуществляется задержка. Пример некоторых операторов приведен ниже.

in.h.ah=0x07;

int86(0x21, &in, &out);

if ((extend=out.h.al)= =0)

{//повторный вызов

in.h.ah=0x07;

int86(0x21, &in, &out);

}

temp=out.h.al;

switch (temp) // анализ ситуаций

{

case 77:x++; break;

case 75:x--; break;

case 80:y++; break;

case 72:y--; break;

}

delay(500); //оператор задержки delay(unsigned milliseconds)

}

while(out.h.al!=ESC);

}//конец программы.

Используемое в программе объединение REGSимеет следующее описание.

union REGS

{

struct WORDREGS x;

struct BYTEREGS h;

};

struct WORDREGS

{

unsigned int ax, bx, cx, dx;

unsigned int si, di, cflag, flags;

};

struct BYTEREGS

{

unsigned char al, ah, bl, bh;

unsigned char cl, ch, dl, dh;

};

Для вывода на экран печатаемого символа, например *, можно использовать стандартные функции clrscr(),gotoxy(x,y) иprintf("*\n").

Некоторые клавиши используются для изменения значения других клавиш, например, клавиши смены регистра (Ctrl, Shift, Alt) и клавиши- переключатели Caps_Lock, Num_Lock. Информация о состоянии названных клавиш хранится в ячейках 0040:0017Н и 0040:0018Н.

Функции языков высокого уровня используют функции BIOSaилиDOSa.

ОЦЕНКА ПРОИЗВОДИТЕЛЬНОСТИ ЭВМ

Определим время выполнения команд в классической модели и пути уменьшения этого времени. Для оценки времени выполнения команд в качестве единицы времени используется такт.

Таблица распределения времени выполнения команд

|

Название ступени (действия на ГСА) |

Тип команды | ||||

|

ADD |

WR |

JMP |

JS(да/нет) |

READ | |

|

IFETCH(выборка команды) |

8 |

8 |

8 |

8/8 |

8 |

|

DECODE(декодирование команды) |

1 |

1 |

1 |

1/1 |

1 |

|

TEST(проверка условия) |

- |

- |

- |

1/1 |

- |

|

EADDR(создание исполнительного адреса) |

6 |

6 |

- |

- |

6 |

|

OFETCH(выборка операнда) |

4 |

- |

- |

- |

4 |

|

EXEC(исполнение) |

3+1 |

1 |

- |

- |

1 |

|

CHANGEIP( изменитьIP) |

- |

- |

1 |

1/0 |

- |

|

STORE(сохранение) |

- |

4 |

- |

- |

- |

|

ENDOP(завершение) |

1 |

1 |

1 |

1/1 |

1 |

|

Итого: |

24 |

21 |

11 |

12/11 |

21 |

Для оценки производительности работы ЭВМ необходимо вычислить время, затрачиваемое на выполнение некоторой обобщенной команды. Для вычисления величины времени выполнения обобщенной команды используется формула, определяющая величину взвешенного арифметического среднего, которая позволяет учесть частоту использования каждой команды в заданной смеси команд.

X=

Xi– время (такты) выполнения командыi-го типа в заданной смеси команд;

Ci– дробная величина (доля). Характеризует частоту использования командыi-го типа в заданной смеси команд. Сумма всехNдолей составляет единицу.

В следующей таблице приведены доли затрат времени для каждой команды.

-

Тип команд

Доля общего времени

выполнения, %

ADD

40

READ

20

WR

15

JMP

5

Условный переход выполняемый

12

Условный переход невыполняемый

8

=100

На исполнение команды в бесконвейерной ЭВМ, реализованной по архитектуре OKOD, затрачивается в среднем 19,82 тактов. Ниже приведен расчет величины взвешенного арифметического среднего.

24*40=960 (тактов) ADD

21*20=420 (т) READ

21*15=315 (т) WR

11*5=055 (т) JMP

12*12=144 (т) УП выполняемый

11*8=088 (т) УП невыполняемый

Итого:1982:100=19,82 тактов.

Если частота тактирующих сигналов равна 20 мГц, то производительность бесконвейерной модели ЭВМ составляет 1 миллион операций в секунду.

ОРГАНИЗАЦИЯ КОНВЕЙЕРНОЙ ОБРАБОТКИ КОМАНД

При конвейеризации очередность команд, заданная программистом при написании программы, нарушается. Исполнения команд (текущей i-й иi+1-й) перекрываются во времени и возникают зависимости операций, запускаемыхi+1 иi+2 командами от результатовi-йкоманды. Эти зависимости вызывают помехи для выполнения команд. При конвейеризации необходимо обнаружить и устранить помехи.

С целью анализа возможности перекрытия команд целесообразно создать таблицу занятости для моделирования бесконвейерной структуры ЭВМ, используемой для выполнения команд. В структуре ЭВМ используется не расслоенная память RAM и бесконвейерное CPU. Когда функционирует память, тоCPUпростаивает и наоборот. В таблице занятости будет две ступени:RAMиCPU.

t

t

RAM

CPU

DECODE ENDOP

ADD

24 такта

EADDR

EXEC

|

|

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

X |

X |

|

|

|

X |

X |

|

|

|

|

|

|

X |

|

|

|

|

|

|

|

X |

X |

X |

X |

|

|

X |

X |

X |

|

|

X |

X |

X |

X |

X |

OFETCH

WR21 такт

|

|

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

X |

X |

|

|

|

|

X |

X |

|

|

X |

|

|

|

|

|

|

|

X |

X |

X |

X |

|

|

X |

X |

X |

X |

|

|

X |

JMP 11 тактов

|

|

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

|

|

X |

|

|

|

|

|

|

|

X |

X |

X |

JSпереход выполняется 12 тактов

|

|

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

X |

|

|

|

|

|

|

|

X |

X |

X |

X |

JSпереход не выполняется 11 тактов

|

|

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

X |

|

|

|

|

|

|

|

X |

X |

X |

READ 21 такт

|

|

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

X |

X |

|

|

|

X |

X |

|

|

|

|

X |

|

|

|

|

|

|

|

X |

X |

X |

X |

|

|

X |

X |

X |

|

|

X |

X |

Одним из путей уменьшения времени выполнения команд является совмещение операций. Используем метод простой предварительной выборки команды. Когда текущая команда выполняет последнюю часть своей работы в CPU, то можно выбирать очередную команду. При рассмотрении схемы выполненияADDможно увидеть возможность одновременного выполнения (перекрытия) двух команд без столкновений.

МЕТОД ПРЕДВАРИТЕЛЬНОЙ ВЫБОРКИ КОМАНД

Рассмотрим команды с целью анализа столкновений. Представим область определения каждой команды и результат ее выполнения в виде таблицы.

|

Команда (функция) |

Область определения |

Область значений |

|

ADD(тип) |

Операнд – ячейки памяти, регистр адреса для исполнительного адреса |

Акк,RD, регистр флагов |

|

STORE WR |

Ячейки памяти для исполнительного адреса, Акк,RD,RA |

Ячейки памяти операнда |

|

Jmp |

|

IP |

|

JS |

Условие (флаги) |

IP |

|

READ |

Операнд – ячейки памяти, ячейки памяти для исполнительного адреса, RA |

Акк,RD |

t

t

RAM

CPU

|

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

1 |

1 |

|

|

|

1 |

1 |

2 |

2 |

2 |

2 |

2 |

2 |

2 |

|

1 |

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

|

|

1 |

1 |

1 |

|

2 |

1 |

1 |

1 |

1 |

1 |

|

|

Предварительная выборка

+ + + + + + + +

-

2

2

2

2

3

3

3

3

3

3

3

2

22

2

2

2

2

2

3

2

2

2

2

2

базовый цикл латентности

Латентность – это число единиц времени (тактов), разделяющих инициации.

Метод выборки следующей команды во время завершения текущей называется предварительным. Он легко реализуется, но при исполнении команды нужно уметь выполнить выборку следующей команды. Могут возникать помехи, которые нужно устранить. Например, в команде JSне известен адрес. Помеха возникает, если к регистру, ячейке или к регистру флагов обращаются или модифицируют две различные команды так близко расположенные в программе, что при конвейеризации их исполнение перекрывается во времени.

Есть три класса таких помех:

Чтение после записи – RAW.

Запись после чтения – WAR.

Запись после записи – WAW.

Пример.

. . . . . . . . .

STORE X

STORE X

. . . . . . . . . RAW– используется «старое» значение вADD.

ADDX

ADDX

. . . . . . . . . WAR, еслиSTOREизменит X раньшеADD.

STOREX

STOREX

. . . . . . . . . WAW– второйSTOREизменитXраньше первого.

STORE

Когда пересекаются действия исполнения команды, то говорят о перекрытии действий.

|

|

|

|

|

Х |

Х |

|

|

|

Х |

Х |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

18 ADD |

|

|

Х |

Х |

Х |

|

|

Х |

Х |

Х |

+ |

+ |

Х |

Х |

Х |

Х |

Х |

|

|

E ADDRизменениеIP(RA)

ADDRизменениеIP(RA)

Для обеспечения предварительной выборки нужны дополнительные действия CPU: обновитьIPи передать его содержимое вRA.

|

|

|

|

|

Х |

Х |

|

|

|

|

Х |

Х |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

19 WR |

|

Х |

Х |

Х |

Х |

|

|

Х |

Х |

Х |

Х |

+ |

+ |

Х |

|

|

|

|

|

|

|

|

|

|

|

+ |

+ |

+ |

+ |

+ |

+ |

+ |

11 Jmp(Перекрытий действий нет) |

|

Х |

Х |

Х |

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

+ |

+ |

+ |

+ |

+ |

+ |

12 JS(Перекрытий действий нет. |

|

Х |

Х |

Х |

Х |

+ |

|

|

|

|

|

|

|

Переход выполняется.)

|

|

|

|

|

+ |

+ |

+ |

+ |

+ |

+ |

+ |

11 JS(Перекрытий действий нет. |

|

Х |

Х |

Х |

+ |

|

|

|

|

|

|

|

Переход не выполняется)

|

|

|

|

|

Х |

Х |

|

|

|

Х |

Х |

+ |

+ |

+ |

+ |

+ |

+ |

+ |

18 READ |

|

|

Х |

Х |

Х |

|

|

Х |

Х |

Х |

+ |

+ |

Х |

Х |

|

|

|

|

|

Средняя латентность: 18*40=720 ADD

18*20=360 READ

19*15=285 WR

11*5=055 Jmp

12*12=144 УП выполняется

1 1*8=088

УП не выполняется

1*8=088

УП не выполняется

1652:100=16,52

Уменьшение величины взвешенного среднего составляет:

1

9,82

1%=0,1982 3,30 0,1982

9,82

1%=0,1982 3,30 0,1982

1

6,52

х%=3,30 х=17%

6,52

х%=3,30 х=17%

3,30

Производительность повысилась на 17%. Стоимость дополнительной аппаратуры для предварительной выборки мала. Отношение стоимость/производительность весьма привлекательно. Поэтому во всех современных машинах реализуется метод предварительной выборки.

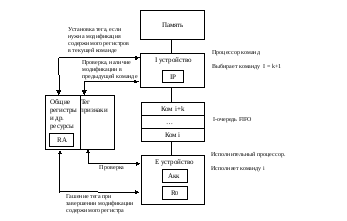

Усовершенствование конвейеризации

Большинство существующих способов конвейеризации основаны на использовании двух устройств, представляющих собой различные ступени конвейера. Одно из этих устройств называется I-устройство или командный процессор. Он служит для предварительной выборки команд.

Другое устройство - Е-устройство - служит для выполнения команд и называется исполнительным процессором.

Между ступенями помещается буфер для хранения очереди команд (I-очередь в буфереFIFO. В частном случае буфер может состоять всего лишь из одного регистра. Существует множество вариантов организации конвейера на базе названных устройств.

Рассмотрим простейшую структуру конвейера, в которой командный процессор выполняет функции IFETCHиENDOP.

Так как выборка команд может перекрываться с другими действиями, то целесообразно ее реализовать в виде одной ступени конвейера. В качестве другой ступени конвейера целесообразно использовать действия исполнения команды. Такое разбиение часто используется, и выделенные ступени имеют стандартные названия.

Рис. 7

I–устройство наращиваетIP, осуществляет выборку команд и помещает команду вi-очередь, если в ней есть место.

E-устройство осуществляет выполнение различных команд. При появление команды перехода (JMP,JE),E-устройство сигнализируетI-устройству которое очищаетI-очередь и перезагружаетIPзначением выработаннымE-устройством.

АЛГОРИТМ ФУНКЦИОНИРОВАНИЯ I И E-УСТРОЙСТВ

I-устройство, выполняет 1 цикл алгоритма за 7 тактов.

Рис.8

Рис.8

Время выполнения команд соответствует ранее рассчитанному времени. Для команд перехода время выполнения увеличится на 1 такт и в I-устройстве добавится еще такт для перезагрузки регистра IP.

E -устройство

-устройство

Рис.9

E– устройство не простаивает в ожидании команд, только при выполнении условного перехода происходит обращение к I-устройству для выборки команд.

Для представленной структуры конвейера с простым I-устройством (командным процессором) средняя латентность команд будет определяться следующим образом:EиI-устройства работают одновременно.

18*40=720 ADD

18*20=360 READ

19*15=285 WR

15*5=075 JMP(есть переход)

15*12=180 JS(переход выполняется)

7 *8=056JS(нет перехода)

*8=056JS(нет перехода)

1676

I-устройство: 7+1+7 – осуществляет выбор;

E-устройство: 7+1+7 – осуществляет выполнение;

Производительность возрастет на 17%.

Дополнительное увеличение производительности можно достичь, усложняя I-устройство. Например,I-устройство может вычислять исполнительный адрес команды перехода и делать предварительную выборку для команд условного перехода двух возможных следующих команд. После получения отE-устройства действительного адреса следующей команды будет известно, какую из предварительно выбранных команд нужно использовать.

ADD

ADD FADD

FADD WR

WR READ

READ Jmp

Jmp JS

JS HLT

HLT CLI

CLI StI

StI

Х

Х

Х

Х