Дополнительные вопросы

1. Пояснить назначение адреса вектора прерывания (авп) и правило формирования авп.

Ответ дан в разделе 2.4 «Средства управления прерываниями» в пояснительной записке к курсовому проекту.

2. Пояснить протокол взаимодействия алу с уу процессора.

Арифметико-логическое устройство (АЛУ), служащее ядром микропроцессора, как правило, состоит из двоичного сумматора со схемами ускоренного переноса, сдвигающего регистра и регистров для временного хранения операндов. Обычно это устройство выполняет по командам несколько простейших операций: сложение, вычитание, сдвиг, пересылку, логическое сложение (ИЛИ), логическое умножение (И), сложение по модулю 2.

Регистром называется электронная схема для временного хранения двоичной информации (машинного слова). Ее строят на триггерах, общее число которых определяет разрядность регистра. Каждый триггер регистра используется для ввода, хранения и вывода одного разряда (1 или 0) двоичного числа. Разрядность регистра выбирают соответственно длине хранимого в нем слова. Регистры, которые служат только для ввода, хранения и вывода двоичной информации, называют регистрами хранения. От них отличаются сдвигающие регистры, которые помимо выполнения указанных функций позволяют осуществлять сдвиг двоичного числа вправо или влево (а иногда – в обоих направлениях). Если в регистр хранения вводят числа в параллельном коде, то есть одновременно во все триггеры, то ввод чисел в сдвигающий регистр часто производят в последовательном коде, подавая последовательно один разряд за другим, хотя возможен и ввод чисел в параллельном коде.

Операндом называют число или символ, участвующие в машинной операции. Типичным примером операнда, используемого при процедуре обработки данных микропроцессором, служит байт.

Устройство управления (УУ) «руководит» работой АЛУ и внутренних регистров в процессе выполнения команды. Согласно коду операции, содержащемуся в команде, оно формирует внутренние сигналы управления блоками микропроцессора.

Схема соединения ALU, процессора и регистров общего назначения представлена на регистровой схеме в разделе 2.2, в разделе 2.3 приведен пример блок-схемы арифметической операции, выполняющейся на АЛУ.

3. Пояснить состав контроллера прерывания и протокол взаимодействия контроллера с центральным процессорным устройством.

Ответ дан в разделе 2.4 «Средства управления прерываниями» в пояснительной записке к курсовому проекту.

4.Указать этапы и пояснить результаты моделирования работы спроектированной ЭВМ, используя созданный алгоритм ее функционирования. Моделированию подлежит процесс выполнения команд READ #2, ADD #2, имеющих непосредственный способ адресации, а также команды READ [REG], имеющей косвенный способ адресации.

Моделирование READ [REG] и ADD 32 выполнено в разделе 4.2 в пояснительной записке к курсовому проекту.

Выполним моделирование READ 2.

READ 2, необходимо прочитать 2 и переместить в Акк.

-

Проверяем триггер пуска. Тп=1.

-

Проверяем условие INTR=1. INTR=0 прерывания нет.

-

Выборка очередной команды

-

Запись указателя на текущую инструкции в регистр адреса (RA←IP), сигнал V1

-

Ожидание готовности памяти (проверка ReadyRam = 1), сигнал Y0

-

Копирование инструкции из регистра RD →RI, сигнал V2

00100

10

0000000000000 0000 00000010

-

-

Проверка кода операции на равенство 00000. Код выбранной операции не равен 00000 и соответствует коду операции READ (00100)

-

Вычисление исполнительного адреса операнда. Способ адресации – непосредственная 10.

-

Перемещаем операнд RD = 0000000000000 0000 00000010, сигнал Y9

-

Так как. СА=10 выборка из памяти операнда не производится.

-

Перемещаем операнд 2 из RD в Акк, сигнал Y5

-

Увеличение указателя текущей команды IP=IP+4, сигнал Y2

-

Возврат в начало цикла (Тп=1).

-

WR2

5.Пояснить процесс выполнения команды JZ METKA.

Команда JZ Метка является условным переходом. Вначале как у любой другой команды происходит выборка IFETCH, затем декодирование команды, если команда определена как JZ, то далее выполняется проверка условия. При флаге ZF==1, то есть выставленный флаг равенства нулю, происходит смена адреса инструкции CHANGE IP на адрес указанной метки, то есть IP присваивается значение K(адрес метки). Если условного перехода не произошло, то происходит завершение команды ENDOP IP = IP +4.

6. Указать назначение таблицы описания страниц, ее размер, место размещения и формат указателя виртуального адреса.

Ответ дан в разделах 1.4.4 и 2.5 в пояснительной записке к курсовому проекту.

7. Пояснить, используя алгоритм обработки виртуального адреса, процесс выполнения команды ADD operand, имеющей символьное задание виртуального адреса. Для пояснения необходимо выбрать численное значение, соответствующее символьному адресу, учесть размер страницы и формат указателя виртуального адреса, используемые в проектируемой ЭВМ.

Ответ дан в разделе 2.5 в пояснительной записке к курсовому проекту.

8. Пояснить понятие латентности, используемое при анализе конвейерной обработки команд.

Латентность – это число единиц времени (тактов), разделяющих инициации. Ответ дан в разделе 3.2.

9. Перечислить функциональные возможности контроллера клавиатуры, демонстрируемые программой, созданной и отлаженной при выполнении лабораторной работы 1.

Ответ дан в разделе 5.1 в пояснительной записке к курсовому проекту

10. Пояснить отличие диапазонов представления чисел с фиксированной и плавающей точками, указать предельную абсолютную погрешность числа, представляемого в форме с фиксированной запятой n разрядами.

Ответ дан в разделах 1.4.2 и 1.4.3, где представлено графическое отличие указанных форматов

11. Пояснить понятие логического диска и один из существующих способов объединения множества дисковых носителей информации в один логический диск.

Логический диск или том — часть долговременной памяти компьютера, рассматриваемая как единое целое для удобства работы. Термин «логический диск» используется в противоположность «физическому диску», под которым рассматривается память одного конкретного дискового носителя.

Для операционной системы не имеет значения, где располагаются данные — на лазерном диске, в разделе жёсткого диска, или на флеш-накопителе. Для унификации представляемых участков долговременной памяти вводится понятие логического диска.

Один из способов объединения множества дисков, представляемых прикладной задаче как один логический диск, выполняется путем установки дисков в корпусе устройства ввода-вывода, которое подключается к файловому серверу по интерфейсу, например, IDE, SCSI, EIDE, SATA.

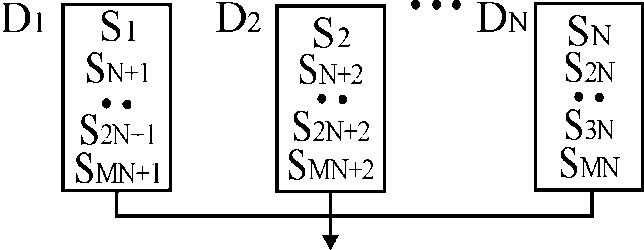

Самый простой способ объединения множества дисков в один логический диск – RAID 0, «чередование дискового массива без дополнительной отказоустойчивости», позволяет повысить производительность для прикладных программ при вводе-выводе данных большого объема. Данные, относящиеся к одному приложению, при хранении разбиваются на множество секторов (512 байт), и каждый сектор размещается на отдельном диске. ЭВМ воспринимает массив дисков как одно устройство хранения информации большой емкости.

Производительность повышается за счет того, что можно одновременно читать (или записывать) с (на) разных дисков.

При отказе одного диска, данные не восстанавливаются, и система перестает работать, но при такой организации данных достигается наивысшая производительность. Схема организации дисков, обозначаемых Di, и секторов Si на дисках представлена на рис. 1.

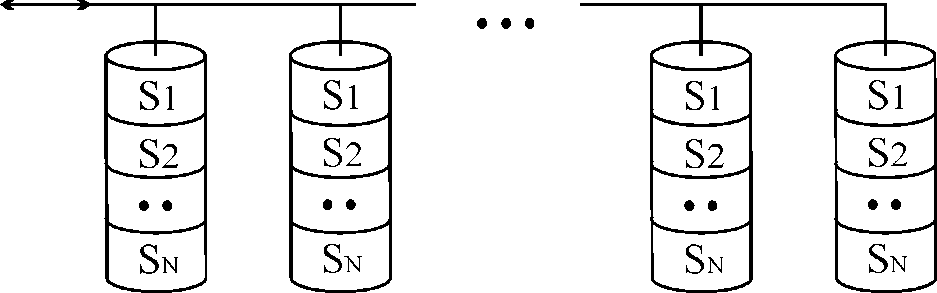

Для повышения надежности (отказоустойчивости) дискового массива используется дублирование дисков (уровень RAID 1). Для каждого диска используется резервный. Схема организации дисков представлена на рис. 2.

Достоинства способа:

-

Скорость записи на зеркальные диски равна скорости записи на один диск.

-

Скорость чтения в 2 раза выше.

-

Высокая скорость восстановления данных.

Недостатки:

-

Низкий коэффициент использования дискового пространства.

-

Неэкономичная схема хранения.

Уровень 0 и 1 целесообразно использовать для больших массивов данных, критичных к скорости чтения (записи) данных.

12. Известно, что передаваемая между техническими объектами информация обладает набором свойств. Правильность передачи информации можно контролировать, проверяя тождественность свойства передаваемой информации на источнике и приемнике. Указать свойство информации, наиболее часто используемое для контроля, и пояснить процесс осуществления контроля. Пояснить возможность использования для контроля кода Хемминга.

При передаче

информации из-за помех она может теряться

свои главные свойства: достоверность

и точность. Для проверки переданной

информации используют специальные

средства. Коды Хэмминга являются

самоконтролирующимися кодами, то есть

кодами, позволяющими автоматически

обнаруживать ошибки при передаче данных.

Для их построения достаточно приписать

к каждому слову один добавочный

(контрольный) двоичный разряд и выбрать

цифру этого разряда так, чтобы общее

количество единиц в изображении любого

числа было, например, четным. Одиночная

ошибка в каком-либо разряде передаваемого

слова (в том числе, может быть, и в

контрольном разряде) изменит четность

общего количества единиц. Счетчики по

модулю 2

![]() ,

подсчитывающие количество единиц,

которые содержатся среди двоичных цифр

числа, могут давать сигнал о наличии

ошибок.

,

подсчитывающие количество единиц,

которые содержатся среди двоичных цифр

числа, могут давать сигнал о наличии

ошибок.

При этом невозможно узнать, в каком именно разряде произошла ошибка, и, следовательно, нет возможности исправить её. Остаются незамеченными также ошибки, возникающие одновременно в двух, четырёх, и т.д. — в четном количестве разрядов. Впрочем, двойные, а тем более четырёхкратные ошибки полагаются маловероятными.

Любой код можно описать выражением (n, k), где

n – длина информационной посылки (вместе с контрольными разрядами);

k – количество информационных разрядов.

Для кода Хемминга это выражение имеет вид (2r – 1, 2r – r – 1), где

r – число проверочных разрядов, r = n – k.

Например, для 11 информационных разрядов необходимо 4 проверочных (r = 4). Для 4 информационных разрядов потребуется 3 контрольных. Отметим, что избыточность уменьшается при увеличении количества информационных разрядов.

Если к коду Хемминга добавить 1 разряд, то можно контролировать четность или нечетность кода. Такая модификация позволяет исправлять единичные ошибки и обнаруживать двойные.

Код Хемминга формируется путем добавления контрольных разрядов, каждый из которых обеспечивает четность (нечетность) количества единиц в соответствующей группе разрядов, в которую входит контрольный разряд.

1-ый контрольный разряд связан с группой информационных разрядов, номера которых представляются следующим двоичным кодом.

Х . . . Х Х 1,

где Х – произвольное значение 0 или 1, то есть разряды с нечетными десятичными номерами составляют группу: 1, 3, 5, 7, 9, … .

2-ой контрольный разряд связан с группой разрядов, двоичные номера которых имеют единицу во втором справа разряде.

Х . . Х 1 Х, т. е. группу составляют разряды с десятичными номерами: 2, 3, 6, 7, 10, … .

3-ий контрольный разряд связан с группой разрядов, двоичные номера которых имеют в 3-ем справа разряде единицу.

Х . . . Х 1 Х Х, т. е. номера десятичные: 4, 5, 6, 7, 12, … .

Значения контрольных разрядов устанавливаются такими, чтобы для соответствующих групп обеспечить четность (нечетность) количества единиц в группе. Если ошибка происходит в одном разряде, то оказывается возможным определить номер ошибочного разряда и произвести инвертирование его значения.