- •1.Основные понятия

- •2 Описание работы стенда

- •3 Указания по технике безопасности при работе со стендом.

- •Стенд включать в сеть только после ознакомления с его устройством и только по разрешению преподавателя;

- •4. Порядок выполнения работы

- •5. Содержание и оформление отчета

- •6.Контрольные вопросы.

- •Содержание

Цель работы: Знакомство с принципом работы мультиплексора и демультиплексора. Получение навыков работы по определению временных даграмм и составлению таблиц соответствия.

1.Основные понятия

Мультиплексоры и демультиплексоры - цифровые многопозиционные переключатели, по-другому, коммутаторы. Мультиплексоры предназначены для коммутации в желаемом порядке информации, поступающей с нескольких входных шин на одну выходную и преобразования параллельного кода, поступающего на информационные входы, в последовательный код на выходе. Мультиплексоры обладают двумя группами входов и одним, реже двумя взаимодополняющими выходами. Входы подразделяются на информационные, на которые непосредственно поступает код слова и служебные (управляющие), к ним относятся: адресные и разрешающие (стробирующие) входы. В зависимости от комбинации сигналов на адресных входах, происходит передача бита информации с одного из информационных входов на выход. Если мультиплексор имеет n адресных входов, то максимальное число информационных входов будет равно 2n. Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединён с выходным выводом.

Разрешающий (стробирующий) вход управляет одновременно всеми информационными входами независимо от состояния адресных входов. Запрещающий сигнал на этом входе блокирует действие всего устройства. Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Разрешающий вход употребляется также для наращивания разрядности мультиплексоров.

Демультиплексоры в функциональном отношении противоположны мультиплексорам. В демультиплексорах сигналы с одного информационного входа распределяются в желаемой последовательности по нескольким выходам, то есть происходит преобразование последовательного кода слова в параллельный. Выбор нужной выходной шины, как и в мультиплексоре, обеспечивается кодом на адресных входах. При m адресных входах мультиплексор может иметь, в зависимости от конструкции, до 2m выходов.

На Рис. 1 показана логическая структура мультиплексора “четыре линии к одной” (4:1). Она содержит четыре информационных входа D0-D3, два адресных входа Х1 и Х2 и разрешающий вход С. Вход Х1 принадлежит младшему разряду, Х2 - старшему. Когда разрешающий вход находится под высоким потенциалом Uвх (логическая единица), один из входов логических элементов “И” будет под низким и, следовательно, на их выходах также будут нулевые уровни независимо от состояния остальных входов. Выходной сигнал в этом случае также будет Y=0.

Рис.1 Логическая структура мультиплексора вида (4:1)

Схема управления выполнена так, что при разрешающем сигнале на входе С любые комбинации сигналов на адресных входах Х1 и Х2 создают условия, при которых на входах (а, значит, и на выходах) трёх логических элементов “И” существуют потенциалы низкого уровня, неактивные для элемента “ИЛИ”.

Состояние четвёртого элемента “И” и сигнала на выходе мультиплексора определяется сигналом на информационном входе. Двоичные числа (00; 01; 10 и 11), эквивалентны индексу задействованного информационного входа (D0; D1; D2; D3).

Так, например, двоичное число 10 на адресных входах обеспечит селекцию шины D2. У мультиплексоров, выпускаемых в виде отдельных микросхем, число информационных входов не превышает шестнадцати. Увеличение числа входов обеспечивается путём наращивания. Наращивание можно выполнять двумя способами: объединением нескольких мультиплексоров в пирамидальную (древовидную) систему, либо последовательным соединением разрешающих входов и внешних логических элементов. На практике применяют оба метода.

Пирамидальные мультиплексоры (Рис. 2) строятся по ступенчатому принципу, причём обычно применяются две, реже - три и более ступени. Пирамидальный характер схемы состоит в том, что каждая ступень, начиная с первой, имеет больше входов, чем последующая.

D

MS

Y

Х

D

MS Y

Х

D

MS Y

Х Y1 D0 D1 D3 D2 D4 D6 D5 Y2 D7 X2 X1 X3

Y

Рис.2 Пирамидальный мультиплексор вида (8:1)

Младшие разряды кода адреса подаются на адресные входы первой ступени, а ступеням более высокого ранга соответствуют старшие разряды адресного кода. Общее число информационных входов при однотипных мультиплексорах младшего ранга равно произведению числа входов отдельных мультиплексоров и числа самих мультиплексоров: Nвх.общ = Nвх*n.

Для очень больших Nвх.общ понадобится третий ряд мультиплексоров. Порядок их подключения не требует пояснений. Общее число входов определяется по той же формуле.

Недостатками пирамидального наращивания считается повышенный расход микросхем, а также невысокое быстродействие из-за суммирования задержек при последовательном прохождении сигналов по ступеням пирамиды. Логическая структура матричного демультиплексора представлена на рис. 3.

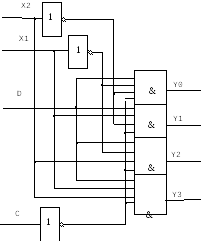

Рис.3 Логическая структура демультиплексора вида (1 : 4).

Здесь Х2 и Х1 - адресные входы, D - информационный вход, С - разрешающий. Схема управления выполнена также как, и у мультиплексора, только задача состоит в переключении одного входящего сигнала на один из четырех выходов.

У демультиплексоров, как и у мультиплексоров, увеличение числа входов обеспечивается путем наращивания.