lect4_m2_vt_mrtus_CS_niy37

.pdfТаблица 2.14

Реализация реверсивного сдвигового регистра (к примеру 2.14)

Номер |

a |

Q i+t |

1 |

Q ti |

Q it-1 |

Qi t+1 |

набора |

|

|

|

|

|

D* |

0 |

0 |

0 |

|

0 |

0 |

0 |

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

|

2 |

0 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

|

3 |

0 |

0 |

|

1 |

1 |

0 |

|

|

|

|

|

|

|

4 |

0 |

1 |

|

0 |

0 |

1 |

|

|

|

|

|

|

|

5 |

0 |

1 |

|

0 |

1 |

1 |

|

|

|

|

|

|

|

6 |

0 |

1 |

|

1 |

0 |

1 |

|

|

|

|

|

|

|

7 |

0 |

1 |

|

1 |

1 |

1 |

|

|

|

|

|

|

|

8 |

1 |

0 |

|

0 |

0 |

0 |

|

|

|

|

|

|

|

9 |

1 |

0 |

|

0 |

1 |

1 |

|

|

|

|

|

|

|

10 |

1 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

|

11 |

1 |

0 |

|

1 |

1 |

1 |

|

|

|

|

|

|

|

12 |

1 |

1 |

|

0 |

0 |

0 |

|

|

|

|

|

|

|

13 |

1 |

1 |

|

0 |

1 |

1 |

|

|

|

|

|

|

|

14 |

1 |

1 |

|

1 |

0 |

0 |

|

|

|

|

|

|

|

15 |

1 |

1 |

|

1 |

1 |

1 |

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

& |

1 |

i+1 |

& |

1 |

i |

& |

1 |

i-1 |

|

|

|

|

|

|

|||

TT |

|

D TT |

& |

|

D TT |

& |

|

D TT |

& |

|

C |

|

C |

|

C |

||

|

|

|

|

|

|

|||

C |

|

|

|

|

|

|

|

|

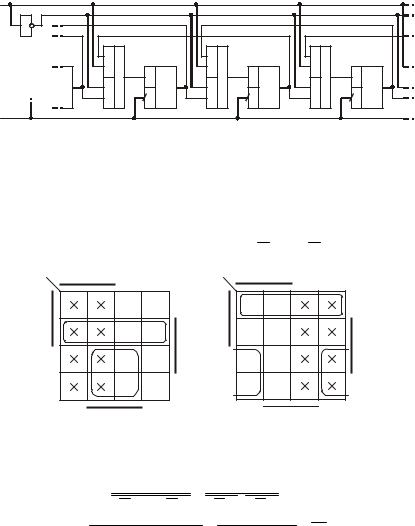

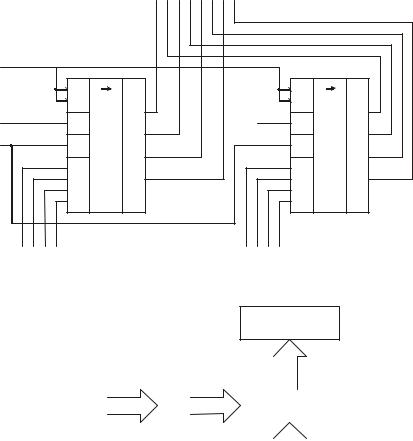

Рис.2.33. Фрагмент реверсивного сдвигового регистра

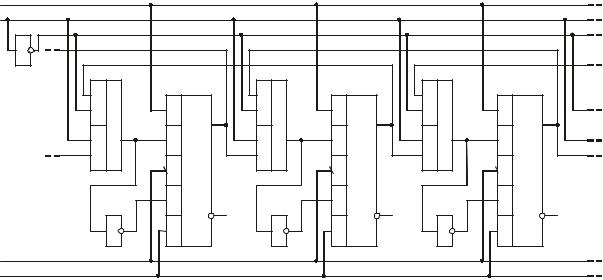

Пример 2.15. Разработать реверсивный сдвиговый регистр на универсальных JK-триггерах (типа 564ТВ1). Примем, что при а = 0 обеспечивается сдвиг влево (к старшим разрядам), а при а = 1 - вправо (к младшим разрядам). Функционирование такого регистра отражено в табл.2.15. Из рис.2.34 следует

|

J aQ |

aQ |

; |

K aQ |

1 |

aQ . |

(2.26) |

||

J* |

i |

i 1 |

i 1 |

|

i |

i |

i 1 |

|

|

Qi |

|

|

|

K* |

Qi |

|

|

|

|

a |

|

0 |

0 |

|

a |

1 |

1 |

|

|

|

1 |

1 |

|

0 |

0 |

|

|

||

|

|

|

|

|

|

||||

|

|

1 |

Qi+1 |

|

1 |

0 |

|

Qi+1 |

|

|

|

0 |

|

|

|

|

|||

|

|

1 |

0 |

|

|

1 |

0 |

|

|

|

|

Qi-1 |

|

|

|

|

|

Qi-1 |

|

|

|

а |

|

|

|

|

|

б |

|

|

|

Рис.2.34. Карты Карно: а - для J*; б - для K* |

|

||||||

УпростимвыражениедляKi , проделавочевидныепреобразования:

Ki aQi 1 aQi 1 aQi 1 aQi 1

(a Qi 1)(a Qi 1) aQi 1 aQi 1 J .

(2.27)

Фрагмент реверсивного сдвигового регистра на JK-триггерах приведён на рис.2.35.

Таблица 2.15

Реализация реверсивного сдвигового регистра (к примеру 2.15)

набораНомер |

a |

Q i+t |

1 |

Q ti |

Q it-1 |

Qi t+1 |

J* |

K* |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

|

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

|

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

|

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

7 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

8 |

1 |

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

9 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

10 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

11 |

1 |

0 |

|

1 |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

12 |

1 |

1 |

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

13 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

14 |

1 |

1 |

|

1 |

0 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

15 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

Уст. «0»

a

1

& |

1 |

|

i+1 |

|

|

||

|

|

R |

TT |

& |

|

J |

|

|

|

C |

|

|

|

K |

|

|

1 |

S |

|

|

|

|

C

& |

1 |

|

i |

|

|

||

|

|

R |

TT |

& |

|

J |

|

|

|

C |

|

|

|

K |

|

|

1 |

S |

|

|

|

|

& |

1 |

|

i-1 |

|

|

||

|

|

R |

TT |

& |

|

J |

|

|

|

C |

|

|

|

K |

|

|

1 |

S |

|

|

|

|

Уст. «1»

Рис.2.35. Фрагмент реверсивного сдвигового регистра

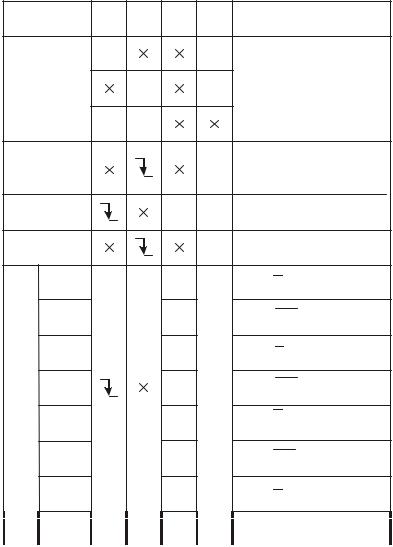

Пример 2.16. Разработать на JK-триггерах регистр, работающий в двух режимах: 1) при управляющем сигнале V = 0 должна осуществляться операция сдвига в сторону старших разрядов, 2) при V = 1 должна осуществляться параллельная загрузка регистра внешними данными.

Функционирование такого регистра отражено в табл.2.16, где Di - i-й разряд параллельного входного кода.

Из рис.2.36 следует

J VD |

VQ |

|

; |

K VD |

VQ . |

(2.28) |

||

i |

i |

i 1 |

|

i |

i |

i 1 |

|

|

J* |

Qi-1 |

|

|

|

K* |

Qi-1 |

|

|

0 |

|

0 |

|

|

V |

1 |

1 |

|

V |

|

1 |

|

|

0 |

0 |

|

|

1 |

|

Di |

|

Di |

||||

1 |

|

0 |

|

0 |

1 |

|||

|

|

|

|

|

||||

1 |

|

0 |

|

|

|

0 |

1 |

|

|

Qi |

|

|

|

|

|

Qi |

|

|

а |

|

|

|

|

|

б |

|

Рис.2.36. Карты Карно: а - для J*; б - для K* |

|

|||||||

Учитывая преобразования, проделанные в (2.27), можно записать

9 |

C1 |

RG |

|

|

|

8 |

|

|

|

||

C2 |

|

|

|

||

|

|

Q0 |

13 |

||

|

|

|

|||

1 |

|

|

|

|

|

DR |

|

12 |

|||

|

|

||||

|

|

Q1 |

|||

|

|

|

|||

6 |

V |

|

|

|

|

|

|

|

|

||

|

|

Q2 |

11 |

||

|

|

|

|||

2 |

|

|

|

|

|

D0 |

|

10 |

|||

|

|

||||

3 |

|

|

|||

D1 |

|

Q3 |

|||

4 |

|

|

|

||

D2 |

|

|

|

|

|

5 |

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

7 - 0 В ; 14 - + 5 В

Рис.2.37. Функциональное обозначение ИС типа К155ИР1, 555ИР1 и т.п.

Ki |

Ji |

. |

(2.29) |

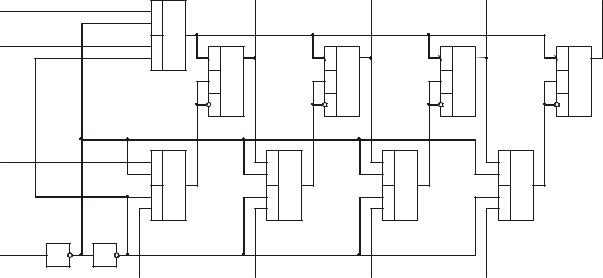

По уравнениям (2.28) и (2.29) реализована схема универсального регистра типа К155ИР1 (аналогичная схема реализована и в других сериях ИС). На рис.2.37 приведено функциональное обозначение этой ИС с указанием номеров выводов микросхемы, в табл.2.17 приведены режимы функционирования [19], а на рис.2.38 - полная схема регистра. Дополнительной особенностью ИС типа 155ИР1 является реализация независимых входов синхронизации для режима сдвига С1 и для режима параллельной загрузки С2, коммутация этих входов осуществляется входом установки режима V. Для большинства практических применений С1 = = С2, т.е. используется один синхросигнал.

Таблица 2.16

Функционирование регистра, работающего в двух режимах (к примеру 2.16)

Номер |

V |

Di |

Q |

Q t |

Q t+1 |

J* |

K* |

набора |

|

|

i-1 |

i |

i |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

8 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

10 |

1 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

11 |

1 |

0 |

1 |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

12 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

15 |

1 |

1 |

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2.17 |

|

|

Режимы функционирования ИС К155ИР1 |

|||||||

|

Режим |

С1 |

С2 |

DR |

V |

|

|

Примечание |

|

|

работы |

|

|

|

|||||

|

|

0 |

|

|

|

0 |

|

|

|

Хранение |

|

0 |

|

|

1 |

|

|

- |

|

|

|

|

|

|

|

|

|

||

|

|

0 |

0 |

|

|

|

|

|

|

|

Запись |

|

|

|

|

|

|

|

|

параллельного |

|

|

|

1 |

Код подаётся на входы Di |

||||

|

кода |

|

|

|

|

|

|

|

|

Сдвиг влево |

|

|

Вход |

0 |

Допускаются указанные |

||||

|

|

|

|

|

|

|

ниже соединения |

||

Сдвиг вправо |

|

|

|

|

1 |

Соединить: 2-12; 3-11; 4-10. |

|||

|

|

|

|

Вход - D |

|

||||

|

|

|

|

|

|

|

|

3 |

|

|

2 |

|

|

y2 |

|

y2 = Q0 |

|

||

|

3 |

|

|

y |

3 |

|

y = Q Q |

||

|

|

|

|

|

3 |

1 |

0 |

||

|

4 |

|

|

y |

|

|

y |

= Q |

|

на: |

|

|

|

4 |

|

4 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

Делитель |

5 |

|

|

y5 |

0 |

y = Q Q |

|||

|

|

5 |

2 |

1 |

|||||

6 |

|

|

y6 |

|

y6 = Q2 |

|

|||

|

|

|

|

|

|

|

|||

|

7 |

|

|

y |

|

|

y7 = Q3Q2 |

||

|

|

|

|

7 |

|

|

|

|

|

|

8 |

|

|

y8 |

|

y8 = Q3 |

|

||

|

. . . |

|

|

|

|

|

|

|

|

C1 |

& |

1 |

Q0 |

|

|

Q1 |

|

|

Q2 |

|

Q3 |

C2 |

& |

|

|

|

|

|

|

|

|

|

|

|

|

C |

TT |

|

C |

TT |

|

C |

TT |

C |

TT |

|

|

J |

|

|

J |

|

|

J |

|

J |

|

|

|

K |

|

|

K |

|

|

K |

|

K |

|

DR |

& |

1 |

& |

1 |

|

& |

1 |

|

& |

1 |

|

|

|

|

|

||||||||

|

& |

|

& |

|

|

& |

|

|

& |

|

|

V |

1 |

1 |

D0 |

D1 |

D2 |

D3 |

Рис.2.38. Схема универсального сдвигового регистра типа К155ИР1, 555ИР1 и т.п.

2.4.4. Организация цепей сдвига на несколько разрядов за один такт

Несмотря на большое разнообразие сдвиговых регистров, в ряде случаев их функциональных возможностей оказывается недостаточно. В первую очередь это относится к необходимости обеспечения сдвига за один такт на два или более разрядов. Последнее становится особенно необходимым при реализации арифметических операций в системах счисления с основанием, кратным двум, например в четверичной или шестнадцатеричной.

Аппаратная реализация сдвига данных на два и более разряда за один такт основана на использовании одного из следующих методов: пространственная перестановка разрядов; применение сдвигателей; применение мультиплексоров.

При использовании метода пространственной перестановки разрядов для построения регистров сдвига одновременно на k разрядов необходимо, чтобы общая длина регистра L была кратна произведению mk, где m - разрядность составляющих его регистров. Тогда процедура построения такого регистра будет следующая: обозначим через i номер входа регистра, а через im - номер того же входа по модулю m. В результате множество входных шин разбивается на k групп. Входные шины из одной группы подключаются в порядке следования их исходных номеров ко входам составляющего регистра с числом входов L/k. В свою очередь, последний может состоять из отдельных ИС, связанных по цепям сдвига последовательно между собой. ИС, соответствующие различным группам входов, связываются последовательными входами так же, как и в схеме сдвига на один разряд, но данные вводятся последовательным кодом, в котором разряды также пространственно переставлены. Номера выходов в регистре соответствуют номерам входов на нем. На рис.2.39 показан пример выполнения восьмиразрядного регистра со сдвигом на два разряда за один такт в сторону старших разрядов (влево).

Сдвигателем называется комбинационный узел ЭВМ, выполняющий микрооперацию сдвига данных на любое число разрядов за один такт. На рис.2.40 приведена обобщённая схема с использованием сдвигателя, где RG1 - регистр, в котором хранится n-разрядное число; m - максимальное число разрядов, на которое сдвигатель может сдвинуть данные за один такт; RG2 - регистр, в который записывается сдвинутое число с разрядностью n + m; RG3 - регистр, в котором хранится код с разрядностью log2(m + 1), определяющий число разрядов сдвига за один такт. Дешифратор DC преобразует последний код в m + 1 управляющие сигналы, обеспечивающие работу сдвигателя. Направление сдвига

определяется либо соответствующим пространственным подключением, |

||||||

либо мультиплексированием входных цепей RG2. |

|

|

||||

|

|

|

|

Q0Q1Q2Q3Q4Q5Q6Q7 |

|

|

C |

|

|

|

|

|

|

|

|

C1 |

RG |

|

C1 |

RG |

|

|

C2 |

|

C2 |

||

|

|

Q0 |

|

Q0 |

||

DR' |

DR |

DR" |

DR |

|||

|

|

Q1 |

|

Q1 |

||

V |

|

V |

|

V |

||

|

|

|

|

|||

|

|

Q2 |

|

Q2 |

||

|

|

D0 |

|

D0 |

||

|

|

D1 |

Q3 |

|

D1 |

Q3 |

|

|

D2 |

|

|

D2 |

|

|

|

D3 |

|

|

D3 |

|

|

|

D0D2D4D6 |

|

D1D3D5D7 |

|

|

|

Рис.2.39. Восьмиразрядный регистр сдвига со сдвигом на два разряда за один |

|||||

|

|

|

такт в сторону старших разрядов (влево) |

|

||

RG2 n+m

|

|

|

|

|

|

|

|

Y |

|

|

|

|

S |

|

|

|

|

|

|

RG3 |

|

DC |

Сдвигатель |

|

m |

||||

|

|

|

|||||||

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RG1 |

|

n |

|||

|

|

|

|

|

|

|

|

|

|

Рис.2.40. Обобщённая схема сдвига данных на основе сдвигателя

Уравнения для сдвигателя, предназначенного для сдвига от нуля до трёх разрядов 4-разрядного числа, имеют вид

y0 = S0x0;

y1 = S0x1 + S1x0;