lect4_m2_vt_mrtus_CS_niy37

.pdf

yi |

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qi |

|

|

|

|

|

|

|

|

|

|

|

|

|

yi |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

=1 |

|

|

|

|

|

||||||||

|

|

1 |

|

0 |

|

1 |

0 |

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qi |

|

|

|

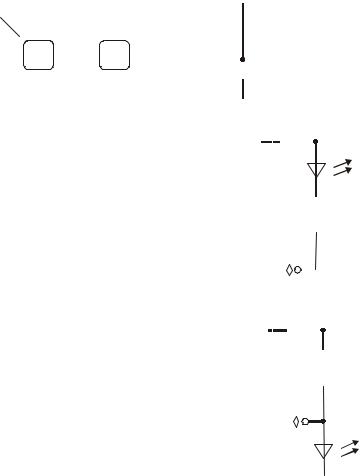

Рис.2.24. Управляемая выходная |

|||||||||||||||||||

|

Рис.2.23. Карта Карно для yi |

||||||||||||||||||||||||||

|

На рис.2.24 приведена соответствую- |

цепь регистра |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UИП |

||||||||||||

щая схема. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Отметим |

также, |

что управляющий |

|

|

|

|

VD |

|

|

|

|

|

|

|

|

|||||||||||

вход «Разрешение выхода» воздействует на |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

выходные буферы регистра. Он устанавли- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

вает их в третье состояние или закрывает |

|

|

|

|

|

|

|

|

|

|

|

|

R |

||||||||||||||

транзистор в схеме ОК и т.п. Наличие |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

управляющего входа и управляемого буфе- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

ра на выходе регистра существенно упро- |

Qi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

1 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

щает обмен данными между регистровыми |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

(yi) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

структурами и организацию регистров- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

файлов. |

|

|

состояния |

регистра |

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|||||||

|

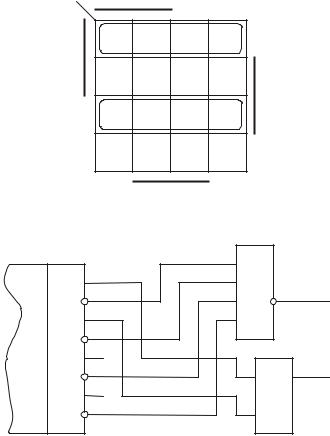

Цепи индикации |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UИП |

|||||||||

могут выполняться с различным уровнем |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

сложности. Простейшие цепи индикации |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

параллельного |

двоичного |

кода приведены |

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|||||||||||

на рис.2.25, где предполагается, что инвер- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

торы выполнены с открытым коллектором. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Для индикации всех состояний многораз- |

|

Qi |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

||||||||||||

рядного регистра применяются знакосинте- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

(yi) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

зирующие индикаторы различных модифи- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

VD |

|

|

|

|

|

|

|

|

||||||||||||||

каций |

с |

|

соответствующи- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

ми дешифраторами. Приме-ром |

сложной |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

системы индикации является так называе- |

|

|

|

|

|

|

|

|

|

|

б |

||||||||||||||||

мая «бегущая строка». |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

Пример 2.12. Для 4-разрядного парал- |

Рис.2.25. Фрагменты схемы |

|||||||||||||||||||||||||

лельного регистра разработать схему, выраба- |

индикации |

с применением |

|||||||||||||||||||||||||

тывающую два осведомительных сигнала: y1 |

светодиода |

при включении: |

|||||||||||||||||||||||||

должен указывать на нулевое состояние реги- |

а - от уровня «1»; б - от |

||||||||||||||||||||||||||

стра, y2 - на то, что состояние регистра мень- |

|

|

|

|

|

|

уровня«0» |

||||||||||||||||||||

ше или равно 3 либо больше или равно 12.

Длясигналовy1 иy2 обеспечитьактивныеуровни«0».

Табл.2.12 является таблицей истинности для сигналов y1 и y2. Для сигнала y1 удобно записать СКНФ, а затем преобразовать выражение к базису И-НЕ:

y1 Q3 Q2 Q1 Q0 |

Q3 |

|

Q2 |

|

Q1 |

|

Q0 |

. |

(2.19) |

Таблица 2.12

Реализация двух осведомительных сигналов о состоянии 4-разрядного параллельного регистра (к примеру 2.12)

|

|

|

|

|

|

|

|

|

Номер |

Q |

Q |

Q |

Q |

|

y |

y |

2 |

набора |

3 |

2 |

0 |

1 |

|

|||

|

|

1 |

|

|

|

|

||

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

8 |

1 |

0 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

10 |

1 |

0 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

11 |

1 |

0 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

12 |

1 |

1 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

15 |

1 |

1 |

1 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

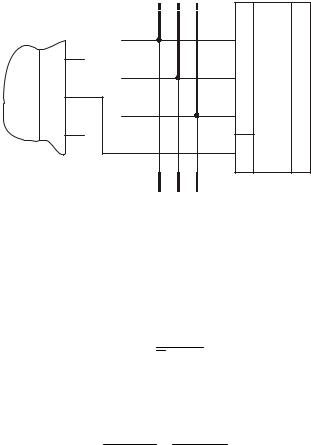

На рис.2.26 приведена карта Карно для сигнала y2, из которой сле-

дует

y Q3 |

Q2 |

|

Q3 |

Q2 Q3 Q2 . |

(2.20) |

Схема, реализующая осведомительные сигналы y1 и y2, приведена |

||||

на рис.2.27. |

y2 |

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

|

Q3 |

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

Q2 |

|

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

|

|

|

Q0 |

|

|

Рис.2.26. Карта Карно для сигнала y2 |

|||

RG |

Q3 |

|

Q2 |

|

Q1 |

|

Q0 |

&

y1

=1 y2

Рис.2.27. Схема реализации y1 и y2

|

a2 |

RG Qi+1 |

a1 |

Qi |

a0 |

|

|

Qi-1 |

|

DC y0

4y1 y2

y2

2y3 y4

y4

1y5 y6

y6

V y7

V y7

Рис.2.28. Схема передачи выходных данных в один из восьми приёмников

Пример 2.13. Разработать схему передачи данных с регистра на один из восьми приёмников. Для решения этой задачи необходимо использовать селектор «1 из 8-ми», в качестве которого можно взять стробируемый дешифратор «1 из 8-ми». Соответствующая схема приведена на рис.2.28. Поясним её работу. Для произвольного выхода yj дешифратора можно записать

~ ~ ~ |

, |

(2.21) |

y j Va2a1a0 |

где a~2a~1a~0 - произвольный адрес приёмника (от 0 до 7).

Пусть подан адрес 5, т.е. а2а1а0 = 101, учитывая, что V = Qi, для у5 можно записать

y5 |

Q |

ia2 |

a1 |

a0 |

Q |

i 1 |

0 |

1 Qi . |

(2.22) |

На остальных выходах дешифратора при этом адресе будет установлен уровень «1».

Очевидно, что передача данных с регистра на все восемь приёмников одновременно является тривиальной задачей - достаточно соединить параллельно одноименные входные линии всех приёмников и подключить их к соответствующим разрядам регистра.

2.3. Регистры-файлы (сверхоперативная память)

Сверхоперативная память содержит обычно небольшое число слов, имеет малое время доступа и часто входит непосредственно в состав арифметических устройств, где используется для хранения промежуточных данных в течение небольшого времени.

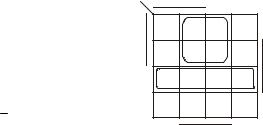

Например, в сериях ИС 533 и 555 есть ИС типа ИР26 (с тремя состояниями выхода) и ИР32 (с открытым коллектором на выходе), каждая из которых представляет собой регистровый файл, построенный как четырёхсловный по четыре разряда слово. Это обеспечивает раздельное декодирование и адресацию четырёх слов как для записи, так и для считывания данных и позволяет осуществлять одновременную запись по одному адресу и считывание - по другому. Наличие третьего состояния для ИС типа ИР26 (ОК для ИР32) позволяет соединять параллельно выходы большого числа регистров для записи и хранения n-четырёхсловных данных по четыре разряда слово. Структуру и режимы работы для указанных ИС см. в [16-18]. В серии 564 есть ИС типа ИР11 и ИР12, каждая из которых обеспечивает одновременное и независимое считывание двух слов. ИС 564ИР11 состоит из восьми четырёхразрядных регистров, включающих в себя: матрицу памяти, в которой каждый столбец образует отдельный регистр; дешифраторы адреса чтения первого и второго слова; дешифратор адреса записи и входной регистр. Вывод данных - параллельный через два независимых порта.

ИС 564ИР12 состоит из четырёх четырёхразрядных регистров и имеет аналогичную структуру. Выходы этой ИС трёхстабильные, что позволяет, например, строить на их основе буферные ЗУ, работающие непосредственно на магистраль коллективного пользования. Структуру и режимы работы для указанных ИС см. в [8].

2.4. Последовательные (сдвиговые) регистры

Последовательный (сдвиговый или сдвигающий) регистр - это регистр, содержимое которого при подаче тактового сигнала (управляющего сигнала «сдвиг») может сдвигаться в сторону старших или младших разрядов. Если регистр выполняется на непрозрачных триггерах, то управление сдвигом осуществляется однофазной синхронизацией. Сдвиговый регистр, выполненный на одноступенчатых защёлках, должен иметь двухфазную систему синхронизации.

В качестве основной элементарной операции сдвига слова применяется сдвиг на один разряд. Если необходимо слово сдвинуть на большее число разрядов, эта операция повторяется соответствующее число раз либо вводится специальная элементарная операция с использованием сдвигателей или других схемных решений. С помощью операции сдвига можно осуществить последовательную передачу слова: поразрядный ввод и поразрядную выдачу слова.

2.4.1. Организация цепей приёма и выдачи

Организация цепей приёма и выдачи данных в сдвиговых регистрах не отличается от процедур, аналогичных для параллельных регистров. Это относится как к последовательной, так и к параллельной загрузке и выдаче данных.

2.4.2. Организация цепей сдвига

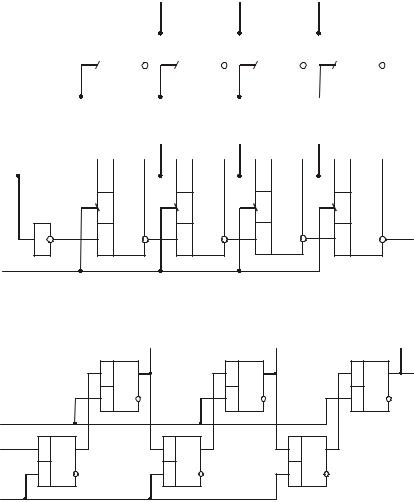

Рассмотрим сначала организацию цепей сдвига для случая однофазной синхронизации в предположении, что сдвиг производится влево (в сторону старших разрядов) на один разряд за один такт. Функционирование цепей сдвига представлено в табл.2.13 в обобщённом виде для двух различных типов триггеров (D и JK). Заполнение этой таблицы осуществляется с использованием соответствующих характеристических таблиц этих триггеров. Из рис.2.29 следует

D Q |

; |

(2.23) |

i i 1 |

|

|

Ji Qi 1;

(2.24)

Ki Qi 1.

Схемы соответствующих 4-разрядных регистров сдвига приведены на рис.2.30. Если сдвиговый регистр выполняется на одноступенчатых тактируемых триггерах, то он должен иметь двухфазную систему синхронизации. На рис.2.31 в качестве примера приведена схема сдвигового регистра на D-триггерах, осуществляющая сдвиг в сторону младших разрядов (вправо).

Таблица 2.13

Реализация сдвига в сторону старших разрядов регистра

|

|

|

Номер |

|

|

Q t |

Q t |

Q t+1 |

|

D |

* |

|

|

J * |

K |

* |

|

|

||||||||

|

|

|

набора |

|

|

i |

|

i-1 |

|

i |

|

|

|

i |

|

i |

|

i |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

0 |

|

0 |

|

0 |

0 |

|

|

0 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

|

1 |

|

1 |

|

|

1 |

|

|

1 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

1 |

|

0 |

|

0 |

0 |

|

|

|

|

|

1 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

1 |

|

1 |

|

1 |

|

|

1 |

|

|

|

|

|

0 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D * |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

i |

|

|

|

Qi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

|

|

|

0 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qi-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

J * |

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

* |

|

|

|

|

|

|

|

|

|

|

|

i |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Qi |

|

|

|

|

|

|

|

|

|

i |

|

|

|

|

Qi |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

1 |

|

0 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Qi-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qi-1 |

|||||

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в |

|||

Рис.2.29. Карты Карно: а - для Di*; б - для Ji*; в - для Ki*

|

|

|

|

|

Q0 |

|

Q1 |

|

|

Q2 |

|

|

Q3 |

|||||

DR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

TT |

|

D |

TT |

|

D |

TT |

|

|

D |

TT |

|

|

|||||

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

C |

|

|

C |

|

|

|

|

C |

|

|

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Q0 |

а |

Q1 |

|

|

Q2 |

|

|

Q3 |

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

DR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TT |

|

|

J |

TT |

|

J |

TT |

|

|

|

J |

TT |

|

|

|

|

|

|

J |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

||||||||||

|

C |

C |

C |

C |

1 |

K |

K |

K |

K |

|

||||

С |

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

Рис.2.30. 4-разрядные сдвиговые регистры: а - на D-триггерах; |

|

||||||

|

|

|

|

б - на JK-триггерах |

|

|

|

|

|

|

|

|

Q2 |

|

Q1 |

|

Q0 |

|

|

D |

T |

|

D T |

|

D |

T |

|

|

C |

|

|

C |

|

C |

|

C2 |

|

|

|

|

|

|

|

|

DL |

D |

T |

|

D |

T |

D |

T |

|

|

C |

|

|

C |

|

C |

|

|

C1 |

|

|

|

|

|

|

|

|

|

Рис.2.31. Сдвиговый регистр с двухфазной системой синхронизации |

|||||||

|

2.4.3. Организация цепей сдвига в реверсивных регистрах |

|||||||||

|

При двунаправленном сдвиге появляются два последовательных |

|||||||||

входа: вход, принимающий входные данные, вдвигаемые в регистр со |

||||||||||

стороны младшего разряда DR (data right - данные справа), и вход со |

||||||||||

стороны старшего разряда DL (data left - данные слева). Эти же входы |

||||||||||

используются и при наращивании разрядов регистра: последовательный |

||||||||||

вход DR старшей секции общего регистра подключается к выходу |

||||||||||

старшего разряда соседней младшей секции общего регистра; последо- |

||||||||||

вательный вход DL младшей секции общего регистра подключается к |

||||||||||

выходу младшего разряда соседней старшей секции общего регистра. |

||||||||||

|

Кроме последовательных входов сдвиговые регистры могут иметь |

|||||||||

входы параллельной загрузки за один такт и обязательно управляющие |

||||||||||

входы, определяющие режим работы сдвигового регистра. Для эконом- |

||||||||||

ного использования выводов микросхемы часто управляющие сигналы |

||||||||||

не вводят непосредственно, а формируют их с помощью дешифратора |

||||||||||

режимов. Другой приём упрощения структуры сдвигового регистра за- |

||||||||||

ключается в реализации цепей сдвига только в одном направлении, а |

||||||||||

для сдвига данных в другом направлении используется режим парал- |

||||||||||

лельной загрузки, для чего необходимо осуществить соответствующую |

||||||||||

коммутацию внешними соединениями между выходами разрядов реги- |

||||||||||

стра и входами параллельной загрузки. |

|

|

|

|

||||||

|

Рассмотримнесколько примероворганизациисдвиговых регистров. |

|||||||||

|

Пример 2.14. Разработать реверсивный сдвиговый регистр на универ- |

|||||||||

сальных D-триггерах (типа К155ТМ2). Так как регистр выполняет две мик- |

||||||||||

рооперации, то код микрооперации (управляющий сигнал а) будет одно- |

||||||||||

разрядным. Примем, что при а = 0 обеспечивается сдвиг вправо (к |

||||||||||

младшимразрядам), априа= 1 - влево(к |

D * |

|

|

|

||||||

старшим разрядам). |

Функционирование |

|

|

|

||||||

i |

Qi |

|

|

|||||||

такого регистра отражено в табл.2.14, где |

|

|

|

|||||||

Qi |

- произвольный разряд сдвигового |

0 |

1 |

1 |

0 |

|||||

регистра, Qi+1 и Qi-1 - соответственно |

a |

|

|

|

||||||

ближайший старший и младший разря- |

0 |

1 |

1 |

0 |

||||||

ды, |

|

- |

информационный |

вход i-го |

|

|

|

Qi+1 |

||

Di |

1 |

1 |

1 |

1 |

||||||

разряда. |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

|

Из рис.2.32 следует |

|

|

0 |

0 |

0 |

0 |

|||

|

|

D |

aQ |

aQ |

. |

|

|

|

|

|

(2.25) |

i |

i 1 |

i 1 |

|

|

|

|

Qi-1 |

|

|

|

|

|

|

сдвиго- |

Рис.2.32. Карта Карно для Di* |

|||||

|

Фрагмент реверсивного |

|

|

|

|

|||||

вого регистра на D-триггерах приведён на рис.2.33. |

|

|

|

|||||||