- •К.А. Палагута Микропроцессоры и интерфейсные средства транспортных средств

- •Москва 2011

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия 11

- •Глава 2 Режимы работы мпс 33

- •Глава 3. Реализация и организация памяти мп 57

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080) 77

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086) 138

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4 159

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus 209

- •Глава 8. Понятие и задачи интерфейса 239

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus 255

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле 308

- •Глава 11. Интегральные схемы программируемой логики (ис пл) 326

- •Предисловие

- •Введение

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия

- •1.1 Определение микропроцессора, классификация мп

- •1.2 Микропроцессорный комплект (мпк)

- •1.3 Микропроцессорная система

- •1.4 Линия, шина, магистраль

- •1.5 Типы магистралей

- •1.6 Шина адреса, раздельные и объединенные адресные пространства памяти и устройств ввода-вывода

- •1.7 Шина данных

- •1.8 Шина управления

- •1.9 Архитектура и структура микропроцессора

- •1.10 Cisc и risc процессоры, конвейерное выполнение команд программы

- •1.11 Конвейерная обработка данных

- •1.12 Контрольные вопросы и задания

- •Глава 2 Режимы работы мпс

- •2.1 Режим обмена данными под управлением процессора

- •2.2 Режим пдп

- •2.3 Режим прерывания

- •2.4 Контрольные вопросы и задания

- •Глава 3. Реализация и организация памяти мп

- •3.1. Виды запоминающих устройств (зу)

- •3.2. Кэш-память

- •3.3. Когерентность, механизмы сквозной и обратной записи

- •3.4. Алгоритмы обновления содержимого заполненных строк, снуппинг

- •3.5. Организация памяти

- •3.6. Внешние зу

- •3.7. Контрольные вопросы и задания

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080)

- •4.1 Структура мп к580вм80

- •4.2 Основные технические характеристики мп кр580вм80а

- •4.3 Регистровая модель мп к580вм80

- •4.4 Классификация команд мп кр580вм80а

- •4.5 Команды пересылки (перемещения) данных

- •4.5.1 Пересылка из регистра в регистр

- •4.5.2 Непосредственная пересылка

- •4.5.3 Непосредственная загрузка пары регистров

- •4.5.4 Запоминание/загрузка аккумулятора и пары hl

- •4.5.5 Ввод из пары регистров в стек

- •4.5.6 Ввод а и f в стек

- •4.5.7 Выбор из стека пары регистров

- •4.5.8 Выбор (a) и (f) из стека

- •4.5.9 Обмен данными

- •4.5.10 Пересылка нl

- •4.6 Приращение / отрицательное приращение

- •4.6.1 Приращение/отрицательное приращение регистра

- •4.6.2 Приращение пары регистров

- •4.6.3 Отрицательное приращение пары регистров

- •4.7 Арифметические и логические операции

- •4.7.1 Арифметические операции над (a) и (r)

- •4.7.2 Арифметические операции с непосредственной адресацией

- •4.7.3 Сложение содержимого пар регистров

- •4.7.4 Логические операции над (а) и (r)

- •0800) Ora c

- •4.7.5 Логические операции с непосредственной адресацией

- •4.7.6 Операции сравнения

- •4.7.7 Операции циклического сдвига (а).

- •4.7.8 Дополнение аккумулятора

- •4.8 Команды перехода и вызова подпрограмм

- •4.8.1 Команды переходов

- •4.8.2 Команды вызова подпрограмм и возврата из подпрограмм

- •4.9 Команды ввода – вывода

- •4.9.1 Ввод данных из входного порта

- •4.9.2 Вывод данных в выходной порт

- •4.10 Команды управления

- •4.10.1 Рестарт (повторный запуск)

- •4.10.2 Изменение (Тс)

- •0800) Stc

- •0800) Cmc

- •4.10.3 Управление прерываниями

- •4.10.4 Двоично-десятичная коррекция

- •4.10.5 Пустая операция

- •4.10.6 Останов

- •4.11 Микропроцессор intel8085

- •4.11.1 Архитектура мп intel8085

- •4.11.2 Регистры мп Intel 8085

- •4.11.3 Ввод и вывод последовательных данных

- •4.12 Контрольные вопросы и задания

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086)

- •5.1. Устройство и работа микропроцессора Intel 8086 (k1810bm86)

- •5.1.1. Структура микропроцессора Intel 8086

- •5.1.2. Режимы работы микропроцессора

- •5.1.3. Структура минимально укомплектованной системы на базе микропроцессора к1810вм86

- •5.1.4. Структура системы средней сложности на базе микропроцессора к1810вм86

- •5.2. Программная модель микропроцессора Intel 8086

- •5.2.1. Пользовательские регистры

- •5.2.2. Регистры общего назначения

- •5.2.3. Сегментные регистры

- •5.2.4. Регистры состояния и управления

- •5.3. Формирование физического адреса в микропроцессоре Intel 8086

- •5.4 Способы адресации микропроцессора

- •5.5 Контрольные вопросы и задания

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4

- •6.1. Архитектура микропроцессоров 80186/80188

- •6.2. Микропроцессор 80286

- •6.2.1 Аппаратные особенности

- •6.2.2 Система команд

- •6.2.3. Виртуальная память

- •6.3. Микропроцессоры 80386 и 80486

- •6.3.1. Микропроцессор 80386

- •6.4. Микропроцессоры Pentium и Pentium Pro

- •6.5. Специальные регистры микропроцессора Pentium

- •6.6. Управление памятью микропроцессора Pentium

- •6.7. Новые команды микропроцессора Pentium

- •6.8. Специальные особенности микропроцессора Pentium Pro

- •6.9. Микропроцессоры Pentium II, Pentium III и Pentium 4

- •6.9.1. Сопряжение с памятью

- •6.9.2. Набор регистров

- •6.11 Контрольные вопросы и задания

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus

- •7.1 Микропроцессор к1801вм1

- •7.1.1 Структурная схема микропроцессора к1801вм1

- •7.1.2 Основные технические характеристики

- •7.1.3 Регистровая модель микропроцессора

- •7.1.4 Адресное пространство

- •7.1.5 Формат команд

- •7.1.6 Методы адресации

- •7.2. Системная магистраль q-Bus

- •7.2.1 Временная диаграмма цикла ввод

- •7.2 2 Временная диаграмма цикла вывод

- •7.2.3 Цикл ввод-пауза-вывод

- •7.2.4 Временная диаграмма предоставления прямого доступа к памяти

- •7.2.5 Временная диаграмма прерывания

- •7.3 Контрольные вопросы и задания

- •Глава 8. Понятие и задачи интерфейса

- •8.1 Интерфейс

- •8.2 Селекция магистралей

- •8.2.1 Схемы централизованной селекции

- •8.2.2 Схемы децентрализованной селекции

- •8.3 Синхронизация обмена по магистрали

- •8.4 Координация взаимодействия устройств на магистрали

- •8.5 Контрольные вопросы и задания

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus

- •9.1 Isa

- •9.2. Порядок обмена по системной магистрали isa

- •9.2.1. Особенности магистрали isa

- •9.2.2. Сигналы магистрали isa

- •9.2.3. Циклы магистрали isa

- •9.3 Разработка устройств сопряжения для isa

- •9.3.1. Проектирование аппаратуры для сопряжения с isa

- •9.4 Разработка устройств сопряжения для q-bus

- •9.5 Контрольные вопросы и задания

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле

- •10.1 Промышленные Fieldbus (полевые) сети

- •10.1.1 Модель osi (Open System Interconnection) (iso/osi) для стандартов.

- •10.1.2 Локальная сеть на основе интерфейса rs-485, объединяющая несколько приемо-передатчиков.

- •10.2 Этапы развития fieldbus технологий

- •10.3 Сетевые протоколы в автомобиле

- •10.4 Контрольные вопросы и задания

- •Глава 11. Интегральные схемы программируемой логики (ис пл)

- •11.1. Классификация ис программируемой логики

- •11.2. Конструктивно-технологические типы современных программируемых элементов

- •11.3. Области применения микросхем с программируемой логикой

- •11.4 Системные свойства ис пл

- •11.5 Типовые схемотехнические решения

- •11.6 Приемы дополнительной обработки сигнала

- •11.7 Организация двунаправленных выводов

- •11.8 Схема программирования типа выхода ячейки (введение триггера)

- •11.9 Fpga (программируемые пользователем вентильные матрицы)

- •11.10. Полные ресурсы межсоединений в микросхемах cpld

- •11.11 Контрольные вопросы и задания

- •Заключение

- •Глоссарий

- •Список литературы

11.4 Системные свойства ис пл

Эти свойства имеют важное значение при использовании ИС ПЛ в составе систем.

Уровни напряжений питания, которые образуют следующий ряд: изначально + 5В, сейчас 3В, 2В, 2.5В, 1.8В, 1.6В. В самой микросхеме ИС ПЛ имеется встроенный источник питания, который вырабатывает повышенное напряжение для программирования.

Управление энергопотреблением. Выделяют активный и пассивный режимы. В пределах активного режима существует несколько подрежимов: повышенное быстродействие с высоким энергопотреблением и стандартное быстродействие с пониженным энергопотреблением. Пассивный режим делится на 2 подрежима:

Первый подрежим (wait) характеризуется существенным снижением мощности, но со способностью к быстрому переходу в активный режим;

Второй подрежим (stop) – режим глубокого снижения энергопотребления, когда на переход в активное состояние требуется длительное время.

Использование интерфейса (JTAG) - интерфейс граничного сканирования. Используется для программирования внутренних элементов схем, занесения программы в статическую память.

Защита памяти конфигурации.

Возможность внутрисхемного программирования.

Управление крутизной фронтов. Используется для снижения помех, генерируемых самой схемой. Выходные буферные элементы являются источниками сильных помех (особенно при высокой крутизне фронтов), как правило, крутизна выходных фронтов делается низкой и только в специальных случаях ее увеличивают.

11.5 Типовые схемотехнические решения

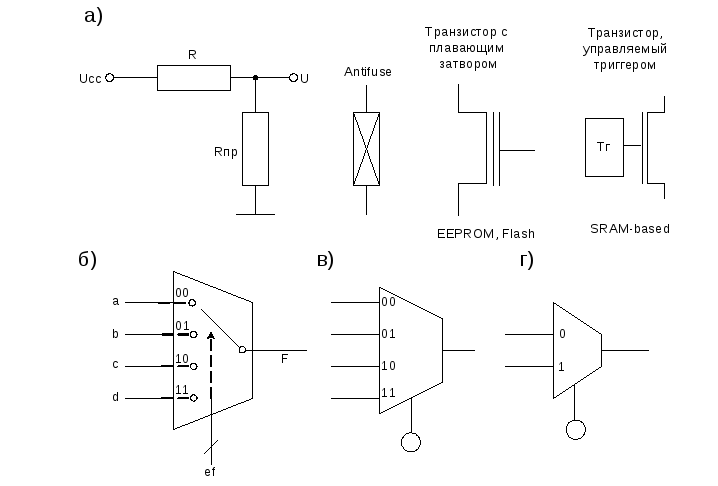

На рис. 11.5 а) приведена схема управляемого делителя напряжения, который может сформировать на выходе либо сигнал напряжения низкого уровня (логический «0»), либо сигнал напряжения высокого уровня (логическая «1»).

В роли программируемого резистора выступает полевой транзистор, при запирании которого выходное напряжение стремится к логической «1», а при открывании – к логическому «0».

|

Рис. 11.5 Схемы выработки программируемых сигналов управления (а) и программируемых мультиплексоров (б, в, г) |

На рис. 11.5 б) приведена схема программируемого мультиплексора, который применяется для конфигурирования межсоединений и построения логических блоков. В последнем случае (рис. 11.5 б) мультиплексор можно условно отобразить в виде переключателя, который под управлением адресных входов передает на выход F одну из входных величин – a, b, c или d. Возле линии каждого входа отмечена комбинация сигналов адреса, подключающая данный вход к выходу мультиплексора. В условном обозначении программируемого мультиплексора в режиме коммутации сигналов (рис. 11.5 в) факт программируемости обозначается кружком на группе адресных входов. При программировании устанавливается определенный код ef и соответствующая ему связь между выходом схемы и одним из входов. Для часто применяемых программируемых мультиплексоров размерности 2-1 условное обозначение имеет вид, показанный на рис. 11.5 г). Комбинации сигналов адреса возле линий входов могут и не указываться, если в этом нет необходимости.

11.6 Приемы дополнительной обработки сигнала

Программирование полярности формируемых функций. Этот прием (рис. 11.6) наиболее часто используется в CPLD, реализующих логические функции в форме ДНФ. Полезность данного приема заключается в том, что логическая функция F и ее инверсия не идентичны по сложности и выражения для них могут иметь существенно различные числа термов.

|

|

|

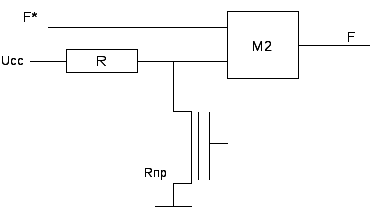

Рис. 11.6 Схема управления полярностью функции |

Рассмотрим реализацию схемы управления полярностью функции. В ней М2 – сумматор по модулю 2 («исключающее ИЛИ»).

Пусть

Uуправления = 0 и транзистор закрыт. На

нижнем входе М2 формируется логическая

«1». F*=0

F=1; F*=1

F=0. F=![]() т.е. произошло изменение полярности.

т.е. произошло изменение полярности.

Пусть Uуправления = 1 и транзистор закрыт. На нижнем входе М2 формируется логический «0». F*=0 F=0; F*=1 F=1. F = F*, т.е. полярность не изменяется.