- •К.А. Палагута Микропроцессоры и интерфейсные средства транспортных средств

- •Москва 2011

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия 11

- •Глава 2 Режимы работы мпс 33

- •Глава 3. Реализация и организация памяти мп 57

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080) 77

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086) 138

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4 159

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus 209

- •Глава 8. Понятие и задачи интерфейса 239

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus 255

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле 308

- •Глава 11. Интегральные схемы программируемой логики (ис пл) 326

- •Предисловие

- •Введение

- •Глава 1. Микропроцессор (мп), микропроцессорная система (мпс), основные понятия

- •1.1 Определение микропроцессора, классификация мп

- •1.2 Микропроцессорный комплект (мпк)

- •1.3 Микропроцессорная система

- •1.4 Линия, шина, магистраль

- •1.5 Типы магистралей

- •1.6 Шина адреса, раздельные и объединенные адресные пространства памяти и устройств ввода-вывода

- •1.7 Шина данных

- •1.8 Шина управления

- •1.9 Архитектура и структура микропроцессора

- •1.10 Cisc и risc процессоры, конвейерное выполнение команд программы

- •1.11 Конвейерная обработка данных

- •1.12 Контрольные вопросы и задания

- •Глава 2 Режимы работы мпс

- •2.1 Режим обмена данными под управлением процессора

- •2.2 Режим пдп

- •2.3 Режим прерывания

- •2.4 Контрольные вопросы и задания

- •Глава 3. Реализация и организация памяти мп

- •3.1. Виды запоминающих устройств (зу)

- •3.2. Кэш-память

- •3.3. Когерентность, механизмы сквозной и обратной записи

- •3.4. Алгоритмы обновления содержимого заполненных строк, снуппинг

- •3.5. Организация памяти

- •3.6. Внешние зу

- •3.7. Контрольные вопросы и задания

- •Глава 4. Микропроцессор кр580вм80а (Intel 8080)

- •4.1 Структура мп к580вм80

- •4.2 Основные технические характеристики мп кр580вм80а

- •4.3 Регистровая модель мп к580вм80

- •4.4 Классификация команд мп кр580вм80а

- •4.5 Команды пересылки (перемещения) данных

- •4.5.1 Пересылка из регистра в регистр

- •4.5.2 Непосредственная пересылка

- •4.5.3 Непосредственная загрузка пары регистров

- •4.5.4 Запоминание/загрузка аккумулятора и пары hl

- •4.5.5 Ввод из пары регистров в стек

- •4.5.6 Ввод а и f в стек

- •4.5.7 Выбор из стека пары регистров

- •4.5.8 Выбор (a) и (f) из стека

- •4.5.9 Обмен данными

- •4.5.10 Пересылка нl

- •4.6 Приращение / отрицательное приращение

- •4.6.1 Приращение/отрицательное приращение регистра

- •4.6.2 Приращение пары регистров

- •4.6.3 Отрицательное приращение пары регистров

- •4.7 Арифметические и логические операции

- •4.7.1 Арифметические операции над (a) и (r)

- •4.7.2 Арифметические операции с непосредственной адресацией

- •4.7.3 Сложение содержимого пар регистров

- •4.7.4 Логические операции над (а) и (r)

- •0800) Ora c

- •4.7.5 Логические операции с непосредственной адресацией

- •4.7.6 Операции сравнения

- •4.7.7 Операции циклического сдвига (а).

- •4.7.8 Дополнение аккумулятора

- •4.8 Команды перехода и вызова подпрограмм

- •4.8.1 Команды переходов

- •4.8.2 Команды вызова подпрограмм и возврата из подпрограмм

- •4.9 Команды ввода – вывода

- •4.9.1 Ввод данных из входного порта

- •4.9.2 Вывод данных в выходной порт

- •4.10 Команды управления

- •4.10.1 Рестарт (повторный запуск)

- •4.10.2 Изменение (Тс)

- •0800) Stc

- •0800) Cmc

- •4.10.3 Управление прерываниями

- •4.10.4 Двоично-десятичная коррекция

- •4.10.5 Пустая операция

- •4.10.6 Останов

- •4.11 Микропроцессор intel8085

- •4.11.1 Архитектура мп intel8085

- •4.11.2 Регистры мп Intel 8085

- •4.11.3 Ввод и вывод последовательных данных

- •4.12 Контрольные вопросы и задания

- •Глава 5. Микропроцессор к1810вм86 (Intel 8086)

- •5.1. Устройство и работа микропроцессора Intel 8086 (k1810bm86)

- •5.1.1. Структура микропроцессора Intel 8086

- •5.1.2. Режимы работы микропроцессора

- •5.1.3. Структура минимально укомплектованной системы на базе микропроцессора к1810вм86

- •5.1.4. Структура системы средней сложности на базе микропроцессора к1810вм86

- •5.2. Программная модель микропроцессора Intel 8086

- •5.2.1. Пользовательские регистры

- •5.2.2. Регистры общего назначения

- •5.2.3. Сегментные регистры

- •5.2.4. Регистры состояния и управления

- •5.3. Формирование физического адреса в микропроцессоре Intel 8086

- •5.4 Способы адресации микропроцессора

- •5.5 Контрольные вопросы и задания

- •Глава 6. Микропроцессоры Intel от 80186 до Pentium 4

- •6.1. Архитектура микропроцессоров 80186/80188

- •6.2. Микропроцессор 80286

- •6.2.1 Аппаратные особенности

- •6.2.2 Система команд

- •6.2.3. Виртуальная память

- •6.3. Микропроцессоры 80386 и 80486

- •6.3.1. Микропроцессор 80386

- •6.4. Микропроцессоры Pentium и Pentium Pro

- •6.5. Специальные регистры микропроцессора Pentium

- •6.6. Управление памятью микропроцессора Pentium

- •6.7. Новые команды микропроцессора Pentium

- •6.8. Специальные особенности микропроцессора Pentium Pro

- •6.9. Микропроцессоры Pentium II, Pentium III и Pentium 4

- •6.9.1. Сопряжение с памятью

- •6.9.2. Набор регистров

- •6.11 Контрольные вопросы и задания

- •Глава 7. Микропроцессор к1801вм1, магистраль q-bus

- •7.1 Микропроцессор к1801вм1

- •7.1.1 Структурная схема микропроцессора к1801вм1

- •7.1.2 Основные технические характеристики

- •7.1.3 Регистровая модель микропроцессора

- •7.1.4 Адресное пространство

- •7.1.5 Формат команд

- •7.1.6 Методы адресации

- •7.2. Системная магистраль q-Bus

- •7.2.1 Временная диаграмма цикла ввод

- •7.2 2 Временная диаграмма цикла вывод

- •7.2.3 Цикл ввод-пауза-вывод

- •7.2.4 Временная диаграмма предоставления прямого доступа к памяти

- •7.2.5 Временная диаграмма прерывания

- •7.3 Контрольные вопросы и задания

- •Глава 8. Понятие и задачи интерфейса

- •8.1 Интерфейс

- •8.2 Селекция магистралей

- •8.2.1 Схемы централизованной селекции

- •8.2.2 Схемы децентрализованной селекции

- •8.3 Синхронизация обмена по магистрали

- •8.4 Координация взаимодействия устройств на магистрали

- •8.5 Контрольные вопросы и задания

- •Глава 9. Интерфейсные блоки для магистралей isa и q-bus

- •9.1 Isa

- •9.2. Порядок обмена по системной магистрали isa

- •9.2.1. Особенности магистрали isa

- •9.2.2. Сигналы магистрали isa

- •9.2.3. Циклы магистрали isa

- •9.3 Разработка устройств сопряжения для isa

- •9.3.1. Проектирование аппаратуры для сопряжения с isa

- •9.4 Разработка устройств сопряжения для q-bus

- •9.5 Контрольные вопросы и задания

- •Глава 10. Промышленные интерфейсы. Сетевые протоколы в автомобиле

- •10.1 Промышленные Fieldbus (полевые) сети

- •10.1.1 Модель osi (Open System Interconnection) (iso/osi) для стандартов.

- •10.1.2 Локальная сеть на основе интерфейса rs-485, объединяющая несколько приемо-передатчиков.

- •10.2 Этапы развития fieldbus технологий

- •10.3 Сетевые протоколы в автомобиле

- •10.4 Контрольные вопросы и задания

- •Глава 11. Интегральные схемы программируемой логики (ис пл)

- •11.1. Классификация ис программируемой логики

- •11.2. Конструктивно-технологические типы современных программируемых элементов

- •11.3. Области применения микросхем с программируемой логикой

- •11.4 Системные свойства ис пл

- •11.5 Типовые схемотехнические решения

- •11.6 Приемы дополнительной обработки сигнала

- •11.7 Организация двунаправленных выводов

- •11.8 Схема программирования типа выхода ячейки (введение триггера)

- •11.9 Fpga (программируемые пользователем вентильные матрицы)

- •11.10. Полные ресурсы межсоединений в микросхемах cpld

- •11.11 Контрольные вопросы и задания

- •Заключение

- •Глоссарий

- •Список литературы

3.3. Когерентность, механизмы сквозной и обратной записи

Нормальная работа микропроцессорной системы с кэш-памятью обеспечивается соответствующими механизмами, которые поддерживают когерентность - соответствие содержимого ОЗУ и кэш-памяти. Это соответствие достигается с помощью механизмов сквозной записи (Write-Through) или обратной записи (Write-Back).

При сквозной записи выполняется одновременное изменение содержимого кэш-памяти и ОЗУ. Таким образом, при любом цикле записи, даже в случае кэш-попадания, производится обращение к основной памяти по системной шине. Данное обстоятельство существенно снижает производительность системы, так как циклы обращения по этой шине выполняются с тактовой частотой системной платы, которая значительно ниже тактовой частоты процессора.

При обратной записи изменение содержимого строки кэш-памяти вызывает установку признака модификации М=1. При обновлении содержимого кэш-памяти ее строки, имеющие значение признака М=1, переписываются обратно в основную память. Таким образом, обращение к основной памяти в циклах записи производится только в случае кэш-промаха. При использовании кэш-памяти значительной емкости в режиме обратной записи процессор может достаточно долго работать без обращения к ОЗУ. Этот механизм наиболее часто используется в кэш-памяти современных микропроцессоров, хотя многие из них могут реализовать как обратную, так и сквозную запись.

Следует отметить, что для кэш-памяти команд, из которой производится только считывание кодов, не требуется поддержание когерентности. Поэтому механизмы сквозной и обратной записи реализуются только для кэш-памяти данных или общей кэш-памяти команд и данных.

3.4. Алгоритмы обновления содержимого заполненных строк, снуппинг

Каждая кэш-память имеет собственную служебную память, где хранятся биты, характеризующие содержимое ее строк: биты обращения, используемые для определения строки, содержимое которой будет обновляться, и биты состояния (бит модификации М, бит достоверности V и другие), с помощью которых обеспечивается когерентность содержимого строки в кэш-памяти и ОЗУ.

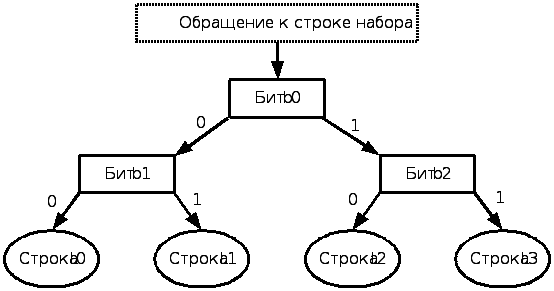

Если при чтении произошел кэш-промах, и кэширование данной области памяти разрешено, то производится обновление содержимого одной из строк набора, заданного полем SET адреса, в которую вводится информация из основной памяти. Новая информация замещает ранее имеющуюся в данной строке. В первую очередь замещается содержимое незаполненной («пустой») строки или недостоверной строки, содержание которой было аннулировано специальной командой. Такие строки имеют значение бита достоверности V=0. Если в данном наборе нет недостоверной ("пустой") строки, то производится удаление из кэш-памяти содержимого строки, которая дольше всего оставалась невостребованной.

Обычно используемый алгоритм обновления содержимого заполненных строк называется "замещение менее используемой информации" (LRU – Least Recently Used) и реализуется с помощью битов обращения. Рассмотрим реализацию этого алгоритма для кэш-памяти, наборы которой содержат по четыре строки. В этом случае в служебной памяти для каждого набора хранятся три бита обращения b0-b2 (биты LRU), значения которых определяют выбор строки, замещаемой в данном наборе при кэш-промахе.

|

|

|

Рис. 3.2. Установка битов LRU при обращении к строкам кэш-памяти

|

При инициализации процессора и очистке кэш-памяти биты LRU всех наборов кэш-памяти сбрасываются в 0. В ходе работы процессора значения битов b0-b2 устанавливаются в соответствии с тем, к каким из строк набора производились последние обращения (рис. 3.2). Если в данном наборе последнее обращение выполнялось к одной из пары строк L0 или L1, устанавливается b0=1, если к LЗ или L4, то устанавливается b0=0. Биты b1 и b2 указывают, к какой из строк пары L1-L2 и L3-L4 осуществлялось последнее обращение. Значение b1=0 устанавливается при обращении к L0, значение b1 = 1 - при обращении к L1. Соответственно, значение b2=0 или 1 устанавливается при обращении к строке L2 или L3. В соответствии с алгоритмом LRU для замены выбирается пара строк, к которым не производилось последнее обращение, а в этой паре замене подлежит строка, к которой не производилось последнее обращение. Выбранная таким образом строка считается дольше всего неиспользуемой в данном наборе, поэтому ее содержимое замещается строкой, выбираемой из ОЗУ при кэш-промахе.

Данное описание соответствует использованию наборов из четырех строк, что чаще всего реализуется в кэш-памяти микропроцессоров. Для кэш-памяти, содержащей две строки в наборе, требуется только один бит LRU для каждого набора, который принимает значение b0=0 при обращении к строке L0, и b0=1 при обращении к L1.

При использовании кэш-памяти с обратной записью когерентность содержимого ОЗУ и кэш-памяти обеспечивается операционной системой, контролирующей значение битов состояния строки при обращении к внешней памяти. Это особенно важно в мультипроцессорных системах, где несколько микропроцессоров могут использовать общее ОЗУ, реализуя захват системной шины (прямой доступ к памяти).

Если выполняется захват системной шины другим процессором (активным устройством) в мультипроцессорной системе, то отключаемый от шины процессор продолжает выполнение команд и обработку данных, содержащихся в кэш-памяти. Активный процессор может обратиться к данным, копии которых уже находятся в кэш-памяти процессора, отключенного от системной шины. Поэтому необходимо принять меры для обеспечения идентичности копий данных, используемых различными процессорами. Такие меры реализуются с помощью специальных средств, выполняющих снуппинг (snoop) - слежение за содержимым кэш-памяти разных процессоров, входящих в систему. При этом отключенный от системной шины процессор принимает адреса, выдаваемые на адресные линии активным процессором. Если этот адрес совпадает с адресом данных, хранящихся в одной из заполненных строк кэш-памяти данных отключенного процессора, то выполняются следующие процедуры. Если активный процессор производил запись по данному адресу, то содержимое соответствующей строки в отключенном от шине процессоре аннулируется (устанавливается значение бита V=0). Если активный процессор производил чтение по адресу модифицированной строки, имеющей значение бита модификации М=1, то отключенный процессор выполняет специальный цикл выдачи адресованных данных на внешнюю шину, чтобы активный процессор получил их модифицированный вариант.

Специальные команды управления процессором позволяют производить очистку кэш-памяти (аннулирование содержимого строк) путем установки значений бита достоверности V=0. При этом для обеспечения когерентности содержимое модифицированных строк переписывается в ОЗУ.