- •Организация эвм и систем

- •Глава 6 Организация памяти

- •Глава 1. Структура современного компьютера

- •1.1 Основные понятия

- •1.2 Принцип действия компьютера

- •Цикл работы компьютера

- •1.3 Программное обеспечение компьютера

- •1.4 Надежность, производительность и показатели быстродействия

- •Производительность компьютера

- •Технико-эксплуатационные характеристики

- •1.5 Вычислительные системы и сети

- •Вопросы для самопроверки

- •Глава 2 представление информации в компьютере

- •5.2 Система команд. Форматы команд и способы адресации

- •5.3 Система прерываний и приостановок, состояние процессора

- •Характеристики системы прерываний

- •Организация перехода к прерывающей программе

- •5.4 Режимы работы процессора: однопрограммный, пакетный, разделения времени, реального времени

- •5.5 CisCиRisCкомпьютеры

- •Процессоры персональных компьютеров

- •5.6 Устройства управления

- •Устройства управления с хранимой в памяти логикой

- •5.7 Методы и средства повышения производительности процессоров персональных компьютеров

- •Суперскалярная обработка

- •Переименование регистров

- •Динамическое прогнозирование условных переходов

- •Контроллер памяти Контроллер pci

- •Вопросы для самопроверки

- •Глава 6. Организация памяти

- •6.1 Адресное пространство

- •6.2 Виды памяти

- •6.3 Оперативная память

- •Статическая и динамическая память

- •6.5 Внешняя память

- •6.6 Организация виртуальной памяти

- •Страничное, сегментное и странично-сегментное распределение

- •Свопинг

- •6.7 Защита памяти

- •Вопросы для самопроверки

- •Глава 7. Интерфейсы

- •7.1 Понятие интерфейса и его характеристики

- •7.1 Состав линий системной шины

- •Передача данных по проводным линиям связи По линиям связи современных интерфейсов преимущественно передаются низкочастотные дискретные одно - и биполярные сигналы (рисунок 7.Х).

- •Адрес верный

- •7.2 Подключение устройств

- •7.4 Интерфейсы внешней памяти

- •7.5 Малые интерфейсы (usb,ide,rs-232c,scsi)

- •Вопросы для самопроверки

- •Глава 8. Периферийные устройства компьютеров

- •8.1 Организация систем ввода-вывода. Каналы, контроллеры

- •Основные функции свв

- •Программный ввод-вывод

- •Прямой доступ в память

- •8.2 Клавиатура и мышь

- •8.3 Дисплеи

- •8.4 Принтеры

- •8.5 Накопители на магнитных дисках

- •Структура накопителя на жестких дисках

- •Структура и особенности накопителя на гмд

- •8.6 Накопители на компакт-дисках (cd-rom, cd-r, cd-rw, dvd)

- •8.7 Другие виды периферийных устройств

- •Вопросы для самопроверки

- •Какие особенности пу делают возможным организацию параллельной обработки и ввода-вывода?

- •Закон Амдала

- •Совместно используемая и распределенная память

- •Когерентность кэш-памяти

- •Наибольшее распространение получили следующие аппаратные механизмы, реализующие протокол когерентности кэш-памяти: это протоколы наблюдения и на основе справочника.

- •9.2 Конвейерные системы

- •Векторные регистры

- •9.3 Симметричные системы

- •9.4 Вычислительные системы со сверхдлинным командным словом

- •9.5 Другие виды мультипроцессорных систем

- •Машины с массовым параллелизмом

- •Нейрокомпьютеры

- •9.6 Проблемно-ориентированные системы

- •Вопросы для самопроверки

- •Глава 10. Организация вычислительного процесса

- •12.2 Системы автоматического контроля и диагностики

- •Контроль передач информации

- •Контроль арифметических операций

- •12.3 Защита памяти. Raid-массивы

- •12.4 Построение «безотказных» систем питания Вопросы для самопроверки

- •Список литературы

Адрес верный

£75нс ³75нс

t0 t1t2t3 t4

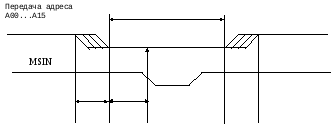

Рисунок 7.х. Временная диаграмма передачи адреса по параллельной магистрали со стробированием

Адресация и идентификация

Рассмотренный пример косвенно

затрагивает еще одну важную сторону

передачи информации – организацию

группового обмена по общей шине. Одним

из характерных способов такого обмена

является централизованный, когда по

общей шине устройство А0обменивается

данными с одним из устройств Вi(i=![]() ),

подключенным к магистрали. В этом случае

возникает необходимость в решении задач

адресации и идентификации.

),

подключенным к магистрали. В этом случае

возникает необходимость в решении задач

адресации и идентификации.

Адресация – это выбор центральным устройством А0одного из устройств Вiдля связи. Идентификация состоит в определении центральным устройством А0, какое из устройств Вiзапрашивает связь. Решение этих двух задач требует передачи по линиям управления интерфейса дополнительной информации, количество которой зависит от организации и структуры интерфейса.

Возможен интерфейс с индивидуальными линиями (радиального типа), в котором центральное устройство соединено с периферийными по индивидуальным линиям. При использовании такой системы существенно упрощается решение задач адресации и идентификации, но при этом увеличивается количество оборудования, следовательно, повышаются стоимость, энергопотребление и снижается надежность.

При использовании схем с коллективным линиями значительно уменьшается их число, но существенно усложняются процессы адресации и идентификации. В этом варианте периферийные устройства Biпринимают все предаваемые центральным устройством А сообщения, но селектируют их в зависимости от собственного адреса. Идентификация активных периферийных устройств центральным устройством реализуется путем селекции соответствующего идентификационного номера.

В этом случае шина управления служит для определения момента, когда возможна передача данных, когда нужно передать адрес, когда нужно выполнить процедуру арбитража (т.е. определить, какое из подключенных к шине устройств имеет право выставлять свои данные на шину) и т.п.

К «системной» шине всегда подключается более двух устройств, а одновременно передача данных может производиться только между двумя из них. А это означает, что в один и тот же момент возможно появление нескольких запросов, которые могут быть удовлетворены только последовательно один за другим. Поэтому каждое из устройств должно получить в свое распоряжение шину и только после этого передавать по ней данные. Следовательно, любая шина должна обладать средствами «арбитража», позволяющими выстраивать очередь запросов, разрешая одновременную передачу данных только между двумя устройствами.

Арбитраж можно реализовать разными способами: чаще всего его организуют в виде последовательного распределенного арбитража или в виде параллельного арбитража.

При последовательном распределенном арбитраже все устройства подключаются последовательно к линии, по которой передается арбитражный сигнал АРБN (рисунок 7.х). Этот сигнал АРБN подается на выход устройства, которому присвоен наивысший приоритет и подключается к точке с потенциалом земли, а выходной сигнал АРБ0 подается на вход следующего устройства с более низким приоритетом. Таким образом, образуется цепочка последовательно подключаемых устройств. Сигнал АРБN подается в эту цепочку и достигает устройства, которое должно стать задатчиком, т.е. устройством, занимающим интерфейс для передачи или приема данных. На все устройства подается синхронизирующий сигнал BCLK; устройство имеет право выставлять запрос на занятие шины, т.е. размыкать ключ в цепи арбитражного сигнала по положительному фронту сигнала BCLK.

По отрицательному фронту этого сигнала устройство формирует сигнал на линии BUSY, «захватывая» магистраль, т.е. теперь магистраль отдается в распоряжение исключительно этого устройства. Таким образом, чтобы устройство стало задатчиком, должны быть выполнены следующие условия:

отсутствие сигнала АРБ0 (т.е. устройство запрашивает шину),

присутствие сигнала АРБN (т.е. ни одно из более приоритетных устройств не запрашивает шину),

отсутствие сигнала BUSY (т.е. шина свободна).

B

CLK

CLK

А

РБNАРБ0

РБNАРБ0

АРБNАРБ0

АРБNАРБ0

BUSY

Рисунок 7.х. Схема последовательного распределенного арбитража

Для организации параллельного арбитража используется специальная схема приоритетного шифратора-дешифратора, рисунок 7.х. На входы этого шифратора Ш подаются запросы от множества устройств на право занять шину BREQ, а на выходах дешифратора ДШ может присутствовать только один сигнал BPRN, направляемый к одному из подключенных к нему устройств и разрешающий использовать шину в данный момент для передачи данных. Устройство, получившее этот сигнал, захватывает магистраль (т.е. выставляет сигнал BUSY). Сигнал BUSY удерживается до завершения работы устройства, предотвращая занятие шины другими устройствами. Схема параллельного арбитража ограничивает число устройств количеством входных и выходных сигналов. Однако она обладает высоким быстродействием и обычно служит для арбитража контроллеров прямого доступа в память.

Рисунок 7.х. Схема параллельного арбитража (а) и временная диаграмма его работы (б)

Помимо параллельного арбитража известна схема циклического арбитража. Ее работа подобна работе схемы параллельного арбитража за исключением того, что после завершения цикла работы, т.е. когда какому-нибудь устройству разрешено передавать данные по магистрали, ему присваивается самый низкий приоритет, а приоритет всех остальных устройств увеличивается. Число устройств при параллельном и циклическом арбитраже ограничено числом входов и выходов приоритетного шифратора.

Непосредственно к шине подключается не устройство, а его контроллер (или адаптер); само же устройство подключают к этому контроллеру через точку доступа, которую называют физическим «портом». Физический порт – это место подключения устройства, т.е. практически это разъем для подсоединения устройства к линиям интерфейса. Порт, или «малый» интерфейс позволяет подключать устройство к контроллеру стандартным образом. В персональных компьютерах периферийные устройства подключают к параллельному или последовательному интерфейсам.

Как правило, малые интерфейсы строят по радиальному принципу, т.е. устройство подключается по отдельным принадлежащим только ему проводам, а поэтому необходимость в адресации отпадает (к каждому интерфейсу может подключаться только одно устройство).