Prikladnoe_programmirovanie_-Konspekt_lektsy

.pdf

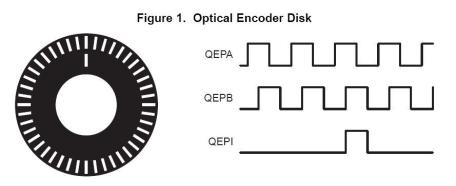

импульсы, соответствующие изменению углового положения на 1/N часть оборота, где N

– число щелей на обороте. Как правило, в датчике располагается также вторая пара осветитель-приемник, сдвинутая относительно первой на ¼ шага, и третья, расположенная напротив второй дорожки, состоящей всего из одной щели и соответствующей началу отсчета.

Рис.4.1. Инкрементный датчик угла

В линейных инкрементных датчиках дорожки щелей вытянуты в линию. 4.1.3 Начало отсчета задается импульсом QEPI, длительность которого может

соответствовать различному угловому интервалу, а фронты привязаны или не привязаны к фронтам сигналов QEPA, QEPB.

Для определения направления движения анализируются сигналы, приходящие с двух фотоприемников, эти сигналы квадратурны, т.е. сдвинуты по фазе на 90º, а знак разности фаз характеризует направление движения. У большинства датчиков при движении по часовой стрелке передний фронт сигнала QEPA опережает QEPB на четверть периода.

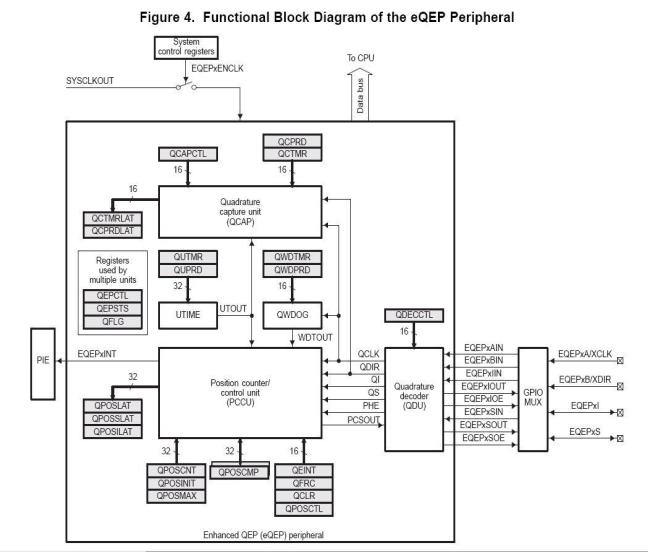

4.1.4 Модуль содержит следующие узлы (см. рис.4.2):

-программируемые входы (посредством GPIO MUX);

-квадратурный декодер (QDU);

-узел позиционного счетчика и управления измерением положения (PCCU);

-квадратурный узел захвата фронтов для измерения низких скоростей (QCAP);

-формирователь эталонного временного интервала для измерения высоких скоростей (UTIME);

-сторожевой таймер для выявления зависаний (QWDOG).

4.1.5Каждый модуль имеет 4 входа, подключаемые к выводам процессора посредством GPIO MUX. В зависимости от подключаемого датчика модуль может быть настроен для работы в одном из двух режимов: Quadrature-clock Mode или Direction-count Mode Пара входов QEPA/XCLK and QEPB/XDIR в режиме Quadrature-clock Mode

предназначена для приема сигналов прямоугольной формы QEPA and QEPB, сдвинутых на четверть периода. По этим сигналам квадратурный декодер (QDU) формирует сигнал направления движения и последовательность счетных импульсов.

Если используется датчик угла, формирующий сигнал направления движения и последовательность счетных импульсов (а не пару сигналов А и В), в режиме Quadratureclock Mode эти сигналы подаются на пару входов QEPA/XCLK and QEPB/XDIR.

Вход eQEPI: Index or Zero Marker – служит для приема сигнала нулевой метки, используемого для сброса позиционного счетчика в нулевое состояние при начале каждого нового оборота.

Вход QEPS: Strobe Input – для приема строб-сигнала, информирующего о некотором внешнем событии.

21

4.1.6Узел позиционного счетчика и управления измерением положения (PCCU) по сигналам направления движения и последовательности счетных импульсов формирует код текущего углового положения.

4.1.7При вращении импульсы формируются с частотой, пропорциональной скорости вращения. Скорость может вычисляться контроллером по двум различным алгоритмам:

-при больших скоростях в узле PCCU подсчитывается число импульсов за фиксированный интервал времени, формируемый формирователем эталонного временного интервала для измерения высоких скоростей (UTIME);

-при малых скоростях формирователем эталонного временного интервала для измерения высоких скоростей (UTIME) измеряется время, за которое происходит поворот на фиксированный угол (например, на 1/N часть оборота).

В системах, где вал вращается в широком диапазоне скоростей, используются оба алгоритма, переход с одного на другой происходит на заданной пороговой скорости.

4.1.8На сторожевой таймер модуля QWDOG, который контролирует работу модуля, поступают тактовые импульсы SYSCLKOUT/64, после их деления на 64. Сброс счетчика таймера осуществляется импульсами QCLK. При их отсутствии в течение периода, заданного в регистре QWDPRD, флаг прерывания от сторожевого таймера устанавливается в QFLG[WTO]. Сторожевой таймер программируется через регистр

QWDPRD.

Рис.4.2. Блок-схема модуля eQEP

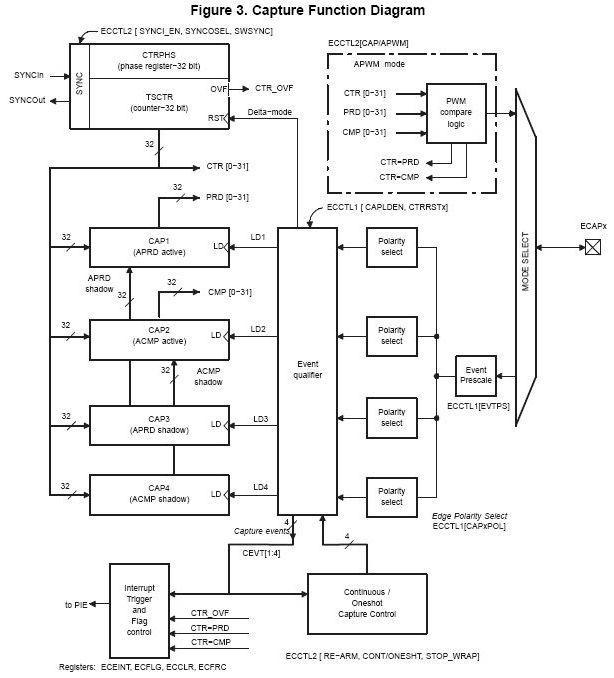

4.2 Модуль eCAP захвата внешних событий (Capture)

22

4.2.1 Модуль востребован в системах, где требуется точная временная привязка внешних событий, и используется для измерения частоты или периода импульсных сигналов, длительности импульсов и временных интервалов между ними. Модуль содержит 6 субмодулей захвата.

4.2.2 Каждый субмодуль (см.рис. 4.3) представляет собой один полный канал захвата, который может реагировать на множество событий. Субмодуль имеет выделенный входной вывод на микросхеме, содержит временную базу на основе 32-разрядного счетчика и четыре 32-разрядных регистра для фиксации моментов времени, соответствующих заданным событиям во входном сигнале, имеет индивидуальную настройку полярности (фронт/спад) для каждого из событий. Субмодули при необходимости могут быть использованы для генерации ШИМ-сигналов.

4.2.3 Входная последовательность импульсов может передаваться на анализ непосредственно, может прореживаться в число раз от 2 до 62, заданных во входном делителе.

4.2.4 Субмодуль фиксирует в регистрах время событий (изменения уровней входного сигнала) циклически или замораживает (в режиме one-shot) состояние регистров после прохождения заданного числа (от 1 до 4) событий.

23

Рис.4.3. Блок-схема субмодуля eCAP

4.2.5 Субмодуль генерирует прерывание по любому из семи событий: 4 входных, переполнению счетчика и (в режиме ШИМ) по переходам ШИМ –сигнала.

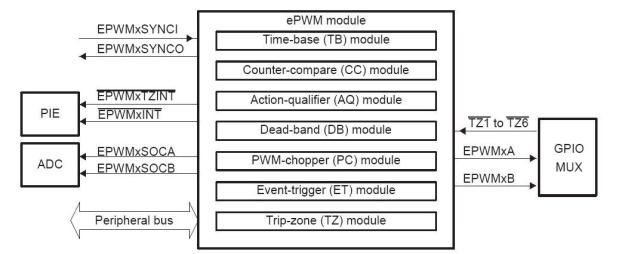

4.3 Модуль ePWM широтно-импульсной модуляции

4.3.1 Модуль предназначен для выработки сложных ШИМ-сигналов с минимальным отвлечением ресурсов CPU. Модуль содержит 12 субмодулей, 6 из которых могут использоваться в режиме с повышенным разрешением. Все модули охвачены единой синхронизацией и могут работать как поодиночке, так и в системе.

4.3.2 Каждый субмодуль представляет собой один полный канал ШИМ, который формирует два выходных сигнала: EPWMxA и EPWMxB. Субмодуль содержит временную базу на основе 16-разрядного счетчика с управлением периодом и частотой. Выходы субмодуля могут использоваться в трех конфигурациях:

24

-два независимых сигнала с одним переходом;

-два независимых сигнала с двумя симметричными переходами;

-один независимый сигнал с двумя несимметричными переходами.

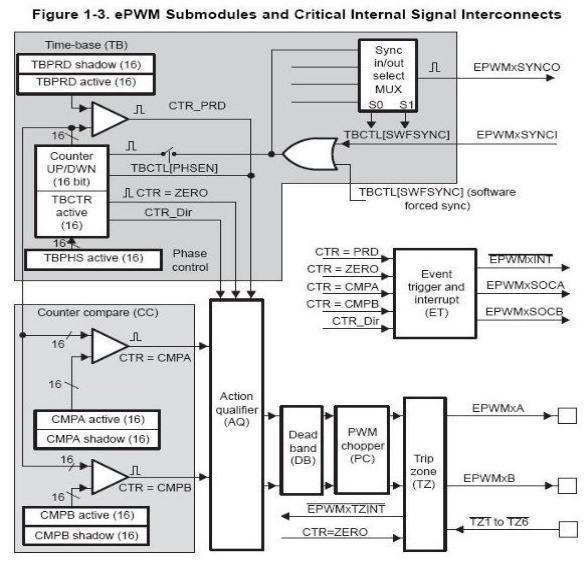

Рис.4.4. Структура субмодуля ePWM

На рисунке 4.4 приведена структура субмодуля и его связи. Субмодуль включает следующие узлы:

-Time-base module - формирует временную базу на основе 16-разрядного счетчика

суправлением периодом и частотой и синхронизирует ее с другими субмодулями;

-Counter-compare module – формирует ШИМ сигнал по длительности;

-Action-qualifier module – определяет направление переходов и управляет формированием сигнала по уровню;

-Dead-band module – формирует мертвые зоны между фронтами EPWMxA и EPWMxB сигналов;

-PWM-chopper module – формирует вид цепочки импульсов в ШИМ сигнале;

Event-trigger module – формирует прерывания;

-Trip-zone module – формирует выходные сигналы EPWMxA и EPWMxB по

уровню.

Блок-схема субмодуля и основные связи между его узлами приведены на рис.4.5. Конфигурирование субмодуля производится с помощью набора

конфигурационных регистров:

25

Рис.4.5. Блок-схема субмодуля ePWM и основные связи между его функциональными узлами

4.4 Модуль HRPWM широтно-импульсной модуляции с повышенным разрешением

4.4.1 Модуль обеспечивает формирование ШИМ сигналов с повышенным разрешением, когда частота сигналов превышает 200 кГц. Разрешение по времени может быть повышено с 10 нс до 180 пс.

4.5 Аналого-цифровой преобразователь ADC

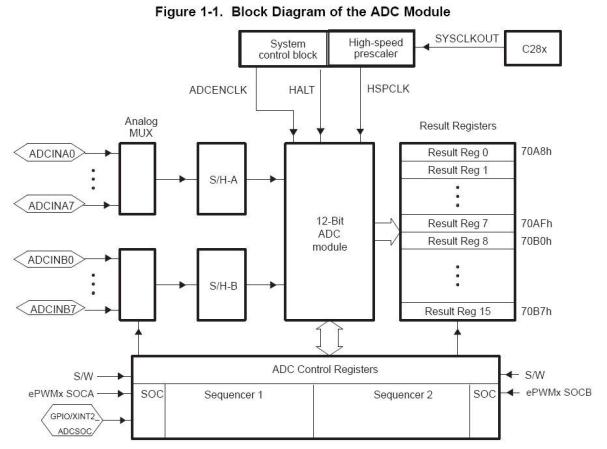

4.5.1 В состав контроллера входит 12-разрядный конвейерный АЦП. Входные каналы АЦП сконфигурированы в два независимых модуля, каждый из которых содержит 8 каналов, но далее сигналы всех 16 каналов обрабатываются одним АЦП.

Основные характеристики АЦП:

-одно ядро преобразователя, но два устройства выборки/хранения;

-16 мультиплексируемых входов;

-одновременный и последовательный режимы выборки;

-входной диапазон от 0 до 3 В;

-быстродействие 6,25 миллиона преобразований в секунду;

26

-выборкой каналов управляют секвенсоры, их два по 8 состояний каждый, могут работать параллельно или последовательно как один на 16 состояний;

-16 индивидуально адресуемых регистров для хранения результатов преобразования;

-запуск преобразования программно, от модуля ePWM, от XINT2;

-управление временем выборки в устройствах выборки/хранения;

-код на выходе изменяется от 0 при Uвх=0 В до 4095 при Uвх≥3 В.

Блок-схема модуля АЦП и основные связи между его узлами приведены на рис.4.6.

Рис.4.6. Блок-схема модуля АЦП

4.5.2 Управление преобразованием от секвенсоров Секвенсоры обеспечивают автоматическое выполнение серии преобразований при

получении одной команды «Старт». Результаты отдельных преобразований сохраняются в соответствующих регистрах результата: результат первого в ADCRESULT0, второго - в ADCRESULT1 и т.д.

АЦП может работать в последовательном или одновременном режимах выборки; для каждого преобразования (или пары преобразований в одновременном режиме выборки) текущее состояние CONVxx автомата секвенсора указывает, сигнал с какого вывода (или пары) должен быть выбран и преобразован. Входы АЦП могут быть выбраны в любом порядке, в частности многократно может быть выбран один и тот же вход. Номера выбираемых каналов задаются 4-разрядными полями CONVxx в регистрах

ADCCHSELSEQ1ADCCHSELSEQ4.

Преобразование может выполняться в непрерывном режиме, режим устанавливается записью 1 в бит CONT_RUN регистра ADCTRL1. В этом случае после выполнения числа преобразований, установленного в MAX_CONV1, в порядке, записанном в регистрах ADCCHSELSEQ1ADCCHSELSEQ4, цикл преобразований повторяется.

В старт-стоповом режиме работа может синхронизироваться от различных источников. После выполнения группы преобразований, инициированных одним

27

источником, АЦП ожидает запуска от второго источника для преобразования второй группы входных сигналов.

4.5.3 Установка тактовой частоты АЦП производится записью 4 разрядов ADCCLKPS в регистре ADCTRL3. Частота периферийных тактов делится на установленное в этих разрядах число перед поступлением на синхронизацию АЦП.

Для управления длительностью выборки используются разряды ACQ_PS [3:0] регистра ADCTRL1, длительность выборки равна установленному в этих разрядах числу +1 тактов АЦП.

4.5.4 Программа самокалибровки разработана Texas Instruments и загружена в блок OTPпамяти при изготовлении. АЦП самокалибруется при запуске без участия пользователя, из загрузочного модуля памяти вызывается процедура инициализации регистров ADCREFSEL, ADCOFFTRIM, где хранятся калибровочные данные.

Примечание. При запуске в интегрированной среде при отладке программ Boot ROM обходится и самокалибровка автоматически не происходит.

4.5.5 Выбор опорного источника По умолчанию АЦП работает с опорой на внутренний источник опорного

напряжения. При необходимости другой шкалы могут быть использованы опорные источники с напряжениями 2,048 В, 1,5 В, 1,024В, подключаемые в выводу ADCREFIN микросхемы. Величина в регистре ADCREFSEL определяет выбранный опорный источник.

4.5.6 Доступ к АЦП по шине DMA

Регистры результатов АЦП с адресами 0х0B00 - 0х0B0F расположены в периферийном фрейме 0 и доступны по шине DMA одновременно с доступом от процессорного ядра CPU.

Регистры результатов АЦП с адресами 0х7108 - 0х710F расположены в периферийном фрейме 2 и по шине DMA недоступны.

АЦП вырабатывает в секвенсоре импульс, который передается в DMA-модуль и может быть использован для синхронизации считывания информации из регистров результата.

Лекция №5 «Цифровой сигнальный контроллер TMS320F28335. Периферийные устройства интерфейсов eCAN, McBSP, I2C, SPI, SCI»

5.1 Модуль SPI последовательного периферийного интерфейса

5.1.1Интерфейс SPI (serial peripheral interface) разработан компанией Motorola в 1979 году как внешняя шина микроконтроллеров семейства 68000.

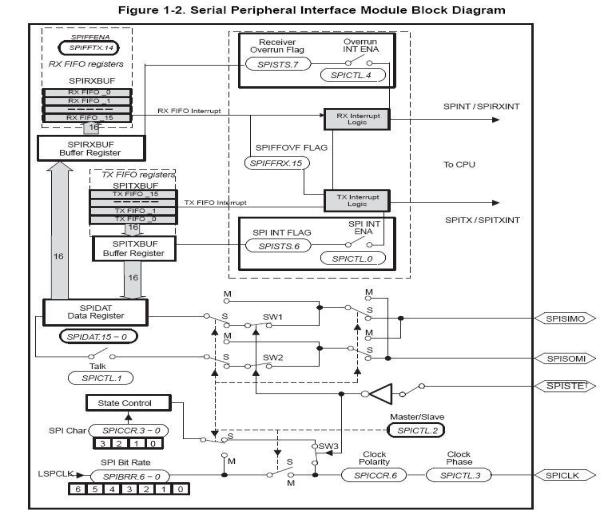

Модуль высокоскоростного синхронного последовательного интерфейса используется для связи контроллера с периферийными устройствами или другим контроллером. Может использоваться в режиме ведущего (master) или ведомого (slave).

Модуль высокоскоростного синхронного последовательного интерфейса обеспечивает передачу и прием слов запрограммированной длины (от 1 до 16 бит данных) с запрограммированной скоростью – возможны 125 различных частот, максимальная тактовая частота – 12,5 МГц.

5.1.2Для подключения к SPI интерфейсу контроллер использует 4 вывода микросхемы, которые могут также быть конфигурированы как GPIO:

SPISOMI – выход ведомого или вход ведущего; SPISIMO – вход ведомого или выход ведущего;

SPISTE – разрешение передачи для ведомого (инверсия);

28

SPICLK – тактовые импульсы.

Допускает четыре различных режима синхронизации передачи и приема с фронтами тактовых импульсов, работу в режиме приема и передачи одновременно (но прием и передача синхронно с разными фронтами тактовых импульсов); содержит FIFO с глубиной 16 уровней на прием и передачу.

Управляется 12-ью 16-разрядными регистрами, расположенными в периферийном фрейме 2 начиная с адреса 7040h. Блок-схема модуля SPI и основные связи между его узлами приведены на рис.5.1.

Рис.5.1. Блок-схема модуля SPI

5.1.3 Принцип действия При связи между двумя устройствами одно выполняет функции ведущего, другое

ведомого. Ведущее устройство инициирует передачу данных выдачей тактовых импульсов, под действием которых сдвигаются коды, загруженные в сдвиговые регистры обоих устройств и биты этих кодов последовательно поступают в линии связи. Сдвиг информации происходит по переднему фронту, а фиксация – по заднему фронту тактовых импульсов, в результате оба устройства одновременно и передают и принимают данные.

Ведущий готов начать передачу в любой момент, поскольку он контролирует выдачу тактовых импульсов. Он выдает на выход данные, находящиеся в старшем разряде сдвигового регистра, аналогично передает данные ведомый. Ведущий записывает полученный от ведомого старший значащий бит в младший разряд сдвигового регистра, который освободился в данном такте. После заданного числа тактов передаваемое слово полностью вытеснится из сдвигового регистра и заместится принятым, которое будет переписано в буфер для передачи в CPU.

29

В типовом случае сигнал SPISTE выполняет роль чип-селекта для ведомого, перед передачей ведущий устанавливает его в 0, после окончания обмена – в 1. Единичным состоянием сигнала SPISTE сдвиговый регистр останавливается, а вывод выхода устанавливается в высокоимпедансное состояние, позволяя подключение к шине многих ведомых, хотя активным может быть только один из них.

5.1.4 Прерывания модуля SPI

Прерывания модуля конфигурируются 4 битами в двух управляющих регистрах:

-битs SPI INT ENA и OVERRUN INT ENA – осуществляет активацию прерываний от модуля;

-бит SPI INT FLAG - статусный флаг, индицирующий состояния приемного буфера и готовность к считыванию информации;

-бит RECEIVER OVERRUN FLAG – флаг сигнализирует, что новая информация загружается до того, как считана предыдущая.

5.2Модуль I2C межмикросхемного последовательного интерфейса

5.2.1 Интерфейс I2C (inter-integrated circuit) разработан компанией Philips в 1982 году для связи микроконтроллера с периферией в телевизоре. Модуль интерфейса I2C используется для связи контроллера с периферийными устройствами или другим контроллером, имеющими соответствующий интерфейс версии 2.1 и подключенными к шине I2C.

Интерфейс I2C – это протокол с многими ведущими и ведомыми, использующий только две сигнальные линии:

-линия последовательных данных SDA;

-линия синхросигнала SCL.

Модуль высокоскоростного синхронного последовательного интерфейса может использоваться в режиме ведущего (master) или ведомого (slave) и обеспечивает передачу и прием слов запрограммированной длины (от 1 до 8 бит данных) с запрограммированной скоростью.

5.2.2 Особенности модуля:

-режимы 7- и 10-битной адресации;

-режим общего вызова;

-режим стартового байта;

-режим свободного формата данных;

-поддержка множества ведущих (передатчиков) и ведомых (приемников);

-скорость передачи данных от 10 до 400 килобит в секунду (режим High-Speed не поддерживается);

-содержит FIFO на прием и передачу с объемом 16 байт каждое;

-модуль может выключаться.

Блок-схема модуля I2C и основные связи между его узлами приведены на рис.5.2.

30