Структура процессора

Разрядность и тип системы команд. Для проведения мысленного эксперимента по построению процессора можно выбрать разрядность в 32 бита, трехадресную систему команд и объем регистрового файла равный 256 регистрам. В этом случае формат команды получается наиболее простым и красивым – команда состоит из четырех байт, один из которых определяет код операции, а три других – регистры, участвующие в этой операции.

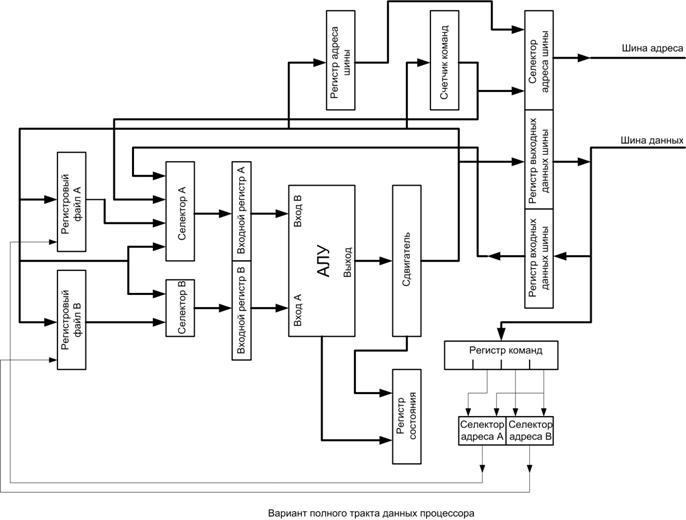

Одновременная выборка двух аргументов. Возвращаясь к блок-схеме процессора, следует обратить внимание еще на некоторые обстоятельства. Первое из них заключается в том, что перед выполнением каждой команды необходимо извлечь оба ее аргумента из регистрового файла, а поскольку за один прием можно извлечь из регистрового файла только одно слово, придется это делать в два приема, что потребует лишнего шага при выполнении каждой команды. Чтобы избежать этого, можно предусмотреть две копии регистрового файла, имеющих одинаковое содержимое. Тогда станет возможно извлекать из регистрового файла одновременно оба аргумента – один из одной его копии, а другой – из другой. Соответственно, в каждую копию регистрового файла должен быть передан адрес регистра из соответствующего байта регистра команд. Запись в регистровый файл должна осуществляться одновременно в обе копии, по одному и тому же адресу. Для коммутации адресов регистрового файла нужно предусмотреть дополнительно два селектора адресов регистров.

Путей данных недостаточно . Также следует вспомнить про второе обстоятельство, которое заключается в том, что для некоторых из необходимых дополнительных узлов, необходимо предусмотреть возможность не только передачи данных из основного тракта данных в эти узлы, но и в обратном направлении. С одной стороны, если выбрать вариант построения схемы с использованием дополнительных селекторов, для этого потребуется два дополнительных селекторных входа, поскольку остались два узла, для которых не предусмотрена возможность передачи данных из этих узлов в основной тракт данных: счетчик команд и регистр входных данных шины. С другой стороны, входные регистры АЛУ можно использовать не только в качестве временного хранилища при передаче данных из регистрового файла в АЛУ, но и из других узлов процессора, а также для временного хранения данных в процессе выполнения команды. Если между регистровым файлом и входными регистрами АЛУ предусмотреть два 32-разрядных селектора, можно решить обе этих задачи.

И вот теперь, с учетом этих обстоятельств можно нарисовать более полную блок-схему тракта данных процессора с подключенными к нему необходимыми дополнительными узлами:

Такой тракт данных, уже должен позволять выполнять большинство необходимых действий. Конечно, этот вариант не является окончательным – в процессе разработки полной системы команд и пошагового разбора выполнения каждой команды может потребоваться внесение каких-либо изменений и дополнений.

Управление процессором

Что делать с управляющими сигналами? Воспользовавшись блок-схемой процессора можно нарисовать точную и подробную электрическую схему, на которой будет показано, как необходимо соединить входные и выходные сигналы данных всех узлов процессора. Однако эти узлы имеют не только сигналы данных, но и управляющие сигналы, о которых блок-схема не дает никакого представления, и прежде чем рисовать такую схему, нужно понять, что делать с этими управляющими сигналами. Разбираться в этом вопросе следует начать с одного довольно простого дела. Нужно аккуратно выписать в таблицу список изображенных на блок-схеме узлов, а для каждого узла определить список сигналов, необходимых для управления этим узлом. Тогда получится примерно следующая таблица:

|

Узел |

Список сигналов |

Примечание |

|

АЛУ |

Выбор операции 0 |

См. таблицу функций АЛУ |

|

Выбор операции 1 | ||

|

Выбор операции 2 | ||

|

Выбор операции 3 | ||

|

Выбор операции 4 | ||

|

Сдвигатель |

Выбор сдвига 0

|

00 – без сдвига 01 – сдвиг на бит влево 10 – сдвиг на бит вправо |

|

Выбор сдвига 1 | ||

|

Регистровый файл А |

Запись в файл А |

= запись в файл |

|

Регистровый файл В |

Запись в файл В |

= запись в файл |

|

Селектор А |

Выбор входа А 0 |

00 – регистровый файл 01 – выход сдвигателя 10 – счетчик команд 11 – регистр данных шины |

|

Выбор входа А 1 | ||

|

Селектор В |

Выбор входа В 0 |

0 – регистровый файл 1 – выход сдвигателя |

|

Буферный регистр А |

Запись в регистр А |

|

|

Буферный регистр В |

Запись в регистр В |

|

|

Счетчик команд |

Запись в счетчик команд |

|

|

Увеличение счетчика команд |

= (чтение команды) и (ответ шины) | |

|

Сброс счетчика команд |

= общий сброс | |

|

Регистр адреса шины |

Запись адреса шины |

|

|

Селектор адреса шины |

Выбор источника адреса |

= чтение команды |

|

Разрешение выдачи адреса на шину |

= (чтение данных по шине) или (чтение команды по шине) или (запись по шине) | |

|

Регистр входных данных шины |

Запись в регистр входных данных шины |

= ответ шины |

|

Регистр выходных данных шины |

Запись в регистр выходных данных шины |

|

|

Разрешение выдачи данных на шину |

= запись по шине | |

|

Регистр команд |

Запись в регистр команд |

= (чтение команды) и (ответ шины) |

|

Сброс регистра команд |

= общий сброс | |

|

Регистр состояний |

Запись в регистр состояний |

|

|

Сброс регистра состояний |

| |

|

Шина |

Запись по шине |

|

|

Чтение команды по шине |

| |

|

Чтение данных по шине |

| |

|

Запрос шины |

| |

|

Селектор адреса A |

Выбор входа |

= фаза выполнения команды |

|

Селектор адреса B |

Выбор входа |

= фаза выполнения команды |

Таким образом, если рассматривать внешнюю шину как узел процессора, всего получается 18 узлов, для которых необходимо 33 управляющих сигнала. Некоторые из этих сигналов всегда должны совпадать друг с другом и могут быть объединены в один управляющий сигнал. Другие сигналы представляют собой простейшую логическую комбинацию других сигналов и могут быть получены при помощи элементарных логических элементов из других сигналов.

Передача данных по шине. Для гипотетического процессора целесообразно использовать шину с максимально простыми правилами передачи данных. Для примера, можно предположить, что шина состоит из 32 разрядной шины адреса (два младших разряда всегда равны нулю) и 32 разрядной шины данных. Передача по шине осуществляется 32-разрядными словами. Если необходимо считать данные с какого-то устройства на шине, например из оперативной памяти, процессор должен сначала выдать на шину адреса адрес слова, которое он хочет прочитать, установить сигнал типа операции в состояние «чтение», и затем установить сигнал запроса шины. Через некоторое время после этого он должен получить сигнал ответа шины, который означает, что на шине данных присутствует необходимая информация. Получив сигнал ответа шины, процессор записывает данные в регистр входных данных шины, и только после этого убирает с шины адрес и сигнал запроса. При записи процессор должен выдать данные на шину одновременно с адресом, а сигнал ответа шины означает, что данные приняты устройством и их можно убрать с шины. Использование таких управляющих сигналов и правил их формирования гарантирует, что данные по шине будут передаваться без искажений.