ВТиИТ лекции

.pdf

Данная схема является, пожалуй, наиболее удачной и широко распространенной, поскольку:

в ней не используются сопротивления с сильно отличающимися номиналами как в схеме с весовыми резисторами и поэтому она более технологична при изготовлении ЦАП в виде интегральной микросхемы;

в отличие от схемы с весовыми источниками тока позволяет получать (при использовании в качестве ключей полевых транзисторов) ЦАП умножающего типа.

Последовательные или интегрирующие ЦАП

Собственно ЦАП данного типа представляет собой электрический ключ, периодически замыкаемый и размыкаемый, и формирующий импульсы. Преобразователи данного типа могут работать либо по принципу преобразования частоты формируемых импульсов в

напряжение (ЧИМ), либо с широтно-импульсной модуляцией (ШИМ) - формируя сигнал. |

|

|||||||

После того, как сформирован импульсно |

|

s |

|

|

||||

модулированный |

сигнал, |

его |

достаточно |

|

|

Фильтр |

|

|

проинтегрировать |

(используя |

фильтр, |

Uоп |

|

U1 |

Uвых |

||

подавляющий высокочастотную составляющую) |

|

|

|

|

||||

для получения среднего значения. В качестве |

|

|

|

|

||||

интегратора |

в таких ЦАП |

зачастую выступает |

U1 |

|

Uвых |

|

||

нагрузка. Лампа накаливания, нагревательный |

|

|

||||||

|

|

|

||||||

элемент, |

коллекторный |

электродвигатель |

|

|

|

|

||

постоянного |

тока |

является |

прекрасными |

tи |

Т |

|

|

|

интеграторами. |

|

|

|

2Т |

t |

|||

|

|

|

|

|

||||

Для формирования импульсной последовательности с управляемой частотой или длительностью может быть применен таймер либо использована программная реализация этой задачи.

Последовательные ЦАП более медленные, чем параллельные, как правило менее точные, но существенно более дешевые поскольку в некоторых случаях вообще не требуют никаких дополнительных периферийных устройств кроме порта.

Аналого-цифровые преобразователи Параллельные АЦП

Uоп

R1

DA1

R2

DA2

R3

DA3

R4

DA4

R5

DA5

R6

DA6

R7

DA7

R8

DA8

R9

Uвх

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A7 |

|

CD |

D0 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

A6 |

|

|

D1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

A5 |

|

|

D2 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

A4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входной сигнал подается на неинвертирующие входы компараторов (DA1-DA8), соединенные параллельно. На инвертирующие входы этих компараторов подаются опорные напряжения с делителя напряжений на сопротивлениях R1R9, на каждый компаратор подается опорное напряжение, отличающееся от соседних на шаг квантования. Количество включенных компараторов преобразуется в двоичный код при помощи шифратора СD.

Достоинства

-высокое быстродействие, достигающее десятков наносекунд.

Недостатки

-большая сложность (количество компараторов в схеме равно чис-

лу уровней квантования, и равно 2n где n - разрядность выходного кода

-высокая стоимость;

-невысокая точность (8-10 двоичных разрядов)

Особенности сопряжения с микропроцессорными системами

Поскольку такие АЦП более быстродействующие, чем микропроцессорная система, то данные сначала записываются с выхода АЦП в быстродействующее буферное ОЗУ

|

|

АЦП последовательных приближений |

|

|

|

|

||||||||||||

|

|

|

|

|

Uвх |

|

|

|

|

|

U |

|

|

|

|

|

||

|

“Пуск” |

|

|

|

|

|

|

|

|

Uш |

|

|

|

|

|

|

||

|

|

|

|

1 |

|

|

|

|

|

Uвх |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Счетчик |

2 ЦАП |

|

|

|

|

|

|

|

|

|

|

|

|

||||

G |

fт |

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

n |

|

|

|

|

|

|

|

|

|

|

Uкв |

|

|

|

“Стоп” |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Uш – напряжение шкалы ЦАП, n – число разрядов счетчика и ЦАП, (2n – 1) – число тактов, за |

||||||||||||||||||

которые достигается на выходе ЦАП Uш, тогда шаг квантования U |

кв |

|

Uш . |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

2n 1 |

|

|

|||

Число тактов, за которое достигается Uвх равно |

U |

вх |

U |

вх |

(2n 1) |

|

|

|

|

|

|

|||||||

|

|

Uш |

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

Uкв |

|

|

|

|

|

|

|

|

|||

Время измерения T |

|

U |

вх |

(2n 1) |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

изм |

|

|

Uшfт |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

АЦП поразрядного взвешивания |

|

|

|

|

|

|||||||||

Пуск |

S T |

|

|

|

|

|

|

|

|

|

|

Ux |

|

|

|

|

||

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

RG |

|

|

S |

T |

D0 D/A |

|

|

|

|

||||

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

_ |

|

D0 |

|

R |

|

|

|

|

|

|

|

|

|

||

|

G |

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

S |

T |

D1 |

|

|

|

|

|

|

||

|

|

|

|

|

D1 |

& |

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

S |

T |

|

|

|

|

Uш |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

|

|

8 |

|

|

|

|

|

|

|

|

|

& |

|

R |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

D2 |

|

|

|

|

|

|

|

7 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

Работа АЦП данного типа основана на алгоритме половинного де- |

5 |

|

Ux |

||||||||||||||

|

|

|

||||||||||||||||

|

|

|

|

|||||||||||||||

ления или дихотомии. |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

||

|

АЦП поразрядного взвешивания состоит из компаратора, на один |

3 |

|

|

||||||||||||||

вход которого подается входное напряжение, а на другой - сигнал от |

|

|

||||||||||||||||

ЦАП. Схема из сдвигового регистра и блокировочных триггеров служит |

2 |

|

|

|||||||||||||||

для управления ЦАП - выработки последовательности кодов, прибли- |

|

|

||||||||||||||||

жений окончательного значения преобразования. |

|

|

|

|

|

|

|

1 |

|

|

||||||||

|

Первое приближение |

равно половине |

максимального значения, |

|

Т |

|||||||||||||

далее выясняется, больше входное напряжение этого значения или |

|

|

||||||||||||||||

1 |

2 |

3 |

||||||||||||||||

меньше, в следующем цикле интервал в котором находится входное на- |

||||||||||||||||||

пряжение делится еще пополам и т.д. Каждый цикл приближения дает один правильный двоичный разряд результата, начиная со старшего.

Достоинства и недостатки

Данный способ построения АЦП имеет по сравнению с интегрирующими и параллельными АЦП среднее быстродействие - типичное значение времени преобразования - 1...10 мкс, и среднюю точность - 10...14 двоичных разрядов. К недостаткам данного метода относится большая чувствительность к импульсным помехам, к достоинствам - хорошее согласование по времени измерения с типичными микропроцессорными системами, невысокая стоимость и сложность.

Интегрирующие АЦП

Общие особенности

АЦП данного типа осуществляют преобразование в два этапа.

На первом этапе входной аналоговый сигнал интегрируется и это проинтегрированное значение преобразуется в импульсную последовательность. Частота следования импульсов в этой последовательности или их длительность бывает промодулирована проинтегрированным значением входного сигнала.

На втором этапе эта последовательность импульсов преобразуется в цифровой код - измеряется ее частота или длительность импульсов.

Общие достоинства

АЦП данного типа нечувствительны к импульсным помехам.

АЦП данного типа нечувствительны к периодическим помехам если их период в целое число раз меньше периода интегрирования.

В результате, АЦП данного типа являются наиболее точными - типичная точность - 4...6 десятичных знаков, что соответствует 14...20 двоичным разрядам.

При работе АЦП данного типа в составе микропроцессорной системы возможна программная реализация части измерительной процедуры, а именно второго этапа - измерения временных характеристик последовательности импульсов, что упрощает преобразователь.

Общие недостатки

Преобразователи данного типа являются наименее быстродействующими из всех - типичное время преобразования - 1 - 1000 мс.

АЦП с двойным интегрированием

UX |

|

Rэт |

|

|

|

|

|

С |

||||

|

|

|

|

|

|

|

|

|

|

нуль-компаратор |

||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rэт

Tи1

ФИ код

|

пуск |

|

UUвх2 |

|

вх1 |

tи |

|

t1 |

t2 |

|

N2 |

|

N1 |

Nи |

|

G

G

счетчик

счетчик  стоп

стоп

Это двухтактный преобразователь с заданной длительностью первого такта.

В течение первого такта происходит заряд интегрирующего конденсатора. Напряжение на нем в конце такта пропорционально интегралу входного напряжения.

Во время второго такта преобразования происходит разряд конденсатора заданным током до нулевого напряжения. Длительность этого такта и есть выходной сигнал преобразователя.

Во время второго такта преобразования происходит разряд конденсатора заданным током до нулевого напряжения. Длительность этого такта и есть выходной сигнал преобразователя.

Достоинством данного варианта построения интегрирующего АЦП является не зависимость результата преобразователя от емкости интегрирующего конденсатора и пропорциональное изменение длительности второго такта при изменении длительности первого.

Это позволяет снизить требования к точности тактовой частоты.

Сигма-дельта АЦП

Воснове идеи сигма-дельта АЦП лежит принцип одноразрядной дельта-модуляции, когда текущее значение сигнала сравнивается с предыдущим, и если сигнал превысил предыдущий отсчет на некое порогового значение, он кодируется 1, если уменьшился – 0. При этом предполагается, что входной сигнал остается неизменным во время всего цикла преобразований для одной выборки (выборка или отсчет – сформированное на выходе АЦП мгновенное цифровое значение измеряемого сигнала). Такая обработка требует достаточно больших скоростей дискретизации, как правило – в 20-40 раз выше максимальной частоты входного сигнала.

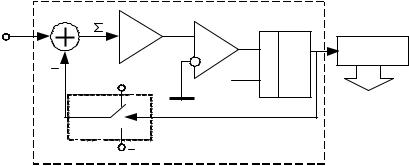

Впростейшем случае сигма-дельта АЦП включает в себя сигма-дельта модулятор, выполняющий преобразование аналогового сигнала в цифровую последовательность, и выходной фильтр (счетчик), преобразующий цифровую последовательность из модулятора в окончательный цифровой код.

Как и любой АЦП, сигма-дельта АЦП выдает оцифрованные значения сигнала в долях диапазона измерения. Измеряемый сигнал должен находиться в диапазоне опорного напряжения от +Uоп до –Uоп (относительно некоего установленного уровня "0", численно рав-

ного половине диапазона измерения). Если разрядность АЦП – m бит, то весь этот диапазон разбит на интервалы (кванты) 2Uоп/2m. Очевидно, что значения +Uоп и –Uоп могут быть любыми, не обязательно отрицательными. Для удобства рассуждений будем полагать, что уровень "0" соответствует напряжению 0 В.

Простейший сигма-дельта модулятор состоит из сумматора, интегратора, компаратора, триггера-защелки (D-триггера) и одноразрядного ЦАП. Одноразрядный ЦАП фактически представляет собой коммутатор, который в зависимости от входного сигнала (1 или 0) выдает напряжение +Uоп или –Uоп, соответственно.

Uвх |

|

U |

Uи |

|

|

+ |

|

D TT |

счетчик |

||

|

|

|

|||

|

|

+Uоп |

fmod |

C |

код |

|

|

ЦАП |

|

Кi |

|

|

|

|

|

||

|

|

1-bit |

|

|

|

|

|

Uоп |

модулятор |

|

|

Перед началом вычисления новой выборки напряжения на выходе интегратора (Uи) и на выходе ЦАП равны нулю. Сигнал с выхода сумматора UΣ поступает на интегратор, где суммируется с предыдущим значением интегратора (т.е. для i-ой итерации Uи(i) = Uи(i–1) + UΣ. В начальный момент входной сигнал Uвх без изменений поступает на интегратор, поскольку на другом входе сумматора сигнал равен 0 (Uи(0) = Uвх).

Компаратор сравнивает выходное значение интегратора Uи с уровнем "0" и выдает 1, если Uи ≥ 0, и 0 при Uи < 0. Сигнал с компаратора поступает в выходной регистр, образуя последовательность одноразрядных цифровых отсчетов (выборка модулятора). Также этот сигнал попадает в ЦАП, который в зависимости от его уровня выдает +Uоп или –Uоп. В сумматоре это значение вычитается из входного сигнала Uвх и складывается с Uи в интеграторе. После чего процесс многократно повторяется.

Очевидно, что значение Uи в ходе оцифровки сигнала будет то нарастать, то убывать. Например, если Uоп = 1 В, а Uвх = 0,6 В, то напряжение в интеграторе Uи будет последова-

тельно принимать значения 0,6; 0,6 + (0,6 – 1) = 0,2; 0,2 + (0,6 – 1) = –0,2; –0,2 + (0,6 + 1) = 1,4; 1,4 + (0,6 – 1) = 1; 1 + (0,6 – 1) = 0,6 и т.д. Через пять итераций Uи будет равно Uвх = 0,6 В. На выходе компаратора и D-триггера при этом сформируется последовательность Ki=1101111011... В полученной последовательности присутствует циклически повторяющийся сигнал 11011. Для других значений входного сигнала число символов в цикле

(длина циклической последовательности) будет другим (см. таблицу). Нетрудно заметить, что если Uвх = –Uоп, то выходная последовательность будет состоять только из нулей, а если Uвх = +Uоп – только из единиц. При Uвх = 0 на выходе D-триггера будет 101010...

|

N такта |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

Uвх = 0,5В |

UΣ, В |

0,5 |

-0,5 |

-0,5 |

1,5 |

-0,5 |

-0,5 |

-0,5 |

1,5 |

-0,5 |

-0,5 |

-0,5 |

1,5 |

-0,5 |

Uи, В |

0,5 |

0 |

-0,5 |

1 |

0,5 |

0 |

-0,5 |

1 |

0,5 |

0 |

-0,5 |

1 |

0,5 |

|

|

Ki |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

Uвх = 0,6В |

UΣ, В |

0,6 |

-0,4 |

-0,4 |

1,6 |

-0,4 |

-0,4 |

-0,4 |

-0,4 |

1,6 |

-0,4 |

-0,4 |

-0,4 |

-0,4 |

Uи, В |

0,6 |

0,2 |

-0,2 |

1,4 |

1 |

0,6 |

0,2 |

-0,2 |

1,4 |

1 |

0,6 |

0,2 |

-0,2 |

|

|

Ki |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

Uвх = 0В |

UΣ, В |

0 |

-1 |

1 |

-1 |

1 |

-0,3 |

-0,3 |

-0,3 |

-0,3 |

-0,3 |

-0,3 |

1,7 |

-0,3 |

Uи, В |

0 |

-1 |

0 |

-1 |

0 |

1,2 |

0,9 |

0,6 |

0,3 |

0 |

-0,3 |

1,4 |

1,1 |

|

|

Ki |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

Математически механизм работы модулятора можно представить следующим образом. Пусть значение Uи в ходе преобразования k раз было меньше "0" и n раз больше или равным нулю; т.е. n + k = N, где N – общая длина кодовой последовательности для одной выборки. Очевидно, что Uи(N) = Uвх + n(Uвх – Uоп) + k(Uвх + Uоп); Uи(0) = Uвх.

Предположим, что через какое-то число итераций N ≠ 0 напряжение на интеграторе вновь принимает исходное значение: Uи(N) = Uвх. Тогда можно записать:

Uвх = Uвх (1 + n + k) + Uоп(k – n);

n k

Uвх Uоп n k Uоп

2n n k |

|

|

|

|

|

2n |

|

n k |

|

2n |

|

|

||||

|

|

|

|

U |

оп |

|

|

|

|

U |

оп |

|

1 |

, или |

||

n k |

n k |

n k |

|

|||||||||||||

|

|

|

|

|

|

N |

|

|

||||||||

|

|

Uвх |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uоп |

|

n |

|

|

|

|

|

|

|

(1) |

||||

|

|

|

|

|

|

|

|

|

|

|

||||||

2 |

|

N |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||||||

Таким образом, отношение числа единиц к общей длине циклической последовательности n/N однозначно определяет измеряемое напряжение Uвх как часть диапазона измерений Uоп.

Цикличность изменения напряжения в интеграторе обусловлена отрицательной обратной связью в сигма-дельта модуляторе. Длительность цикла зависит от соотношения значений Uвх, Uоп и точности их представления. Ее можно определить из формулы (1) при условии, что N и n – целые числа. Например, при Uвх = 0,7 В наименьшее значение N = 20, соответственно n = 17.

Если длина выборки сигнала в модуляторе достаточно велика, можно гарантировать, что она окажется в несколько раз больше самой длинной циклической последовательности N. Поэтому даже если она не кратна N, все равно "лишние" отсчеты (биты) существенно не исказят статистику и не повлияют на результат измерения Uвх.

Таким образом, с помощью всего лишь одноразрядного преобразования в заданном диапазоне напряжений можно измерить входной сигнал с любой точностью. Но очевидно, что чем выше точность, тем больше отсчетов необходимо в выборке модулятора для одного сигнала. И если частота следования многоразрядных выборок fs (т.е. скорость выдачи результатов измерения сигнала АЦП) должна удовлетворять теореме Котельникова и по крайней мере вдвое превышать ширину полосы частот сигнала F (fs > 2F), то частота одноразрядных отсчетов гораздо выше: fmod = Kfs, где К – коэффициент передискретизации (избыточной дискретизации). Коэффициент К может варьироваться в достаточно широких пределах, от единиц до тысяч. Именно этот факт и является одним из существенных ограничителей частотных свойств сигма-дельта АЦП, ставя в обратную зависимость их разрешение (число разрядов в выборке) и диапазон рабочих частот.

Сформированную выходную двоичную последовательность модулятора необходимо преобразовать в двоичный код заданной разрядности m (меньшей, чем в исходной выборке).

Простейший способ - это использовать счетчик фиксированной разрядности m (например, 8- разрядный). Счетчик на каждой итерации (т.е. с частотой сигма-дельта модулятора fmod = Kfs) опрашивает выход компаратора и суммирует число единиц в последовательности длиной 2m – 1. В случае m = 8 такой счетчик будет обрабатывать выборки длиной 256 бит, накапливая значение n из формулы (1). Фактически он будет формировать 255 отсчетов на диапазон –Uоп… +Uоп, представляя их в дополнительном коде: 00000000 = –Uоп; 10000000 = 0 В, 11111111 = (254/255)Uоп. Причем счетчик не только преобразует (кодирует) выборку модулятора, но и сокращает число отсчетов, понижая частоту конечной выборки. Операция сокращения числа отсчетов (прореживания выборки) называется децимацией.

В реальных сигма-дельта АЦП вместо двоичных счетчиков используют цифровые фильтры-дециматоры нижних частот с конечной импульсной характеристикой (КИХфильтры).

Сигма-дельта АЦП получили широкое распространение в тех областях измерительной техники, где не требуются большие частоты дискретизации, но важно обеспечить высокую точность измерений. Выпускаемые промышленностью сигма-дельта АЦП имеют разрядность 16-24 бит и частоту дискретизации до 10МГц.

Сравнение сигма-дельта АЦП с АЦП многотактного интегрирования показывает значительные преимущества первых. Прежде всего, линейность характеристики преобразования сигма-дельта АЦП выше, чем у АЦП многотактного интегрирования равной стоимости. Это объясняется тем, что интегратор сигма-дельта АЦП работает в значительно более узком динамическом диапазоне, и нелинейность переходной характеристики усилителя, на котором построен интегратор, сказывается значительно меньше. Емкость конденсатора интегратора у сигма-дельта АЦП значительно меньше (десятки пикофарад), так что этот конденсатор может быть изготовлен прямо на кристалле ИМС. Как следствие, сигма-дельта АЦП практически не имеет внешних элементов, что существенно сокращает площадь, занимаемую им на плате, и снижает уровень шумов. К тому же сигма-дельта АЦП начинает давать правильный результат через 3-4 отсчета после скачкообразного изменения входного сигнала, что при величине первой частоты режекции, равной 50 Гц, и 20-разрядном разрешении составляет 6080 мс, а минимальное время преобразования АЦП многотактного интегрирования для 18разрядного разрешения и той же частоты режекции составляет 140 мс. В настоящее время ряд ведущих по аналого-цифровым ИМС фирм, такие как Analog Devices и Burr-Brown, прекратили производство АЦП многотактного интегрирования, полностью перейдя в области АЦ-преобразования высокого разрешения на сигма-дельта АЦП.

Память в вычислительных системах

Классификация типов памяти:

1.По типу доступа

Адресная

Ассоциативная

Последовательная:

FIFO(первый зашел, первый вышел)

LIFO (последний зашел, первый вышел)

циклические

2.По возможности изменения данных

RAM(оперативно запоминающее устройство - ОЗУ)

Статическое

Динамическое

ROM(постоянно запоминающее устройство - ПЗУ)

Масочные (ROM)(M)

С возможностью программирования (EPROM)

С возможностью перепрограммирования (EEPROM)

Flash

3.По энергозависимости

Энергозависимые

Энергонезависимые

Основные параметры памяти

1. |

Информационная емкость памяти (равна числу ячеек памяти) |

||||||||||||

2. |

Структура – определяет, сколько ячеек памяти может считать одновременно |

||||||||||||

|

|

4 kb = 4096*1 = 1024*4 = 512*8 и т.д. |

|||||||||||

3. |

Быстродействие |

||||||||||||

|

|

|

|

|

Установка адреса |

||||||||

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

cs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R/W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DO |

|

|

|

|

|

|

|

|

D |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tвыб |

|

|

|

|

|

|||

|

|

|

|

|

|

||||||||

tвыб = tвыд |

|

|

|

|

|

|

|

|

|

|

|

||

|

- время выборки/выдачи информации на шину данных. |

||||||||||||

4. |

Потребляемая мощность |

||||||||||||

|

n |

|

|

|

|||||||||

|

|

|

|

|

|||||||||

|

|

|

|

A |

|

|

|||||||

|

m |

|

|

|

|

||||||||

|

|

|

|

||||||||||

|

|

|

|

DI |

|

|

|||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

DO |

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

R/W |

|

|

|||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

cs |

|

|

|||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А – адресная шина.

DI – шина входных данных

DO – шина выходных данных

R/W - определяет режим работы чтение/запись. CS – вход «выбор микросхемы».

Структуры запоминающих устройств Адресные структуры

(2D):

|

m |

|

|

DC |

|

|

|

n |

|

|

|

ЗЭ |

ЗЭ |

ЗЭ |

|

ЗЭ |

ЗЭ |

ЗЭ |

n |

cs |

|

|

2 |

ЗЭ |

ЗЭ |

ЗЭ |

|

|

Усилитель R/W |

|

|

R/W |

|

|

|

DI/O |

DI/O |

DI/O |

Матрица запоминающих элементов (ЗЭ) M=k*m, М – информационная емкость в битах, k – число хранимых слов, m – их разрядность.

Дешифратор DC активизирует одну из выходных линий -> считываем или записываем данные (слово) разрядностью m из ЗЭ. Возможно применение только для малой емкости.

3D:

n/2 |

A1 |

cs |

|

A2 |

n/2 |

|

DCy |

|

DCx |

|

|

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

|

1 |

|

1 bit

Только чтение. 1 бит данных за 1 цикл. Выбирается 1 ЗЭ на пересечении активных выходов. Адреса делятся как 2n/2*2n/2=2n