- •1. Общие сведения

- •1.1. Системы счисления

- •2. Цифровая логика

- •2.2. Булева алгебра

- •2.3. Цифровые интегральные схемы

- •2.4. Триггеры

- •2.5 Сдвиговые регистры

- •2.6 Выходные буферные схемы

- •2.7 Счетчики

- •2.8 Сумматоры

- •2.9 Дешифраторы

- •2.10 Мультиплексоры

- •2.11 Шифраторы

- •3. Память

- •3.1 Постоянные запоминающие устройства

- •3.2 Оперативные запоминающие устройства

- •4. Ацп и цап

- •4.1 Общие сведения

- •4.2 Электрические параметры, эксплуатационные характеристики ацп и цап

- •4.3 Классификация ацп

- •4.4 Классификация цап

- •Литература

- •Содержание

2.10 Мультиплексоры

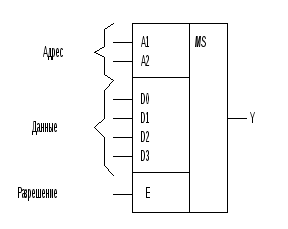

Мультиплексор {multiplexor) — это функциональный узел, осуществляющий подключение (коммутацию) одного из нескольких входов данных к выходу. Номер выбранного входа соответствует коду, поданному на адресные входы мультиплексора. Условное изображение мультиплексора показано на рис. 2.46. Вход Е — разрешающий: при E=1 мультиплексор работает как обычно, при Е=0 выход узла находится в неактивном состоянии, мультиплексор заперт.

Рис. 2.46. Условное изображение мультиплексора

Мультиплексоры 4—1, 8—1, 16—1 выпускаются в составе многих серий и имеют буквенный код КП. Их временные характеристики задаются задержками по трем трактам: вход адреса—выход, вход данных—выход, вход разрешения — выход. Для большинства серий эти величины лежат в пределах (1-2)t своей серии элементов. Универсальный способ наращивания мультиплексоров показан на рис. 2.47.

Рис. 2.47. Каскадное соединение мультиплексоров.

2.11 Шифраторы

Шифратор, или кодер (encoder}, выполняет функцию, обратную дешифратору. Условное изображение шифратора на схемах показано на рис. 2.48. Классический шифратор имеет m входов и n выходов, и при подаче сигнала на один из входов (обязательно на один, и не более) на выходе узла появляется двоичный код номера возбужденного выхода. Число входов и выходов такого шифратора связано соотношением m=2n. Шифратор можно использовать, например, для отображения в виде двоичного кода номера нажатой кнопки или положения многопозиционного переключателя.

Рис. 2.48. Условное изображение шифратора

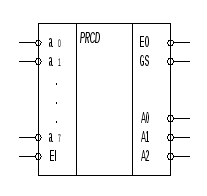

На рис. 2.49 показано условное обозначение 8-входового приоритетного шифратора К155ИВ1. Схема собственно приоритетного шифратора построена на элементах И-ИЛИ-НЕ, имеет входные буферные инвертирующие усилители и ничего принципиально нового к уже изложенному не добавляет. Новым здесь является тракт групповых сигналов. Как видно из рисунка, сигнал Выход разрешения ЕO отражает ситуацию ЕО = (EI) & (В данной группе нет ни одной единицы), а Групповой сигнал (group signal) GS — ситуацию GS = (EI) & (В группе есть хотя бы одна единица). Сигнал ЕI=0 запирает не только выходы адреса АО, A1, А2, но и выходы ЕО и GS.

Рис. 2.49. Условное изображение микросхемы приоритетного шифратора К155ИВ1

На рис. 2.50 показаны примеры использования групповых сигналов при объединении микросхем для наращивания разрядности. Схема на рис. 2.50 кроме адресных выходов A'0—A’3 имеет выходы ЕО' и GS', поэтому ее можно наращивать и далее аналогичным способом.

Рис. 2.50. Наращивание разрядности микросхем приоритетных шифраторов до шестнадцати входов

Микросхема приоритетного шифратора К155ИВ1 (рис. 2.49) имеет две группы входных сигналов: аi и El и три группы выходов: Aj, ЕО, GS. Схема узла такова, что изменение сигналов одной входной группы не влияет на время распространения сигналов по трактам другой входной группы. Поэтому микросхема полностью характеризуется лишь шестью значениями задержки распространения по трактам: ai¾Aj, ai—EO, ai¾GS, EI—Aj, El—EO, EI—GS. Если бы взаимное влияние трактов существовало, то схема характеризовалась бы двенадцатью значениями задержки.

Кроме кодирования состояний переключателей и номеров нажатых клавиш приоритетные шифраторы используются для определения номера устройства, подавшего сигнал запроса на обслуживание в микропроцессорных системах, входя в состав микросхем контроллеров прерываний, например КР580ВН59.