MTK_i_MSS15-01 / Методы моделир.и оптимиз / Лабораторная. работа №3 / Вариант 6

.docЗанятие 6. JK-триггер типа «ведущий-ведомый».

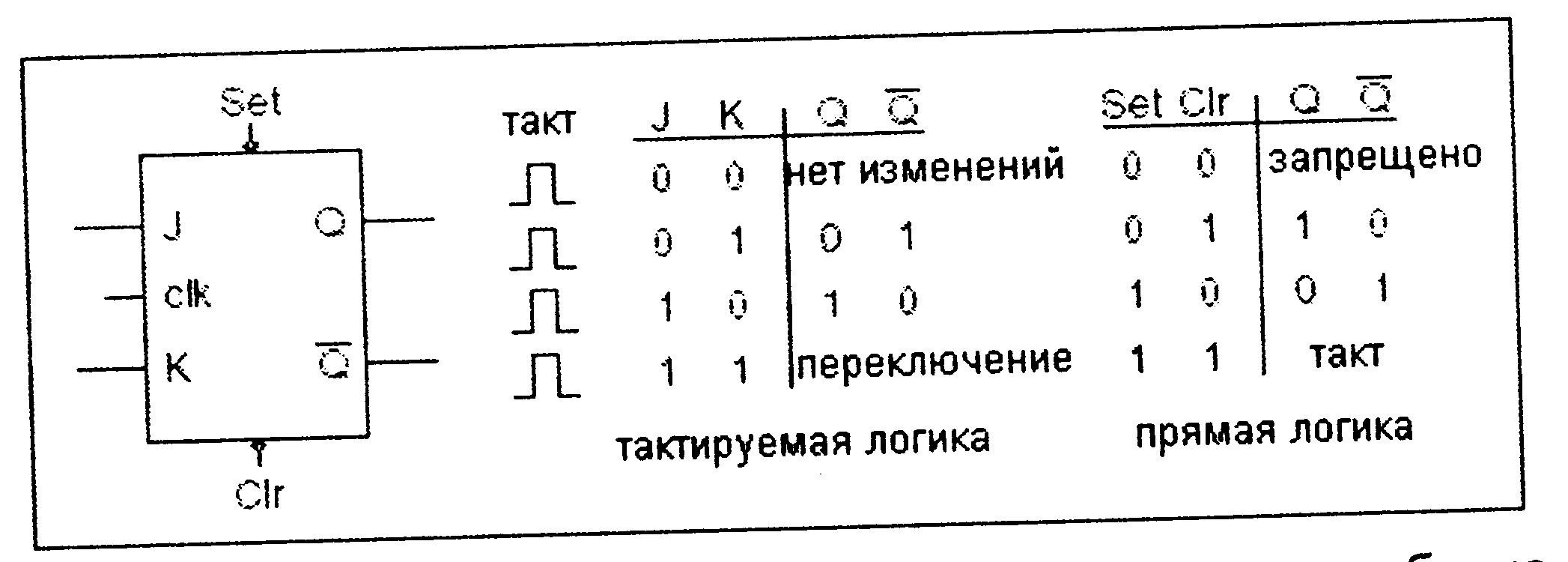

Одним из наиболее важных тактируемых логических устройств является JK-триггер типа «ведущий-ведомый». В отличие от регистра D-типа, который «помнит» только до тех пор, пока не пришел другой тактовый импульс, JK-триггер обладает настоящей памятью. Когда напряжение на входах J и К низкого уровня, состояния выходов Q и Q при тактировании остаются неизменными. Таким образом, информация может быть помещена в выходной разряд и будет храниться до тех пор, пока не будет изменена в будущем. Если на входах J и К действуют противоположные сигналы (0,1) или (1,0), то с приходом очередного тактового импульса выход Q воспроизведет значение J-входа, то есть будет низкого или высокого уровня. Фактически, помещая между входами J и К инвертер, мы получим регистр D-типа. Принципиальная схема JK-триггера и его таблица истинности показаны ниже. Отметим, что JK-триггер может быть установлен в определенное (исходное) состояние прямым вводом определенных сигналов без использования тактируемой логики (прямая логика).

Рисунок 6-1. Схематическое изображение JK триггера и его таблица истинности.

Первая строка таблицы истинности в случае синхронной логики описывает состояние памяти, а другие две комбинации описывают фиксированные состояния. Новое здесь только то, что существует четвертая комбинация (1,1), которая порождает переключаемое состояние. С приходом тактового импульса выходное состояние меняется с 1 на 0 или с 0 на 1. Эту дополнительную функцию часто называют переключателем битов, а триггер (когда состояния J и К входов поддерживаются Высокими) - триггером со счетным входом. Поскольку происходит одно переключение за один цикл, необходимо два тактовых импульса для возращения выхода в исходное состояние.

ЗАДАЧА 27:

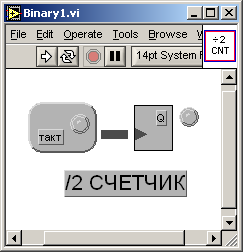

Создайте и запустите программу Binary.vi и наблюдайте работу триггера со счетным входом.

Рисунок 6-2. Модель счетчика-делителя на 2, с использованием подпрограммы Т Flip-Flop.

Каждый раз, когда нажимается кнопка Run, тактовый импульс изменяет состояние с Низкого на Высокое или наоборот.

Сколько раз необходимо нажать кнопку Run, чтобы циклически поменять выходной бит - Низкий - Высокий - Низкий?

Может быть легче для более правильного наблюдения использовать кнопку Run Continuously. Так как для повторения выходного состояния необходимы два тактирующих импульса, триггер со счетным входом делит тактовую частоту на 2 и поэтому называется двоичным счетчиком с делением на два.

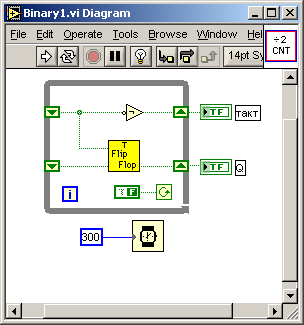

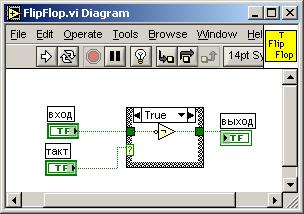

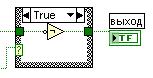

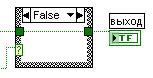

В пакете LabView (см. панель блок-диаграмм и подпрограмму Т flip-flop

) триггер со счетным входом моделируется при помощи структуры Варианта, помещенной в цикл по условию. Верхний сдвиговый регистр и инвертор моделируют генератор тактовых импульсов.

Если выход одного триггера со счетным входом использовать как синхронизирующий вход для второго триггера со счетным входом, то результирующая частота сигнала на выходе пары триггеров будет поделена на 4.

ЗАДАЧА 28:

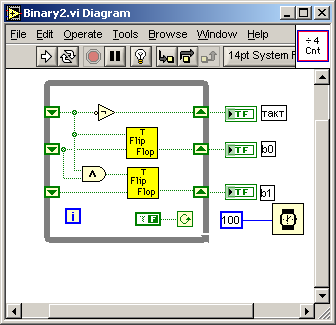

Создайте и запустите виртуальный прибор Binary2.vi.

Рисунок 6-3. Моделирование счетчика-делителя на 4. 146

Если выход первого триггера брать с весом 1, а второго с весом 2, то соответствующие величины в десятичной системе счисления при тактировании образуют следующую последовательность: 0,1,2,3, 0,1,2,3, 0,1,2,3, и т.д. Это двоичный счетчик по модулю 4. Обратите внимание на то, каким образом на блок-диаграмме выход первого триггера складывается с тактирующим сигналом, чтобы сформировать входной сигнал для второго триггера.

Двоичные счетчики

Двоичные счетчики создаются из J-K триггеров подачей на (J.K) входы всех триггеров логической единицы (уровень сигнала Высокий) и подключением выхода каждого предыдущего триггера к тактовому входу последующего. Тактирующий сигнал поступает в цепочку через вход синхронизации первого триггера. Далее результирующий сигнал двигается по цепочке.

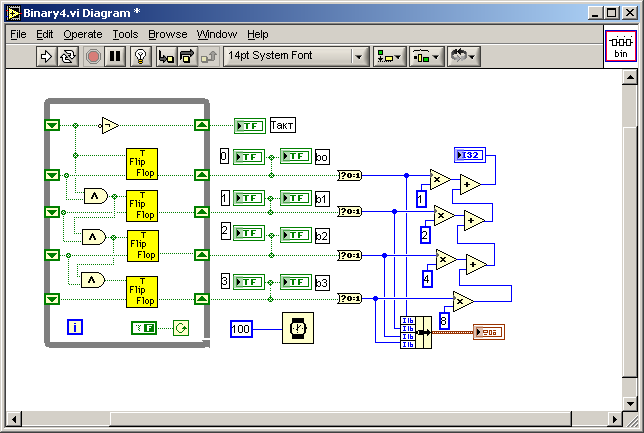

Рисунок 6-4. 4-битовый счетчик, построенный на основе JK триггеров.

В такой конфигурации частота тактирующего сигнала делится на 2 каждый раз, когда сигнал проходит через JK-триггер. Четыре последовательно включенных триггера делят на 24 или 16.

ЗАДАЧА 29:

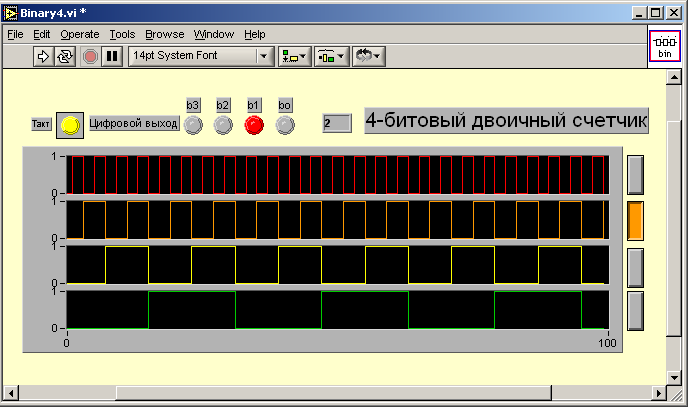

Создайте и запустите виртуальный прибор Binary4.vi, моделирующий представленный двоичный счетчик. Нажимая на кнопку Run, наблюдайте работу счетчика-делителя на 16. Четыре двоичных состояния (Оз, Ог, Qi, Qo) изображаются на светодиодных индикаторах, а эквивалентное значение в десятичной форме изображено в виде числа на лицевой панели. Кроме этого, на отдельных графиках представлены четыре временные диаграммы для выходов Qo - Оз-

Рисунок 6-5. Моделирование 4-битового двоичного счетчика.

Наблюдайте последовательность и заполните следующую таблицу истинности:

Таблица 6-1. 4-битовая двоичная последовательность, сгенерированная счетчиком, и эквивалентная десятичная величина.

|

Тактовый цикл |

О3 |

Q2 |

Q1 |

Q0 |

Десятичный эквивалент |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

2 |

|

|

|

|

|

|

3 |

|

|

|

|

|

|

4 |

|

|

|

|

|

|

5 |

|

|

|

|

|

|

6 |

|

|

|

|

|

|

7 |

|

|

|

|

|

|

8 |

|

|

|

|

|

|

9 |

|

|

|

|

|

|

10 |

|

|

|

|

|

|

11 |

|

|

|

|

|

|

12 |

|

|

|

|

|

|

13 |

|

|

|

|

|

|

14 |

|

|

|

|

|

|

15 |

|

|

|

|

|

|

16 |

1 |

1 |

1 |

1 |

15 |

Заполненная таблица отобразит все двоичные комбинации для 4-битового двоичного счетчика. Если выходам Qo, Qi, Q2, и Q3 присвоить весовые коэффициенты 2°, 21, 22 и 23, то все числа 0-15 в двоичном представлении можно отобразить на четырех выходах. Посмотрите на блок-диаграмму и обратите внимание, каким образом вычисляются эквивалентные десятичные величины.

В шестнадцатиричной системе счисления 16 состояний (0-15) обозначаются как 0...9 и A...F. Такое представление более компактно, и его проще запомнить, чем длинные комбинации битов двоичного представления. Битовые последовательности большой длины разбиваются на группы из четырех битов, называемых полубайтом. Каждый полубайт кодируется как один шестнадцатиричный (HEX) символ.

Например, 16-битовое число 1101 0111 0011 1100 кодируется в HEX как $D73C.

8-битовый двоичный счетчик

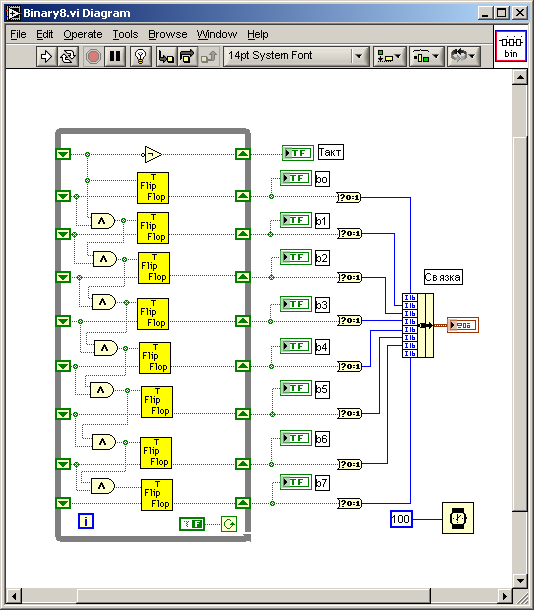

Для данных с более высокими разрядами применяется логическое расширение 4-битового двоичного счетчика. Встроенные контроллеры используют внутреннюю 8-битовую шину данных, а современные процессоры используют 16- и 32-битовые тракты прохождения данных.

ЗАДАЧА 30:

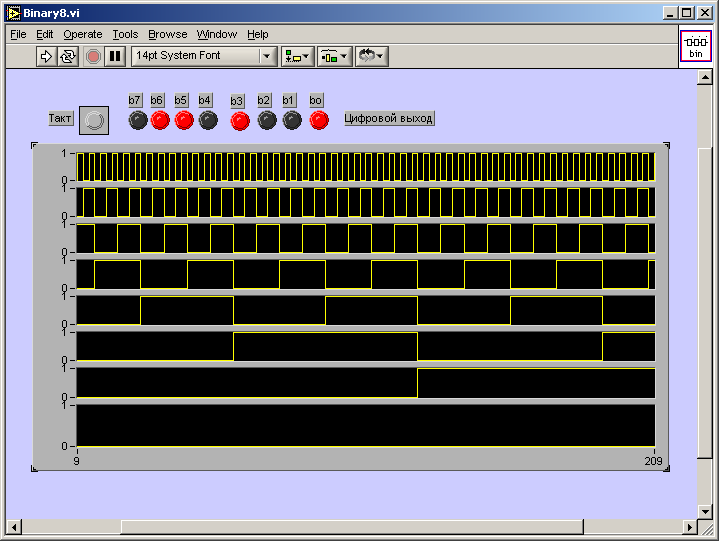

Созадайте программу Binary8.vi. Она наглядно демонстрирует двоичную счетную последовательность в виде байта на восьми светодиодных индикаторах и 8-битовую временную диаграмму. Запустите этот прибор в непрерывном режиме для наблюдения двоичных чисел от 0 до 255. Временная диаграмма показывает, что частота сигнала на каждой стадии в два раза меньше, чем на предыдущей. Выходные частоты сигналов на стадиях Qo...Q7-f/2, f/4, f/8, f/16, f/32, f/64, f/128n f/256. Здесь f - тактовая частота. Для различных операций двоичные счетчики необходимо сбрасывать в состояние 0 (все биты 0) или устанавливать в состояние 1 (все биты 1). Таблица истинности для JK-триггера, показанная выше, имеет прямые входы, обеспечивающие такую возможность (прямая логика). Синхронная (тактируемая) логика активизируется, когда входы сигналов установки в "0" и "1" имеют Высокий уровень. Низкий уровень сигнала на входе установки в "1" или "0" устанавливает выход триггера в 1 или 0 соответственно. Эти операции взаимно исключающие, следовательно, состояние (00) запрещено.

Рисунок 6-6. Моделирование 8-битовый двоичный счетчик.

ЗАДАЧА 31:

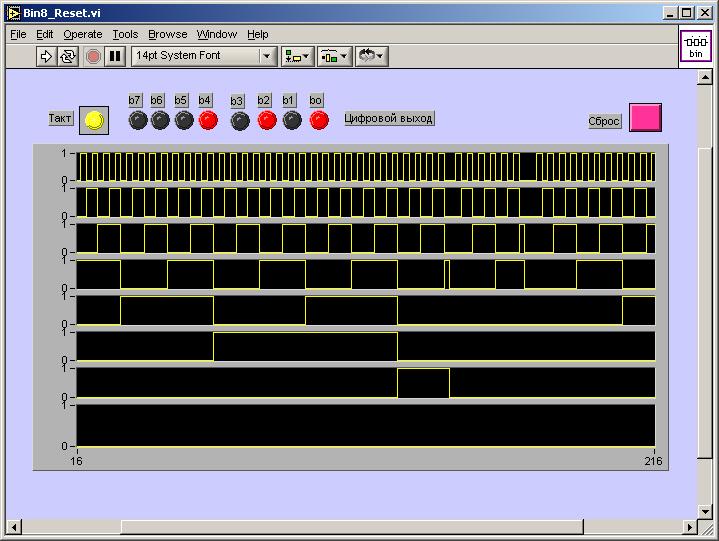

Создайте и сохраните файл виртуального прибора Bin8_Reset.vi.

Виртуальный прибор Bin8_Reset.vi обеспечивает функцию установки в исходное состояние 8-битового двоичного счетчика. Запустите эту программу в непрерывном режиме. Нажатием на кнопку Reset счетчик устанавливается в исходное состояние. Эта операция применяется для счетчиков с нечетным коэффициентом пересчета и в аналого-цифровых преобразователях.

Задание повышенной сложности (по указанию преподавателя)

Придумайте двузначный двоичный счетчик, который бы считал от 0 до 99.

Двоичные счетчики являются базовой компонентой цифровых электронных схем. Они применяются для счетчиков по модулю n различных типов, для генерации субгармоник тактирующих сигналов, а также в многоразрядных устройствах, таких как АЦП и ЦАП.

Состав библиотеки виртуальных приборов, использованных на занятии 5 (показан в порядке упоминания)

Binary 1.vi (счетчик-делитель на 2)

Binary2.vi (счетчик-делитель на 4)

Binary4.vi (счетчик-делитель на 16 с графическим индикатором)

Binary8.vi (счетчик-делитель на 256 с графическим индикатором)

Bin8_Reset.vi (8-битовый счетчик с кнопкой возврата в исходное состояние)

FlipFlop.vi (подпрограмма, применяемая во всех приборах этой главы)