- •Содержание

- •Введение

- •1 Разработка функциональной схемы системы

- •Описание принципа работы объекта

- •1.2 Функциональная схема микропроцессорной системы

- •2 Разработка аппаратной части системы

- •2.1 Краткое описание микропроцессорного комплекта

- •2.2 Организация памяти микропроцессорной системы Распределение памяти контроллера приведено на рисунке 5.

- •2.3 Расчет и выбор элементов сопряжения

- •2.3.1 Выбор терморезистора и элементов схемы сопряжения его с ацп.

- •2.3.2 Выбор ацп

- •2.3.3 Выбор индикатора и элементов сопряжения с ним

- •2.3.4 Расчет и выбор кнопок

- •2.3.5 Выбор конденсаторов

- •K73-9-10b-0,1 мкФ±10% ожо.461.087 ту

- •2.4 Описание схемы электрической принципиальной

- •3 Разработка программного обеспечения системы

- •3.1 Краткое описание системы команд микроконтроллера

- •Группа команд арифметических операций:

- •3.2 Описание общего алгоритма работы системы

- •3.3 Разработка текста программы

- •Заключение

- •Список использованной литературы

1.2 Функциональная схема микропроцессорной системы

Функциональная схема системы приведена на рисунке 2 и в графической части проекта.

В данной схеме можно выделить следующие блоки:

датчик температуры (ДТ) – изменяет значения сопротивления в зависимости от температуры;

блок согласования (БС) – служит для связи датчика температуры с микропроцессорным устройством;

блок ввода аналогового сигнала (БВА) – преобразует аналоговые значения поступающие с датчика в цифровые;

блок расчета температуры (БРТ) – служит для расчета температуры в соответствии с таблицей сопротивления датчика;

блок расчета среднесуточной температуры (БРСТ) –служит для расчета среднесуточной температуры;

блок обработки индикации (БОИ) – служит для подготовки вывода информации на индикатор;

индикатор (ИНД) – служит для визуализации информвции ;

таймер (Т) – служит для отсчетов промежутков времени;

блок обработки клавиатуры (БОК) – служит для подготовки ввода информации с клавиатуры;

клавиатура (К) – служит для ввода информации в микропроцессорную систему.

Рисунок 2 – функциональная схема микропроцессорной системы

2 Разработка аппаратной части системы

2.1 Краткое описание микропроцессорного комплекта

В данном проекте используется 8-разрядный КМОП микроконтроллер с Flash ПЗУ AT89C51.

Особенности:

- Совместимость с приборами семейства MCS-51TM

- Емкость перепрограммируемой Flash памяти: 4 Кбайт, 1000 циклов стирание/запись.

- Напряжение питания 5±20% B

- Полностью статический прибор - диапазон рабочих частот от 0 Гц до 24 МГц.

- Группы по частотам: 12 МГц, 16 МГц, 20 Мгц и 24 Мгц

- Трехуровневая блокировка памяти программ

СОЗУ емкостью 128 байтов

- 32 программируемых линий ввода/вывода

- Два 16-разрядных таймера/счетчика событий

- Шесть источников сигналов прерывания

- Программируемый последовательный канал UART

- Пассивний (idle) и стоповый (power down) режимы

- Промышленный (-40°С...85°C), коммерческий (0°C...70°C), диапазоны температур

Описание:

КМОП микроконтроллер АТ89С51, оснащенный Flash программируемым и стираемым ПЗУ , совместим по системе команд и по выводам со стандартными приборами семейства MCS-51TM. Микроконтроллер содержит 4 Кбайта Flash ПЗУ, 128 байтов ОЗУ, 32 программируемых линий ввода/вывода, два 16-разрядных таймера/счетчика событий, полнодуплексный последовательный порт (UART), пять векторных двухуровневых прерывания, встроенный генератор и схему формирования тактовой последовательности.

Существуют два варианта микроконтроллеров АТ89С51: с возможностью внутрисистемного программирования с использованием при программировании напряжения 5 В, и программирование с использованием напряжения 12 В, применяемого в большинстве программаторов.

Содержимое Flash памяти программ может быть защищено от несанкционированной записи/считывания. Имеется возможность очистки Flash памяти за одну операцию, возможность считывания встроенного кода индентификации.

Потребление в активном режиме на частоте 12 Мгц не превышает 20 мА и в пассивном режиме, при котором остановлено ЦПУ, но система прерываний, ОЗУ, таймеры/счетчики событий и последовательный порт остаются активными, потребление не превышает 5 мА. В стоповом режиме потребление не превышает 100 мкА и 20 мкА при напряжении питания 6 В и 3 В, соответственно.

Микроконтроллер АТ89С51 ориентирован на использование в качестве встроенного управляющего контроллера.

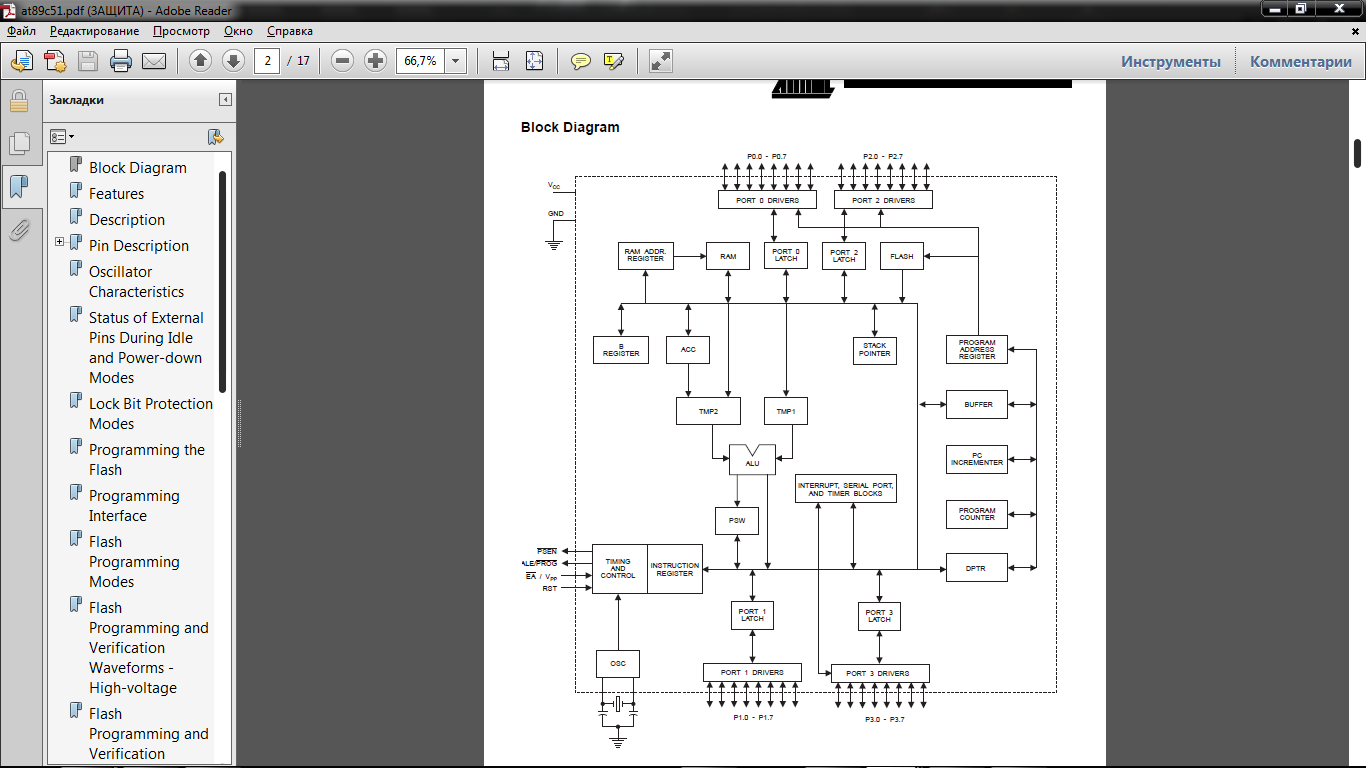

Структурная схема контроллера приведена на рисунке 3.

Рисунок 3 – структурная схема контроллера AT89C51

В данной схеме представлены следующие блоки:

PORT 0,1,2,3 – соответственно четыре 8-разрядных порта МК;

DPTR,PSW - регистры специальных функций;

PC INCREMENTER – счетчик команд;

PROGRAM ADDRESS REGISTER – регистр адреса программ;

STACK – стек, служит для временного хранения данных;

ACC – аккумулятор;

B – регистр, служащий расширителем аккумулятора;

RAM – память стираемая после выключения устройства(ОЗУ);

Flash – память программ, из которой контроллер считывает программу после включения (ПЗУ);

ALU – арифметическо-логическое устройство, осуществляет арифметические и логические операции;

INTERRUPT PORT – блол отвечающий за работу прерываний от пяти источников(входы int0, int1, таймеры-счетчики С/Т0, С/Т1 и от последовательного интерфейса).

Распишем более подробно работу некоторых блоков используемых в данной работе :

INTERRUPT PORT:

Упрощенная схема прерываний показана на рисунке 4:

Рисунок 4 – упрощенная схема прерываний.

Внешние прерывания ¬INT0 и ¬INT1 могут быть вызваны либо уровнем, либо переходом сигнала из 1 в 0 на входах МК51 в зависимости от значений управляющих бит IT0 и IT1 в регистре TCON. От внешних прерываний устанавливаются флаги IE0 и IE1 в регистре TCON, которые инициируют вызов соответствующей подпрограммы обслуживания прерывания. Сброс этих флагов выполняется аппаратурно только в том случае, если прерывание было вызвано по переходу (срезу) сигнала. Если же прерывание вызвано уровнем входного сигнала, то сбросом флага IE управляет соответствующая подпрограмма обслуживания прерывания путем воздействия на источник прерывания с целью снятия им запроса

Флаги запросов прерывания от таймеров TF0 и TF1 сбрасываются автоматически при передаче управления подпрограмме обслуживания. Флаги запросов прерывания RI и ТI устанавливаются блоком управления УАПП аппаратурно, но сбрасываться должны программой.

Прерывания могут быть вызваны или отменены программой, так как все перечисленные флаги программно-доступны и могут быть установлены/сброшены программой с тем же результатом, как если бы они были установлены/сброшены аппаратурными средствами

В блоке регистров специальных функций есть два регистра, предназначенных для управления режимом прерываний и уровнями приоритета. Возможность программной установки/сброса любого управляющего бита в этих двух регистрах делает систему прерываний МК51 исключительно гибкой.

Флаги прерываний опрашиваются в момент S5P2 каждого машинного цикла. Ранжирование прерываний по уровню приоритета выполняется в течение следующего машинного цикла. Система прерываний сформирует аппаратурно вызов (LCALL) соответствующей подпрограммы обслуживания, если она не заблокирована одним из следующих условий:

1) в данный момент обслуживается запрос прерывания равного или более высокого уровня приоритета;

2) текущий машинный цикл – не последний в цикле выполняемой команды;

3) выполняется команда RETI или любая команда, связанная с обращением к регистрам IE или IP.

Отметим, что если флаг прерывания был установлен, но по одному из перечисленных выше условий не получил обслуживания и к моменту окончания блокировки уже был сброшен, то запрос прерывания теряется и нигде не запоминается

По аппаратурно-сформированному коду LCALL система прерывания помещает в стек только содержимое счетчика команд (PC) и загружает в счетчик команд адрес вектора соответствующей подпрограммы обслуживания. По адресу вектора должна быть расположена команда безусловной передачи управления (JMP) к начальному адресу подпрограммы обслуживания прерывания. Подпрограмма обслуживания в случае необходимости должна начинаться командами записи в стек (PUSH) спора состояния программы (PSW), аккумулятора, расширителя, указателя данных и т.д. и заканчиваться командами восстановления из стека (POP). Подпрограммы обслуживания прерывания обязательно завершаются командой RETI, по которой в счетчик команд перезагружается из стека сохраненный адрес возврата в основную программу. Команда RET также возвращает управление прерванной основной программе, но при этом не снимает блокировку прерываний, что приводит к необходимости иметь программный механизм анализа окончания процедуры обслуживания данного прерывания.

Также можно рассмотреть таймеры контроллера:

Два программируемых 16-битных таймера/счетчика (T/C0 и T/C1) могут быть использованы в качестве таймеров или счетчиков внешних событий. При работе в качестве таймера содержимое T/C инкрементируется в каждом машинном цикле, т.е. через каждые 12 периодов резонатора. При работе в качестве счетчика содержимое Т/С инкрементируется под воздействием перехода из 1 в 0 внешнего входного сигнал; подаваемого на соответствующий (T0, T1) вывод МК51. Опрос значения внешнего входного сигнала выполняется в момент времени S5P2 каждого машинного цикла. Содержимое счетчика будет увеличено на 1 в том случае, если в предыдущем цикле был считан входной сигнал высокого уровня (1), а в следующем – сигнал низкого уровня (0). Новое (инкрементированное) значение счетчика будет сформировано в момент S3P1 в цикле, следующем за тем, в котором был обнаружен переход сигнала из 1 в 0. Так как на распознавание перехода требуется два машинных цикла, то максимальная частота подсчета входных сигналов равна 1/24 частоты резонатора. На длительность периода входных сигналов ограничений сверху нет. Для гарантированного прочтения входного считаемого сигнала он должен удерживать значение 1 как минимум течение одного машинного цикла МК51.

Для управления режимами работы T/C и для организации взаимодействия таймеров с системой прерывания используются два регистра специальных функций (TCON и TMOD), описание которых приводите в табл.1 и табл. 2 соответственно. Как следует из описания управляющих бит TCON, для обоих T/C режимы работы 0, 1 и 2 одинаковы. Режимы для T/C0 и T/C1 различны. Рассмотрим кратко работу T/C во всех четырех режимах.

Режим 0. Перевод любого Т/С в режим 0 делает его похожим на таймер МК48 (8-битный счетчик), на вход которого подключен 5-битный предделитель частоты на 32. Работу Т/Cв режиме 0 на примере Т/C1 иллюстрирует. В этом режиме таймерный регистр имеет разрядность 13 бит. При переходе из состояния "все единицы" в состояние "все нули" устанавливается флаг прерывания от таймераTF1. Входной синхросигнал таймера 1 разрешен (поступает на входT/C), когда управляющий битTR1 установлен в 1 и либо управляющий битGATE(блокировка) равен 0, либо на внешний вывод запроса прерывания ¬INT1 поступает уровень 1.

Отметим попутно, что установка бита GATEв 1 позволяет использовать таймер для измерения длительности импульсного сигнала, подаваемого на вход запроса прерывания.

Режим 1. Работа любого Т/С в режиме 1 такая же, как и в режиме 0, за исключением того, что таймерный регистр имеет разрядность 16 бит.

Режим 2. В режиме 2 работа организована таким образом, что переполнение (переход из состояния "все единицы" в состояние "все нули") 8-битного счетчика TL1 приводит не только к установке флагаTF1,но и автоматически перезагружает вTL1 содержимое старшего байта (TH1) таймерного регистра, которое предварительно было задано программным путем. Перезагрузка оставляет содержимое ТН1 неизменным. В режиме 2 Т/С0 и Т/С1 работают совершенно одинаково.

Режим 3. В режиме 3 Т/C0 и Т/C1 работают по- разному. Т/C1 сохраняет неизменным свое текущее содержимое. Иными словами, эффект такой же, как и при сбросе управляющего битаTRIв нуль.

Работу T/C0 в режиме 3 иллюстрирует. В режиме 3TL0 и ТН0 функционируют как два независимых 8-битных счетчика. РаботуTL0 определяют управляющие битыT/C0 (C/ ¬T,GATE,TR0), входной сигнал ¬INT0 и флаг переполненияTF0, РаботуTH0, который может выполнять только функции таймера (подсчет машинных циклов МК), определяет управляющий битTR1. При этом ТН0 использует флаг переполненияTF1.

Режим 3 используется в тех случаях применения МК51, когда требуется наличие дополнительного 8-битного таймера или счетчика событий. Можно считать, что в режиме 3 МК51 имеет в своем составе три таймера/счетчика. В том случае, если Т/С0 используется в режиме 3, Т/С1 может быть или включен, или выключен, или переведен в свой собственный режим 3, или может быть использован последовательным портом в качестве генератора частоты передачи, или, наконец, может быть использован в любом применении, не требующем прерывания.

Более подробное описание AT89C51 приведено в литературе [1].