Дз Лаврентьева / DR4

.doc

Кунин Сергей

Группа Б5-02

Домашняя работа №4 по дисциплине «Организация ЭВМ и ВС»

Задача: Спроектировать четырехразрядный двоичный синхронный реверсивный счетчик с возможностью очистки (сброса), параллельной загрузки, каскадирования и буферированным выходом на JK триггерах.

-

Таблица переходов состояния JK триггера.

|

S |

R |

C |

J |

K |

Q |

Событие |

|

0 |

0 |

X |

X |

X |

X |

Запрещено |

|

0 |

1 |

X |

X |

X |

1 |

Установка1 |

|

1 |

0 |

X |

X |

X |

0 |

Сброс 0 |

|

1 |

1 |

|

0 |

0 |

Q |

Хранение |

|

1 |

1 |

|

0 |

1 |

0 |

Запись 0 |

|

1 |

1 |

|

1 |

0 |

1 |

Запись 1 |

|

1 |

1 |

|

1 |

1 |

Q |

Счет |

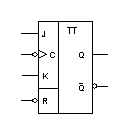

Рис 1.УГО JK - триггера

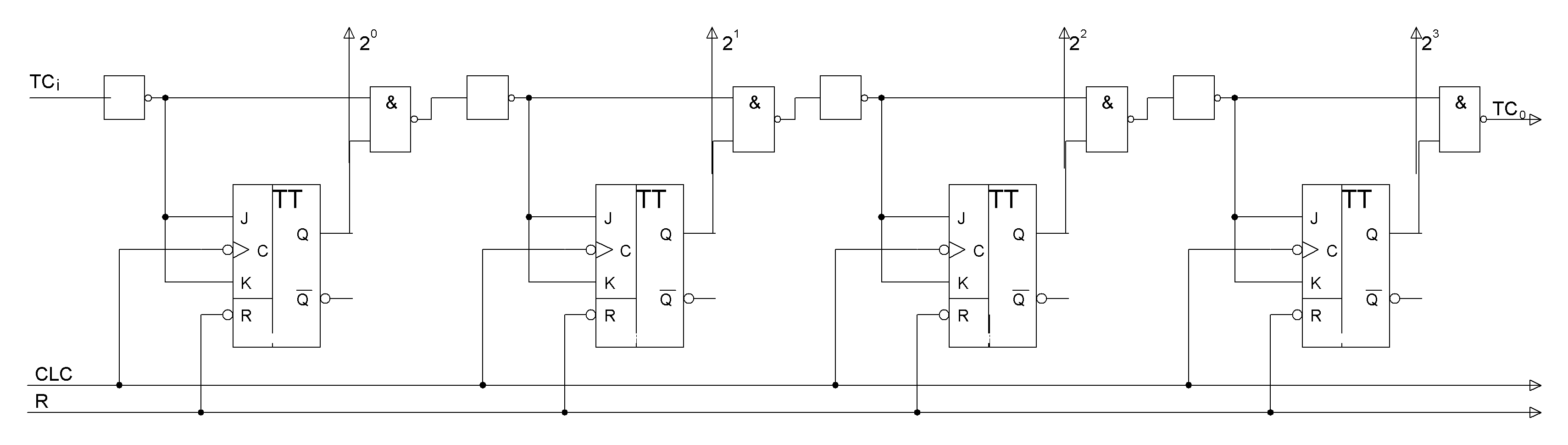

Рис. 2. Схема четырехразрядного суммирующего счетчика:

Е

сли

на элементы «2И-НЕ» подать сигнал с

выхода Q, а не с Q, то счетчик

будет работать на вычитание. Для

реализации реверсивного счетчика

следует поставить мультиплексоры на

выбор Q или Q.

сли

на элементы «2И-НЕ» подать сигнал с

выхода Q, а не с Q, то счетчик

будет работать на вычитание. Для

реализации реверсивного счетчика

следует поставить мультиплексоры на

выбор Q или Q.

П оставив

мультиплексоры на входы J и K JK-триггера,

добавим тем самым возможность параллельной

загрузки двоичного вектора D (Di

- i-й разряд вектора

D).

оставив

мультиплексоры на входы J и K JK-триггера,

добавим тем самым возможность параллельной

загрузки двоичного вектора D (Di

- i-й разряд вектора

D).

Возможность очистки (сброса) реализована введением линии Reset.

Д ля

буферирования выхода следует пропустить

сигнал с Q через буферный шинный

формирователь (элемент 1 на схеме 2).

ля

буферирования выхода следует пропустить

сигнал с Q через буферный шинный

формирователь (элемент 1 на схеме 2).

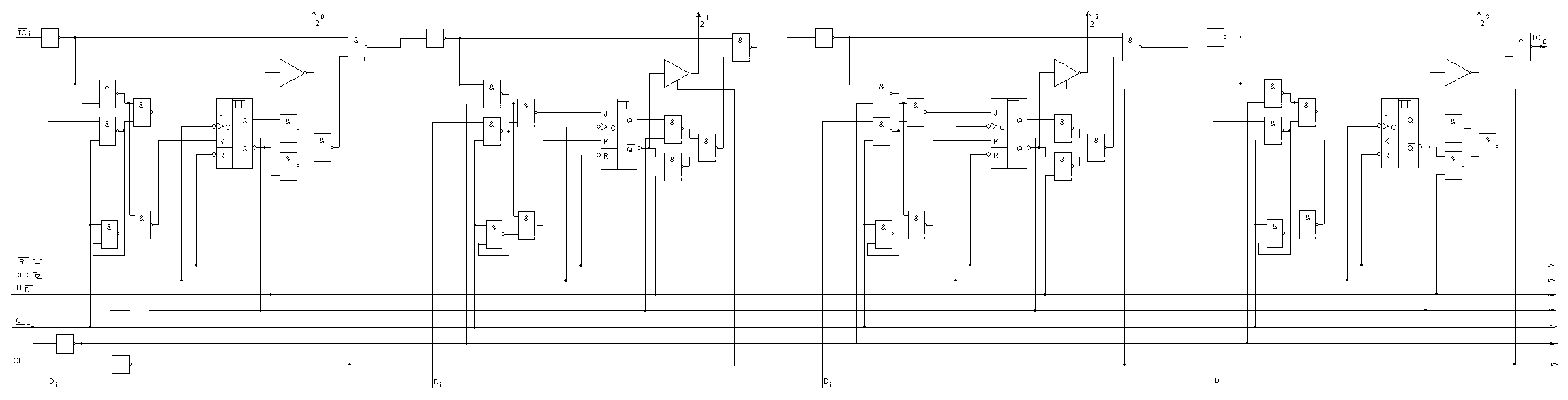

Р ис.3

Схема одноразрядного двоичного счётчика

с возможностью очистки(сброса),

каскадирования, суммирования и вычитания

(реализовано установкой мультиплексора

для выбора выходов Q и Q

) и с возможностью параллельной загрузки

(реализована с помощью мультиплексоров

на входах J и K)

и буферированным выходом.

ис.3

Схема одноразрядного двоичного счётчика

с возможностью очистки(сброса),

каскадирования, суммирования и вычитания

(реализовано установкой мультиплексора

для выбора выходов Q и Q

) и с возможностью параллельной загрузки

(реализована с помощью мультиплексоров

на входах J и K)

и буферированным выходом.

На схеме, изображённой на рисунке 4, реализована возможность каскадирования.

Рис. 4 Схема четырехразрядного двоичного синхронного реверсивного счетчика с возможностью очистки (сброса), параллельной загрузки, каскадирования и буферированным выходом на JK триггерах: