- •Изучение организации памяти, интерфейса расширения и особых режимов работы однокристального микроконтроллера кр1816ве51 (мк51).

- •Особые режимы работы мк51 Режим загрузки и верификации прикладных программ

- •Работа мк51 в пошаговом режиме

- •Сброс, режим холостого хода и режим пониженного энергопотребления

Заботин Е. Л., ЭМ-31

Лабораторная работа №14

Изучение организации памяти, интерфейса расширения и особых режимов работы однокристального микроконтроллера кр1816ве51 (мк51).

Цель работы: Изучить структуру и возможности организации памяти, интерфейса расширения и особых режимов работы однокристального микроконтроллера КР1816ВЕ51 (МК51).

Краткие сведения из теории

Организация памяти ВЕ51. Пространство внутренней памяти DSEG имеет общий объем 256 байт. Однако организация ВЕ51 предусматривает реализацию только первой его половины (128 байт). В МК 8052 DSEG используется в полном объеме.

Подобно архитектуре ВЕ48 все банки рабочих регистров, а также системный стек в МК ВЕ51 располагаются во внутренней памяти данных и могут рассматриваться как обычные ячейки памяти. Существуют два способа адресации памяти данных МК: прямой (direct) и косвенный (@Ri, i = 0—1) через регистры R0, R1 выбранного в данный момент одного из банков RB0—RB3. При прямой адресации доступна только младшая половина адресного пространства внутренней памяти данных (128 байт), при косвенной обеспечивается доступ к любой ее ячейке (256 байт). Введение отсутствующей в ВЕ48 прямой адресации значительно расширило возможности обработки данных МК, в частности появились средства прямого доступа в соседние регистровые банки и стек системы, интерпретируемые как обычные ячейки памяти.

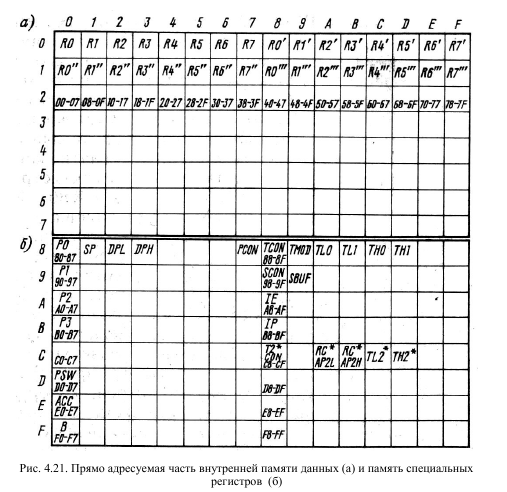

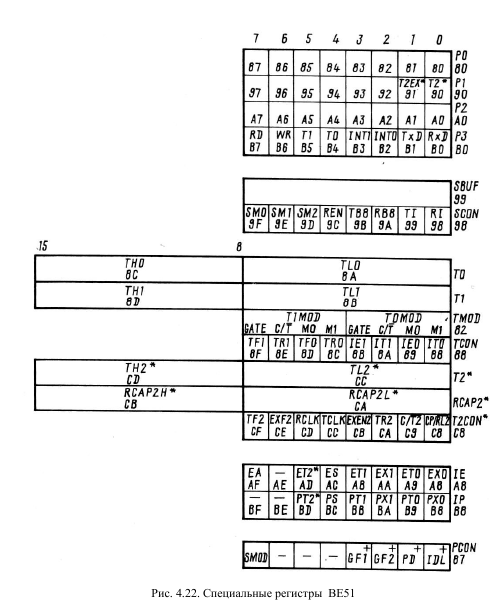

Микроконтроллер ВЕ51 имеет мощную и развитую подсистему ВВ и средства поддержки режима реального времени. Для их управления в МК предусмотрен ряд регистров, которые размещаются во второй половине прямо адресуемого пространства (рис. 4.21), образующей пространство специальных регистров (128 байт). Сюда же включены порты и основные регистры ЦП. Элементы, присутствующие только в модели 8052, отмечены знаком «*», как и на рис. 4.22 - 4.24.

Центральный процессор ВЕ51 содержит специальную логику, предназначенную для выполнения нескольких однобитовых операций, булев или одноразрядный процессор для вычисления булевых выражений. В основу булева процессора положен стандартный аккумуляторный принцип организации. В данном случае роль аккумулятора выполняет флажок переноса CY.

Для хранения булевых данных в архитектуре ВЕ51 предусмотрено специальное одноразрядное линейно упорядоченное пространство BSEG объемом 256 байт, которое физически совмещено с байтовым пространством данных DSEG. При этом одна часть пространства BSEG попадает на обычные ячейки памяти DSEG и может рассматриваться как область общего назначения. Обычно она используется для хранения булевых переменных. Другая часть пространства BSEG попадает на ячейки памяти, совмещенные с регистрами МК, что обеспечивает независимый доступ к их отдельным разрядам. В булевом пространстве определена только прямая адресация bit.

На рис. 4.21 в байтах пространства с прямой адресацией, которые размещены в булевом пространстве, указаны диапазоны адресов BSEG, относящихся к их разрядам. Например, старший разряд аккумулятора А, отождествленного с ячейкой пространства памяти с прямой адресацией под адресом 0E0H, имеет адрес пространства BSEG, равный 0Е7Н. Двойная, а в ряде случаев тройная интерпретация отдельных данных дает возможность программисту выбирать тип доступа, наиболее подходящий для конкретного прикладного случая программирования. Все это позволяет повысить эффективность программного кода, его длину и скорость исполнения.

Пространство внешней памяти XSEG имеет объем 64К байт и реализуется внешними по отношению к МК средствами. Существует единственная команда, поддерживающая связь с данным пространством:

MOVX A,@Ri ;A — XSEG (P2:Ri), ;i = 0 - 1

MOVX A,@DPTR ;A — XSEG (DPTR)

MOVX @Ri, A ;XSEG (P2:Ri) — A, ;i = 0 - 1

MOVX @DPTR, A ;XSEG (DPTR) — A

В команде используются два типа адресации: косвенная регистровая по DPTR и страничная с номером страницы в Р2 и смещением в R0, R1. Это дает право рассматривать организацию внешней памяти ВЕ51 как линейную область или как область со страничной структурой.

Память программ CSEG адресуется 16-разрядным счетчиком PC и, следовательно, может иметь объем до 64К байт. Часть этой памяти (4К/8К байт с младшими адресами) может быть расположена на кристалле в виде программируемого маской ПЗУ или репрограммируемого электрически УСППЗУ. Она образует внутреннюю память программ. Оставшаяся часть, реализуемая внешними средствами вне кристалла, называется внешней памятью программ. С точки зрения программиста как внутренняя, так и внешняя память представляет собой единое пространство CSEG с равными правами доступа.

Среди особых точек пространства CSEG следует отметить

|

RESET |

0000H |

Стартовый адрес при сбросе системы |

|

ЕХТ10 |

0003Н |

Внешнее прерывание 0 |

|

TIMER0 |

000BH |

Прерывание таймера/счетчика 0 |

|

ЕХТ11 |

0013Н |

Внешнее прерывание 1 |

|

TIMER1 |

001BH |

Прерывание таймера/счетчика 1 |

|

SINT |

0023H |

Прерывание последовательного порта |

|

TIMER2 |

002ВН |

Прерывание таймера/счетчика 2 (только для 8052) |

Пространство CSEG - однородное линейное пространство, в котором определены два основных способа передачи управления: абсолютный addr16 и относительный с помощью 8-разрядного смещения rel со знаком. Однако для некоторых команд оно представляет набор 2К-байтовых страниц:

ACALL addr11 ; + (SP) — PC, PC0 - 10 — addr11

AJMP addr11 ; PC0 - 10 — addr11

Кроме того, предусмотрен переход по смещению относительно базы DPTR: JMP @A + DPTR ; PC — DPTR + A

Эти команды введены для поддержки совместимости с архитектурой ВЕ48. Специальная команда пересылки

MOVC A, @A + DPTR ; A — CSEG(A + DPTR) MOVC A, @A + PC ; A — CSEG(A + PC)

позволяет использовать содержимое программной памяти в качестве констант, доступных для чтения.

В МК ВЕ51 имеется возможность совмещения внешней части CSEG с пространством XSEG. Такое совмещение поможет распространить на область CSEG операции и способы доступа к XSEG, в частности станет осуществимой операция записи, что может быть использовано при загрузке программ из внешней памяти.

Интерфейс расширения. Как и в ВЕ48, внутренние ресурсы ВЕ51/8052 могут быть расширены внешними средствами. При этом память программ CSEG достигает 64К байт, а память данных увеличивается за счет ввода в действие внешней памяти XSEG, максимальная емкость которой тоже 64К байт. Внешняя часть CSEG и область XSEG могут быть объединены в одно физическое пространство. Расширение области ВВ выполняется за счет части пространства XSEG (совмещенный ВВ).

Для связи со средствами расширения МК имеет встроенную системную магистраль, которая физически частично совмещена с портами Р0, Р1 и РЗ. В состав магистрали входят двунаправленная шина AD (порт Р0), шина старшей части адреса А (порт Р2), стробы фиксации адреса ALE, чтения памяти программ PSEN, записи WP (линия Р3.6) и чтения RD (линия Р3.7) внешней памяти данных XSEG.

По срезу ALE передаваемая через порт Р0 младшая часть адреса фиксируется во внешнем регистре (см. рис. 4.25). Старшая часть принимается из порта Р2. Стробы PSEN (IOL = 3,2 мА), RD и WR определяют тип доступа. При чтении CSEG (операция PSEN) данные считываются по фронту строба PSEN (фаза S1P1 и S4P1) (рис. 4.26, а), при чтении XSEG (операция RD) - по фазе S3P1 (рис. 4.26, б), при записи в XSEG (операция WR) данные действительны на всем стробе (рис. 4.26, в).

Цикл внешнего обращения к CSEG инициируется всякий раз при выходе адреса за пределы внутреннего ПЗУ, а также при ЕА = 0. Возможность отключения внутреннего ПЗУ используется в системах эмуляции МК и отладки МС на его основе. Цикл обращения к внешней памяти инициируется по команде MOVX.

В операциях обращения к внешней памяти участвуют порты Р0 (совмещенная магистраль AD), P2 (магистраль старшего адреса), а также линии Р3.6 (строб WR) и Р3.7 (строб RD) порта РЗ. При работе порта Р0 в качестве линии AD содержимое связанного с ним выходного регистра теряется и принимает значение 0FFH. Содержимое выходного регистра порта Р2 при работе в режиме адресной шины сохраняется и поступает на выводы порта в тех машинных циклах и полуциклах, когда нет обращения к внешней памяти.

Физическое совмещение пространств CSEG, И XSEG выполняется объединением стробов PSEN и RD в один строб чтения.