Мал. 1.5 Умовне позначення (а) і алгоритм роботи(б) тригера

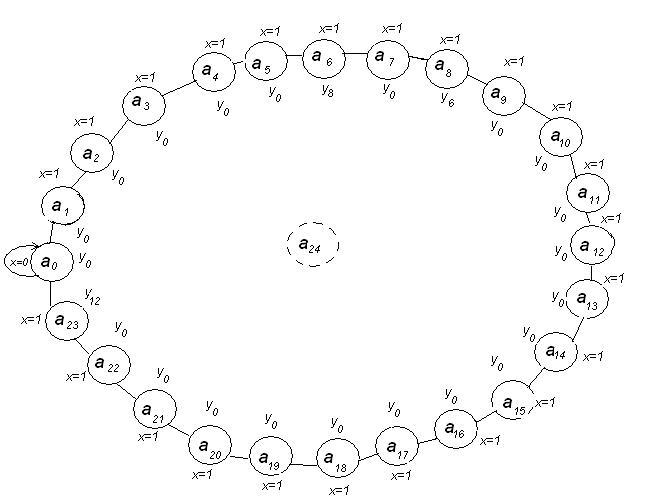

Малюнок 1.6 Граф для ЦА1

то логічні функції q1, q2, q3, q4, q5 , виявляються неповністю визначеними , тому в їх таблицях істинності з'являються «байдужі» змінні, позначені символом Х, які в міру необхідності можуть приймати значення 1 або 0. Звернете також увагу на те, що в таблиці 1.8 складовою частиною входять не тільки q1, q2, q3, q4, q5 , а також вихідних сигналів V6, V8, V12 і W : все ці функції залежать від змінних Q1(t) , Q2(t), Q3(t), Q4(t), Q5(t).

Значення уl вихідних сигналів у(t) змінюються за рахунок видачі імпульсів на активні виходи V6,V8,V12. Оскільки логічні функції V8,V6,V12 і W тільки один раз за цикл приймають одиничне значення , то при синтезі КП2 аналітичні вирази для них виходять відразу, минувши етап мінімізації (формули 1.2.2-1.2.4).

Таблиця 1.8 Повна таблиця функціонування ЦА1

|

Вхідний

сигнал

|

Попередній

стан тригерів T5,T4, |

Наступний

стан тригерів T5,T4, |

Сигнали управління тригерами

|

Сигнали на активних виходах |

||||||||||||||

|

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

Q5 (t+1) |

Q4 (t+1) |

Q3 (t+1) |

Q2 (t+1) |

Q1 (t+1) |

q5 |

q4 |

q3 |

q2 |

q1 |

V3(t) |

V5(t) |

V9 (t)=W |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

0 |

0 |

0 |

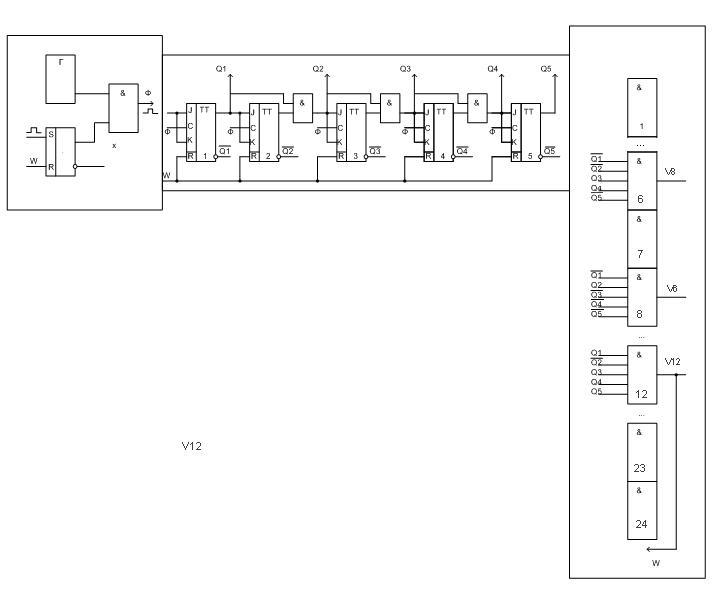

В цьому випадку КП1 і пам'ять ЦА, що синтезується, перетворюються на двійковий лічильник, що підсумовує, з паралельним перенесенням і коефіцієнтом перерахунку :

Ксч= 23 КП2 - в дешифратор станів. (1.2.6)

Зокрема, на малюнку 1.7 ЛЕ D1.1 такого ДШ формує імпульс на виході V3 при проходженні ЦА1 через стан а5= 00101(5-й такт), ЛЕ D1.2 - на виході V5 при стані a3 = 00011 (3-й такт), а ЛЕ D1.3 - на виходах V9 і W при стані a17= 10001 (17-й такт). Раціональне схемне рішення для лічильника з паралельним перенесенням виходить при використанні JК-тригерів з вбудованими схемами збігу по входах J і К.

Малюнок 1.7 Схемна реалізація комбінаційного пристрою