- •Міністерство Освіти і Науки України

- •Анотація

- •Теоретичне підґрунтя

- •Етапи проектування цифрових пристроїв на базі пліс Xilinx

- •Контрольні запитання

- •Вимоги до змісту та оформлення пояснювальної записки

- •Література

- •Завдання

- •2. Розробка процесора Побудова граф-алгоритму шпф з основою 2

- •Алгоритми сумування та множення комплексних чисел

- •Висновки

- •Проектування процесора швидкого перетворення Фур’є на програмованих логічних інтегральних схемах Методичні вказівки

2. Розробка процесора Побудова граф-алгоритму шпф з основою 2

Якщо число N є ступенем 2, то його можна записати як (N/2) * 2; аналогічно N/2 = (M/4) * 2 і т.д. В результаті елементи початкового одновимірного масиву можна розподілити таким чином, щоб елементарними операціями були двохточкові ШПФ. Для побудови графу N-точкового ШПФ з основою 2 потрібно визначити кількість ярусів (Nяр) графу та кількості метеликів (Nм) на кожному ярусі таким чином:

Nяр = Log2N, для N=16, Log216 = 4;

Nм = N/2 = 16/2= 8.

Граф-алгоритм для 16-ти точкового ШПФ за основою 2 показаний на рис. 3.

Рис.3.Граф алгоритм 16-точкове ШПФ з основою 2тапрорідженнямзачастотою

На рис. 3 кільцям відповідають двохточкові ШПФ, стрілками зображено процедуру множення на повертаючі множники. Елементи пам'яті зображено точками та пронумеровано зверху вниз.

Метелик ШПФ показаний на рис. 4, де

Рис. 4. Двохточкове ШПФ (Метелик)

X, Y - результати базової операції; А, B - вхідні відліки; WN – повертаючих множники.

Обчислення повертаючих множників WN

Для виконання кожної базової операції на вхід метелика необхідно подати повертаючий множник (коефіцієнт) Wp, де W=e-2jπ/N при прямому ШПФ і W=e2jπ/N при зворотному ШПФ. Для алгоритму ШПФ з прорідженням за часом значення р пов'язані з номерами відліків п, беруть участь у виконанні базової операції на j-й ітерації, таким співвідношенням:

(10)

(10)

де j=1 ..., r-1 - номер повертаючих коефіцієнтів, що бере участь в базовій операції; ki - розряди r-ого кода номерів операндів.

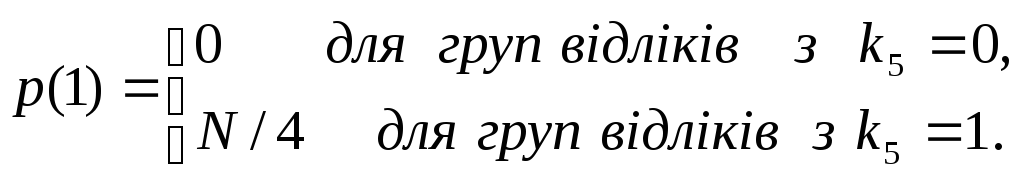

Наприклад, для N=64 і r=2 на 1-й ітерації значення р(1) для всіх груп відліків рівне 0, на 2-й ітерації р(1)=k524= =k5N/4, т. д.

На третій ітерації

і т д.

Використовуючи вираз (10) здійснюємо обчислення повертаючих множників для 16-ти точкового ШПФ за основою 2 з прорідженням по частоті. Відмінністю буде зміна порядку слідування коефіцієнтів на різних ітераціях, тобто на першій ітерації:

Н а

другій ітерації:

а

другій ітерації:

Н

а

третій ітерації:

а

третій ітерації:

На четвертій ітерації: p=0, для всіх груп відліків

Побудова модифікованого граф ШПФ

При апаратній реалізації графу ШПФ виникають незручності через неспівпадіння адрес комірок пам'яті з яких потрібно вичитувати елементи на кожному ярусі. Тому від графу зображеного на рис.3 доцільно перейти до графу зображеного на рис.5.

З рис. 5 видно, що для кожної базової операції на будь-якому ярусі дані беруться і записуються за тими самими адресами що і на попередньому ярусі (з заміщенням).

М етелики

та комірки пам’яті пронумеровані у

відповідності до графу на рис. 3. Порядок

слідування повертаючих множників

змінюється так, як зображено на рис. 5.

етелики

та комірки пам’яті пронумеровані у

відповідності до графу на рис. 3. Порядок

слідування повертаючих множників

змінюється так, як зображено на рис. 5.

Рис.5. Модифікований граф 16-ти точкового ШПФ за основою 2 з прорідженням за частотою.

Біт інверсний порядок видачі даних

Ще однією особливістю алгоритму з прорідженням за частотою є те, що прямий порядок слідування даних на вході графу змінюється двійково-інверсним на виході. Тому для видачі даних в прямому порядку потрібно здійснити двійково-інверсну перестановку за правилом описаним в табл.1.

Таблиця 1 Двійково-інверсна перестановка даних

-

номер

Двійкове представле-ння

Двійкова інверсія

Двійково-інверсний номер

0

0000

0000

0

1

0001

1000

8

2

0010

0100

4

3

0011

1100

12

4

0100

0010

2

5

0101

1010

10

6

0110

0110

6

7

0111

1110

14

8

1000

0001

1

9

1001

1001

9

10

1010

0101

5

11

1011

1101

13

12

1100

0011

3

13

1101

1011

11

14

1110

0111

7

15

1111

1111

15

Для реалізації пристрою обчислення ШПФ використовується одна із модифікацій графу алгоритму (рис. 5), а саме його проекція на вертикальну площину. В результаті отримуємо схему ітераційного пристрою, зображену на рис. 6. Кожній ітерації роботи пристрою відповідає один ярус потокового графу ШПФ.

Проекція потокового графу ШПФ на вертикальну площину

Спрощена проекція потокового графу ШПФ на вертикальну площину показана на рис. 6.

Рис. 6. Спрощена проекція графу на вертикальну площину.

На рис.6 використані такі позначення:

- Memory array – масив елементів пам'яті для зберігання проміжних результатів обробки;

- MUX–вхідні мультиплексори для вибору вхідних даних на першому циклі, та проміжних даних не решті циклах роботи пристрою;

- F1,F2,…,F8–вузли обробки (двохточкові ШПФ)

На рис. 6 не наведені повертаючі множники та виходи пристрою (ілюструється лише потік даних при обробці).

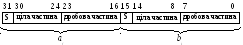

Формат вхідних та вихідних даних

Вхідні та вихідні дані є комплексними числами виду А=ar+jbi, де аr – дійсна частина, bi – уявна частина, j- уявна одиниця. Для їх кодування використовуються 32 розряди, причому 16 старших розрядів для кодування дійсної частини, 16 молодших для кодування уявної частини.

Рис. 7 Формат вхідних та вихідних даних

Дійсна і уявна частина є знаковими числами з фіксованою комою. Розряди 31 та 15 використовуються для кодування знаків, 30-24 та 14-8 для кодування цілих частин, 23-16 та 7-0 для кодування дробових частин дійсної та уявної складових числа відповідно до рис. 7.

Інтерфейс пристрою

П ристрій

має 16 паралельних вхідних портів для

прийому даних та два вхідні порти для

керуючих сигналів – це сигналиRST

(Reset –

початковий скид) та CLK(Clock

– синхронізація). Результати обробки

вхідних даних видаються по 16-х паралельних

вихідних портах. Всі порти, крім RSTiCLKє

32-х розрядні.

ристрій

має 16 паралельних вхідних портів для

прийому даних та два вхідні порти для

керуючих сигналів – це сигналиRST

(Reset –

початковий скид) та CLK(Clock

– синхронізація). Результати обробки

вхідних даних видаються по 16-х паралельних

вихідних портах. Всі порти, крім RSTiCLKє

32-х розрядні.

Розробка структурної схеми процесора

Структура процесора наведена на рис. 8. Дані надходять по 16-ти паралельних портах і проходячи через мультиплексори записуються у відповідні регістри. Мультиплексорами управляє керуючий автомат (Control Unit) по лінії SEL. При SEL = 0, в регістри записуються вхідні дані, при SEL = 1 – проміжні дані. Далі дані з регістрів поступають на входи двохточкових ШПФ та на наступному циклі знову записуються до відповідних регістрів. На останньому циклі, керуючий автомат генерує сигнал oen, за яким дані записуються в регістри та поступають на вихідні порти у біт-інверсному порядку (табл.1).

В ПЗП (ROM) зберігаються повертаючі множники, що є константами і подаються на двохточкові ШПФ через комутуючу мережу. Роботою комутуючої мережі (Comunication Network) управляє керуючий пристрій по лініях DC[3:0].

Далі детальніше розглянемо кожний з основних вузлів, на базі яких побудована структура процесора.

Двохточкові ШПФ (fft0 – fft7)

Вузол для обчислення двохточкового ШПФ наведений на рис. 9. На входи пристрою поступають два 32-х розрядних числа А і В та два 16-ти розрядних числа Wr i Wi. На виході отримуємо два 32-х розрядних числа X=A+B i Y=(A-B)WN.