43_Ho3 / 5-ЛОГИЧЕСКИЕ УСТРОЙСТВА ЭВМ

.DOC

.

2.8. СЧЕТЧИКИ

Счетчиком называется узел ЭВМ, предназначенный для подсчета числа входных сигналов. Счетчики используются в ЭВМ для образования последовательностей адресов команд, для подсчета числа циклов выполнения операций и т. п. Счетчики принято подразделять на суммирующие, вычитающие и реверсивные.

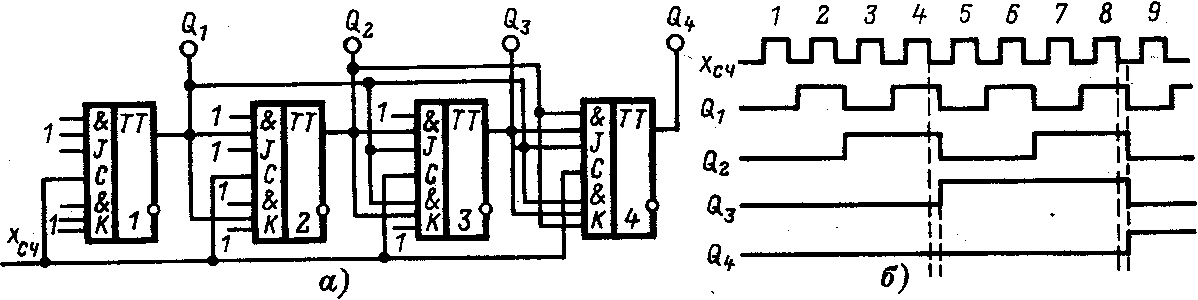

На рис. 2.20 показаны схема несинхронизируемого четырехразрядного двоичного суммирующего счетчика с последовательным переносом и временная диаграмма его работы. Таблица 2.5 показывает состояния, в которых находятся триггеры счетчика при воздействии серии входных сигналов хсч.

Рис. 2.20. Несинхронизируемый двоичный счетчик с последовательным переносом:

а — функциональная схема; 6 — временная диаграмма

Здесь на входы J и К JK-триггеров подаются сигналы 1. Выход каждого предыдущего триггера Q n-1 соединен с входом синхронизации Сn последующего триггера. Каждый JK-триггер в счетчике выполняет функцию несинхронизируемого триггера со счетным входом. По спаду единичного выходного сигнала изменяется состояние триггера младшего разряда счетчика на противоположное (т.е. реализуется сложение по модулю 2 в этом разряде). В последующих разрядах аналогичное действие производит сигнал переноса

Таблица 2.5. Таблица состояний двоичного счетчика

|

Хсч |

Q4 |

Q3 |

Q2 |

Q1 |

Хсч |

Q4 |

Q3 |

Q2 |

Q1 |

|

о |

0 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

9 |

1 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

10 |

1 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

11 |

1 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

12 |

1 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

13 |

1 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

14 |

1 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

15 |

1 |

1 |

1 |

1 |

Обычно счетчик имеет цепь установки в нулевое состояние (сброс триггеров в 0). Однако начальное состояние счетчика необязательно нулевое. Начальное состояние может устанавливаться передачей в счетчик кода некоторого числа, и с него уже будет начинаться операция счета единиц. Такой режим работы счетчика необходим, например, при образовании последовательности адресов команд при заданном исходном адресе. С ростом разрядности счетчика понижается предельная частота его работы. Это объясняется тем, что с ростом разрядности счетчика п будет возрастать задержка поступления сигнала на вход С некоторого j-го разряда относительно времени поступления входного сигнала Хсч на вход С младшего разряда счетчика. Из временной диаграммы видно, что такая задержка может привести к искажению информации в счетчике (моменты времени 4 и 8). Для повышения быстродействия счетчики выполняют с параллельным переносом,

На рис. 2.21 изображена функциональная схема счетчика с параллельным переносом. Отличительной особенностью данной схемы является то, что выходы всех предшествующих разрядов подаются на входы J и К j-го триггера. Длительность переходного процесса в таком счетчике равна длительности переключения одного разряда. Из схемы видно, что с возрастанием порядкового номера триггера увеличивается число входов в элементах И JК-триггеров. А так как число входов J и К и нагрузочная способность выходов триггеров ограничены, то и разрядность счетчика с параллельным переносом невелика и равна обычно четырем. Поэтому при числе разрядов счетчика, большем максимального числа входов J и К, счетчик разбивают на группы и внутри каждой группы строят цепи параллельного переноса

.

Рис. 2.21. Синхронизируемый двоичный счетчик с параллельным переносом:

а—функциональная схема; б—временная диаграмма

Такой подход удобен и потому, что счетчики реализуют в виде интегральной микросхемы в отдельном корпусе. В этом случае при последовательном переносе просто осуществляется увеличение разрядности счетчика.

Вычитающие счетчики и реверсивные (настраиваемые на суммирование или вычитание) строятся аналогичным образом.

2.9. СУММАТОРЫ

Обычно сумматор представляет собой комбинацию одноразрядных суммирующих схем. При сложении двух чисел в каждом разряде производится сложение трех цифр: цифры данного разряда первого слагаемого, цифры данного разряда второго слагаемого и цифры (1 или 0) переноса из соседнего младшего разряда. В результате сложения для каждого разряда получаются цифра суммы для этого разряда и цифра (1 или 0) переноса в следующий старший разряд.

В табл. 2.6 приведены варианты, возникающие при сложении двух двоичных чисел.

Таблица 2.6.

|

Цифры переноса из предыдущего разряда Рi |

Первое слагаемое ai |

Второе слагаемое bi |

Сумма Si |

Цифра переноса в старший разряд P i+1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

По табл. 2.6 можно составить булевы функции для описания одноразрядного сумматора — устройства, вырабатывающего на выходе сигналы суммы и переноса при поступлении на входы двух цифр слагаемых и цифры переноса из предыдущего, младшего разряда:

Si

=

![]() ;

(2.11)

;

(2.11)

Pi+1

=

![]() ,

(2.12)

,

(2.12)

где Р — цифра переноса из предыдущего (младшего разряда);

а, b — цифры слагаемых в данном разряде; Si — сумма;

Рi +1 — цифра переноса в старший разряд.

Выражение для цифры переноса в следующий разряд может быть приведено к более простому виду:

P i+1=aibi v aiPi v biPi. (2.13)

Преобразуя с помощью правил булевой алгебры выражения для цифры суммы и цифры переноса, можно получать различные соотношения, которым будут соответствовать варианты построения схем полных сумматоров.

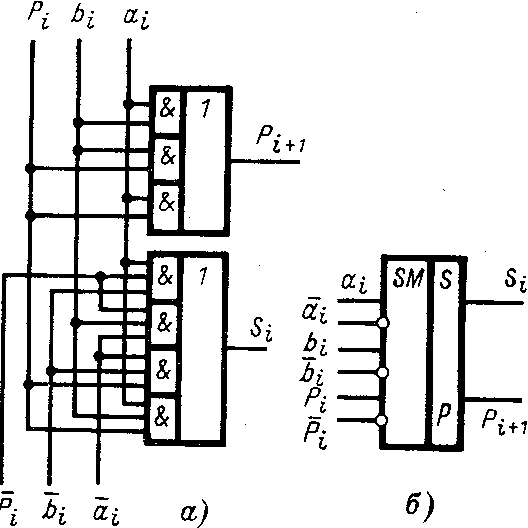

Рис. 2.22. Комбинационный одноразрядный сумматор:

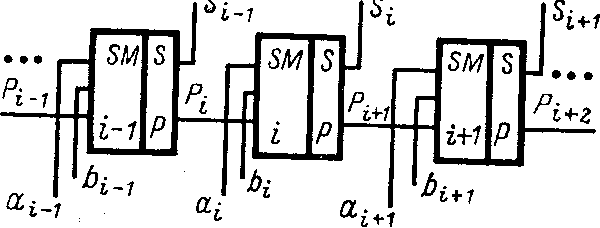

Рис. 2.23. Параллельный сумматор с последовательным переносом

а — функциональная схема; 6 — условное обозначение

Функциональная схема одноразрядного комбинационного сумматора, реализующего соотношения (2.11) и (2.13), показана на рис. 2.22.

Параллельный (многоразрядный) сумматор может быть составлен из одноразрядных сумматоров, число которых равно числу разрядов слагаемых, путем соединения выхода, на котором формируется сигнал переноса данного разряда, с входом для сигнала переноса соседнего старшего разряда (рис. 2.23).

После того как выработан результат сложения на выходах комбинационных схем формирования суммы, он обычно запоминается в отдельном триггерном регистре.

Быстродействие одноразрядного комбинационного сумматора характеризуется временем установления выходных сигналов суммы и переноса после установления сигналов на входах сумматора. Наиболее важным является время распространения сигнала переноса в одноразрядном сумматоре, так как при образовании многоразрядного сумматора из одноразрядных схем сигнал переноса может распространяться от разряда к разряду. Это время определяется временами задержек в логических элементах и количеством последовательно включенных элементов в схеме распространения сигнала переноса.

По характеру распространения переноса различают следующие виды сумматоров: с поразрядным последовательным переносом, с параллельным (одновременным) переносом, с групповым переносом.

Сумматоры с поразрядным последовательным переносом. В сумматорах этого типа (рис. 2.23) перенос распространяется последовательно от разряда к разряду по мере образования цифры суммы в каждом отдельном разряде. При наиболее неблагоприятных условиях для распространения переноса, например при сложении чисел 11...11 и 00...001, произойдет «пробег» 1 переноса через весь сумматор от самого младшего разряда к самому старшему. Поэтому в худшем случае время распространения переноса

Tпер = 1n, (2.14)

где 1 — время распространения переноса в одном разряде; п — число разрядов сумматора. Данный тип сумматора наиболее прост с точки зрения схемы целей распространения переноса, но имеет сравнительно низкое быстродействие.

Сумматоры с параллельным переносом. Можно построить сумматор, в котором сложение выполняется как поразрядная операция и на распространение переноса не требуется дополнительного времени.

Затраты оборудования на построение сумматора такого типа, особенно при большом числе разрядов, настолько велики, что в чистом виде он практически не находит применения. Принцип параллельного формирования переноса используется в сумматорах с групповым переносом.

Сумматоры с групповым переносом. Сумматор разбивается на несколько групп примерно равной длины. Сигнал переноса, поступающий на вход младшего разряда группы, при наличии условий распространения переноса во всех разрядах данной группы передается на вход младшего разряда соседней, более старшей группы в обход данной группы.

Схема формирования сигнала переноса в младшем разряде каждой группы дополняется для этой цели схемой И, реализующей булеву функцию

Р уск =Рicici+1 …ci+k-1, (2.15)

где Руск — сигнал ускорения переноса;

Рi

— сигнал переноса

в младший разряд группы, содержащей

k

разрядов,

cici+1

…ci+k-1,

- условия

распространения переноса в разрядах

группы (сi

=

![]() ).

).

В таком сумматоре максимальная задержка распространения переноса определяется задержкой его в младшей, старшей группах и в цепях обхода остальных групп.

Максимальная задержка сигнала переноса может быть уменьшена, если при разбиении сумматора на группы использовать параллельное (одновременное) формирование переноса внутри групп.

Современные системы элементов содержат микросхемы сумматоров и микросхемы формирования сигналов группового переноса.