- •1.1 Основні визначення

- •1.2 Принципи побудови та функціонування обчислювальних систем

- •1.2.1 Архітектура обчислювальних систем

- •1.3 Принципи побудови та функціонування мпс

- •1.4 Функціонування обчислювального пристрою

- •2.1 Подання даних в обчислювальних системах

- •2.2 Подання даних у кодах

- •2.3 Порозрядні операції над даними

- •3 Цифрові автомати

- •4 Типові пристрої обчислювальних систем (Для самостійного вивчення)

- •4.1 Суматори

- •4.2 Цифрові компаратори

- •4.3 Арифметично-логічний пристрій

- •4.4 Програмовані логічні інтегральні схеми (пліс)

- •5 Принципи побудови запам’ятовувальних пристроїв мпс з заданою організацією

- •5.1 Запам’ятовувальні пристрої мпс та їх класифікація

- •5.2 Постійні запам’ятовувальні пристрої – флеш-пам’ять

- •5.3 Оперативні запам’ятовувальні пристрої

- •5.4 Побудова блока запам’ятовувального пристрою мпс

- •6 Інтерфейс

- •6.1 Організація інтерфейсів

- •6.2 Асинхронний послідовний адаптер rs-232-c

- •7 Мікропроцесори

- •7.1 Архітектура мікропроцесорів

- •7.2.1 Історична довідка про розвиток мікропроцесорів фірми Intel (Для самостійного вивчення)

- •Програмна модель мп к580вм80а

- •7.2.2 Організація 16-розрядних мікропроцесорів

- •7.2.3 Програмна модель мп і8086

- •7.2.4 Режим переривань мп і8086

- •7.2.5 Організація 32-розрядних мікропроцесорів (Для самостійного вивчення)

- •7.3 Архітектура сучасних мікропроцесорів

- •7.3.1 Тенденції розвитку архітектури сучасних мікропроцесорів

- •7.3.2 Мікропроцесори Pentium

- •7.3.3 Процесори фірми amd

- •7.3.4 Продуктивність мікропроцесорів та її оцінювання

- •8 Використання сучасних мікропроцесорів

- •Список рекомендованої літератури до Частини і 1-го модуля

- •9 Програмування мікропроцесорів фірми intel

- •9.1 Сегментування пам’яті мікропроцесорами

- •9.2 Способи адресування операндів мп фірми Intel

- •9.3 Мова програмування Асемблер-86

- •9.3.1 Формат команди

- •9.3.2 Команди пересилань

- •9.3.3 Команди перетворення даних мови Асемблер-86

- •Команди логічних операцій

- •9.3.4 Команди умовних та безумовних переходів

- •9.3.5 Команди організації циклів

- •9.4 Створення програм на мові Асемблер-86

- •9.4.1 Лінійні програми

- •9.4.2 Розгалужені програми

- •9.4.3 Циклічні програми

- •10 Програмна реалізація вузлів телекомунікаційного обладнання мовою асемблер-86

- •10.1 Способи реалізації алгоритмів

- •10.2 Розробка апаратно-програмних комплексів

- •10.3 Приклади реалізації простих вузлів телекомунікацій

- •10.3.1 Ініціалізація послідовного асинхронного адаптера rs-232-c

- •10.3.2 Фрагмент програми передавання даних через асинхронний адаптер rs-232-c

- •10.3.3 Фрагмент програми приймання даних через асинхронний адаптер rs-232-c

- •10.3.4 Приклад програми ініціалізації rs-232-c та введення-виведення даних, написаної у програмному середовищі turbo assembler (tasm)

- •10.3.5 Програмна реалізація генератора імпульсних послідовностей

- •10.3.6 Програмне вимірювання періоду імпульсної послідовності det

- •10.3.7 Програмна реалізація мультиплексора

- •Список рекомендованої літератури до Частини іі 1-го модуля

- •11 Мікропроцесорні системи на універсальних мп фірми motorola

- •11.2 Побудова мпс на 16-розрядних мікропроцесорах фірми Motorola

- •11.2.1 Підсистема центрального процесорного елемента mc68000

- •11.2.2 Розподіл адресного простору мпс

- •11.2.3 Організація підсистеми пам’яті

- •11.2.4 Організація підсистеми введення-виведення

- •11.4 Побудова мпс на 32-розрядних мікропроцесорах фірми Motorola

- •11.4.1 Підсистема центрального процесорного елемента

- •11.4.2 Розподіл адресного простору мпс

- •11.4.3 Організація підсистеми пам’яті мпс

- •12 Програмування універсальних мп

- •Непряме регістрове адресування з постіндексуванням

- •Непряме регістрове адресування з преіндексуванням

- •Непряме відносне адресування з індексуванням

- •12.2 Система команд мп мс680х0 (Для самостійного вивчення)

- •12.2.1 Команди пересилань

- •12.2.2 Команди арифметичних операцій

- •12.2.3 Команди логічних операцій

- •12.2.4 Команди зсувів

- •12.2.5 Команди безумовних переходів

- •12.2.6 Команди умовних переходів

- •12.2.7 Команди організації програмних циклів

- •12.2.8 Команди звернення до підпрограм

- •12.3 Побудова програм з різною структурою мовою Асемблер

- •12.3.1 Лінійні програми

- •12.3.2 Розгалужені та циклічні програми. Підпрограми

- •Even: move sr,d5 ; Завантаження регістра стану до d5

- •12.4 Створення програмного забезпечення мпс на мп фірми Motorola

- •Список рекомендованої літератури до Частини і 2-го модуля

- •13.1 Типові мікроконтролери фірми Motorola

- •Сімейство 68нс16/916

- •13.2 Система команд мікроконтролерів фірми Motorola

- •13.3 Налаштовування вбудованих засобів мікроконтролерів

- •14 Risc-процесори фірми motorola

- •14.1 Risc-процесори PowerPc

- •14.2 Risc-процесори ColdFire

- •14.3 Система команд risc-мікропроцесорів сімейства PowerPc

- •15 Архітектура та принципи побудови процесорів цифрового оброблення сигналів

- •15.1 Основні напрямки цифрового оброблення сигналів (цос)

- •15.2 Узагальнена архітектура процесорів сімейства dsp563xx

- •15.3 Організація циклічного буфера в dsp

- •15.4 Програмна реалізація цифрового фільтра сіх

- •16Мпс на мікроконтролерах, мікропроцесорах та dsp

- •Список рекомендованої літератури до Частини іі 2-го модуля

- •Предметний покажчик

16Мпс на мікроконтролерах, мікропроцесорах та dsp

Вхідний контроль:

Яку архітектуру можуть мати багатопроцесорні системи?

Які функції має виконувати інтерфейс у багатопроцесорній системі?

Яку розрядність шини адреси можуть мати мікроконтролери фірми MotorolaMC68HC05JтаМС68НС11?

З якою метою зреалізовується клямкування адреси у МПС, якщо шина адреси/даних мікропроцесора є мультиплексована?

З якою метою в МПС використовується пріоритетний шифратор?

З якою метою в МПС використовується декодер вектора переривань?

DSPпрацюють переважно у складі багатопроцесорних систем, принаймні двопроцесорних, де другим процесором, так званимHost-процесором, може бути мікропроцесор, мікроконтролер, іншийDSPабо апаратний ПДП. Зв’язок поміжDSPтаHost-процесором зреалізовується черезHost-інтерфейс (НІ). На прикладіHost-інтерфейсуDSPсімействаDSP56000 фірмиMotorolaрозглянемо його структуру.НІ– 8-бітний повнодуплексний, з подвійною буферизацією паралельний порт, який долучується безпосередньо до шини даних Host-процесора.HI– асинхронний інтерфейс, який вміщує два банки регістрів: один, доступнийHost-процесору, і другий банк, доступний процесоруDSP.НІзабезпечує швидкість передавання пакетів 8 Мбайт/с, максимальна швидкість передавання даних при обробленні переривань становить 1,71 мільйона 24-розрядних слів/с.

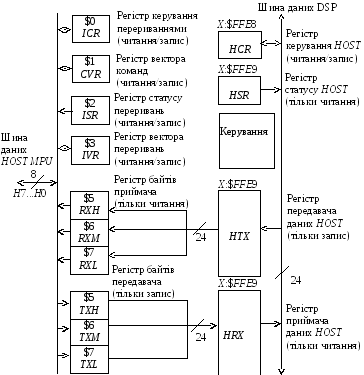

Структуру НІподано на рис. 16.1. ПроцесорDSPрозглядаєНІяк периферійний пристрій, який займає три 24-бітові слова у просторі пам’яті даних. Регістри інтерфейсу є доступні за допомогою стандартних команд процесора і способів адресування. При програмному та апаратному скиданніНІвикористовується задля стандартного введення-виведення.

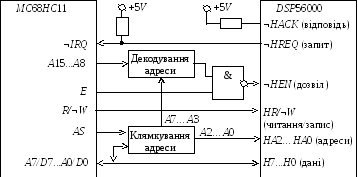

На рис. 16.2 наведено двопроцесорну систему на базі DSP56000 та мікроконтролераМС68НС11 фірмиMotorola, який має мультиплексовані шини адреси та даних і тому потребує клямкування адреси. Усі невикористовувані входи може бути підімкнено до живлення через резистор, як, наприклад,¬HAСK, задля запобігання виникнення помилкових сигналів.

Двоспрямована шина даних Н7...Н0 використовується для передавання даних поміжHost-процесором таDSP. Виходи адресиНА2...НА0 забезпечують адресне вибирання регістрівНІ, вони є стабільні, якщо вхід ¬НЕNдозволу переривань має низький активний рівень. ВхідHR/¬Wвибирає напрямок передавання даних при доступі доHost-процесора. ЯкщоHR/¬W= 1 та¬HENє активний, дані передаються зDSPдоHost-процесора; якщоHR/¬W= 0, то за активного входу ¬HENдані передаються зHost-процесора доDSP. ВхідHR/¬Wє стабільний, якщо¬HENє активний. Вхід¬HEN– дозвілHOST, дозволяє передавати дані шиною данихHOST. Якщо¬HENне є активний, лінії шини даних перебувають у третьому стані. Вихід¬HREQзабезпечує надходження відDSPдоHost-процесора, контролера ПДП або іншого зовнішнього контролера

Рисунок 16.1 – Структура НІ

сигналу запиту на переривання ¬IRQ. Вихід¬HREQможе сполучуватись з контактом запиту на перериванняHost-процесора, запитом передавання контролера або входом керування зовнішнього пристрою. Вихід¬HACK– забезпечення сигналу відповіді за операцій ПДП та сигналу відповіді – за переривання для сумісності з процесорами сімействаМС68ХХХ. У першому випадку сигнал¬HACKвикористовується для стробування даних за операцій ПДП, а у другому – для дозволу видавання на шину даних вектора переривань, якщо сигналHREQє активний.

Рисунок 16.2 – Система на базі DSPтаМC68НС11

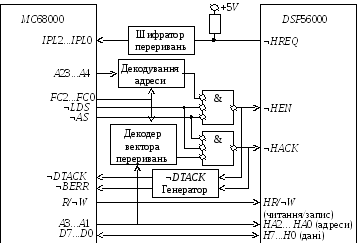

На рис. 16.3 наведено двопроцесорну систему на базі DSP56000 та процесораМС68000 фірмиMotorola. ПроцесорМС68000 може використовувати командуMOVEPзі словом, довгим словом задля передавання доDSPабо читання з нього послідовності даних. При використовуванні в якості Host-процесораМС68020 абоМС68030 у будь-якій команді може використовуватись динамічно змінюваний розмір шини.

Рисунок 16.3 – Система на базі DSP та МС68000

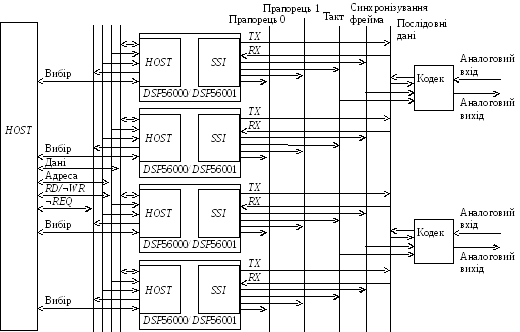

На рис. 16.4 наведено мікропроцесорну систему з чотирьох DSP, які сполучуються за допомогою одногоHost-інтерфейсу. Така МПС може виконувати до 41-го мільйона команд на секунду і може масштабуватись для підвищування продуктивності.SSIна рис. 16.4 – послідовний інтерфейс.

Контрольні питання:

Яку роль у багатопроцесорних системах відіграє мікроконтролер і яку – DSP?

Яку роль у багатопроцесорних системах відіграє мікропроцесор і яку – DSP?

За допомогою якого вузла DSPзреалізовується долучання його доHost-процесора?

Які пристрої можуть використовуватись в якості Host-процесора?

Контрольні питання підвищеної складності:

У який спосіб можуть обмінюватися інформацією процесори у багатопроцесорних системах?

У який спосіб за послідовного чи паралельного передавання даних зреалізовується обмін поміж DSPтаHost-процесором?

Чи є передавання даних через Host-інтерфейс: синхронне? асинхронне?

Рисунок 16.4 – Система на базі кількох DSP